文章目录

1. SR锁存器

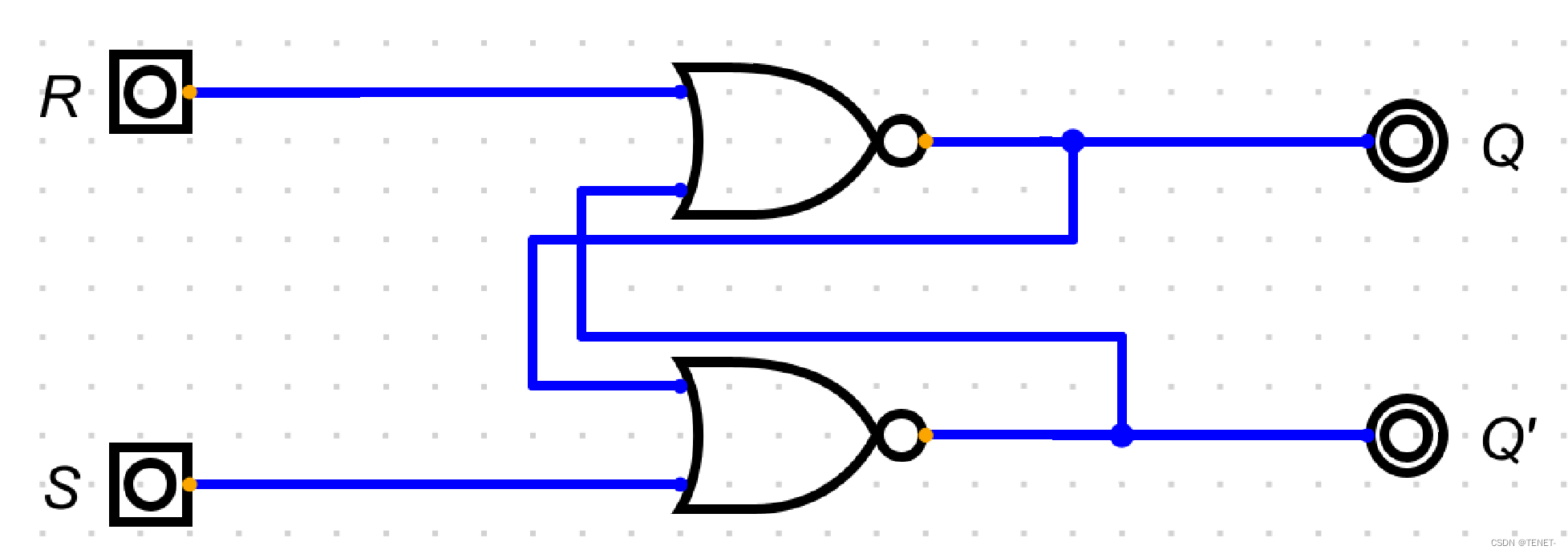

1.1 电路结构

SR锁存器(set-reset-Latch)是静态存储单元中最基本且结构最简单的一种电路。锁存器是一种双稳态电路,它可以保持一个二进制状态,直到输入信号改变。锁存器在电平触发下工作,这意味着它在输入信号为特定电平(高电平或低电平)时,响应并改变其状态。SR锁存器有两种构成方式:一种是由两个或非门构成,另一种是由两个与非门构成。尽管构成方式不同,这两种SR锁存器的功能是相同的。下面,我们将以与非门构成的SR锁存器为例进行介绍。

1.2 电路解析

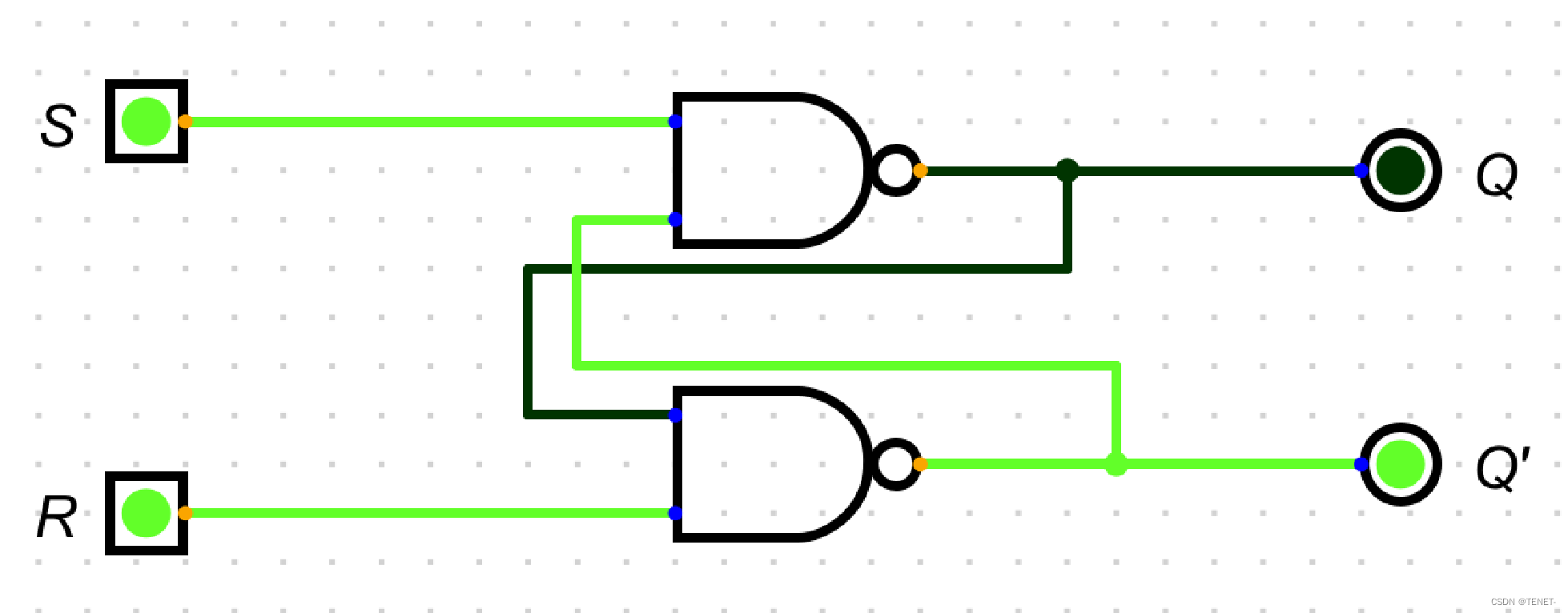

假设SR锁存器一开始的输入S、R 都为高电平(1),此时输出端Q和Q`的电平是无法确定的。这个状态为初始状态。

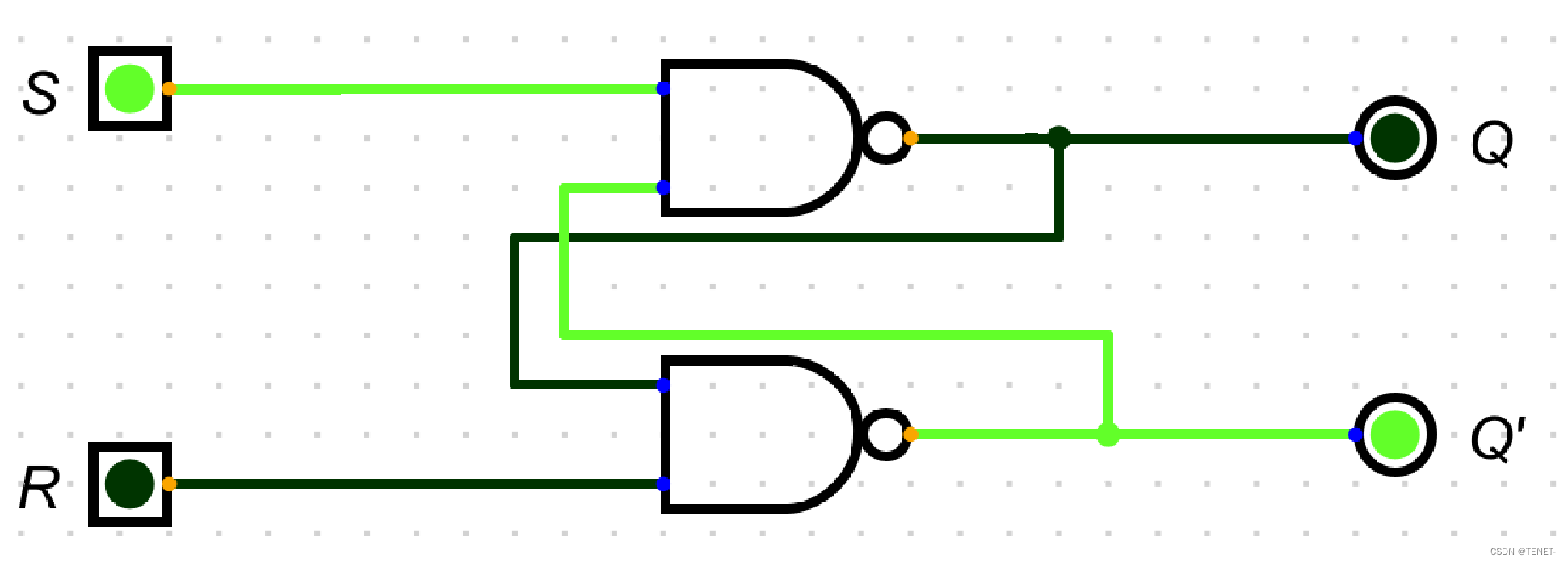

此时如果S的输入由1变为0,无论Q‘的电平是高或低,经过S(0)与非的计算,Q的电平都会变为1。

Q'的电平经过Q和R的与非计算会变为0. 并且无论S的电平变为什么,输出Q和Q'都会被锁定,不会发生变化。这个过程为置位(set)。

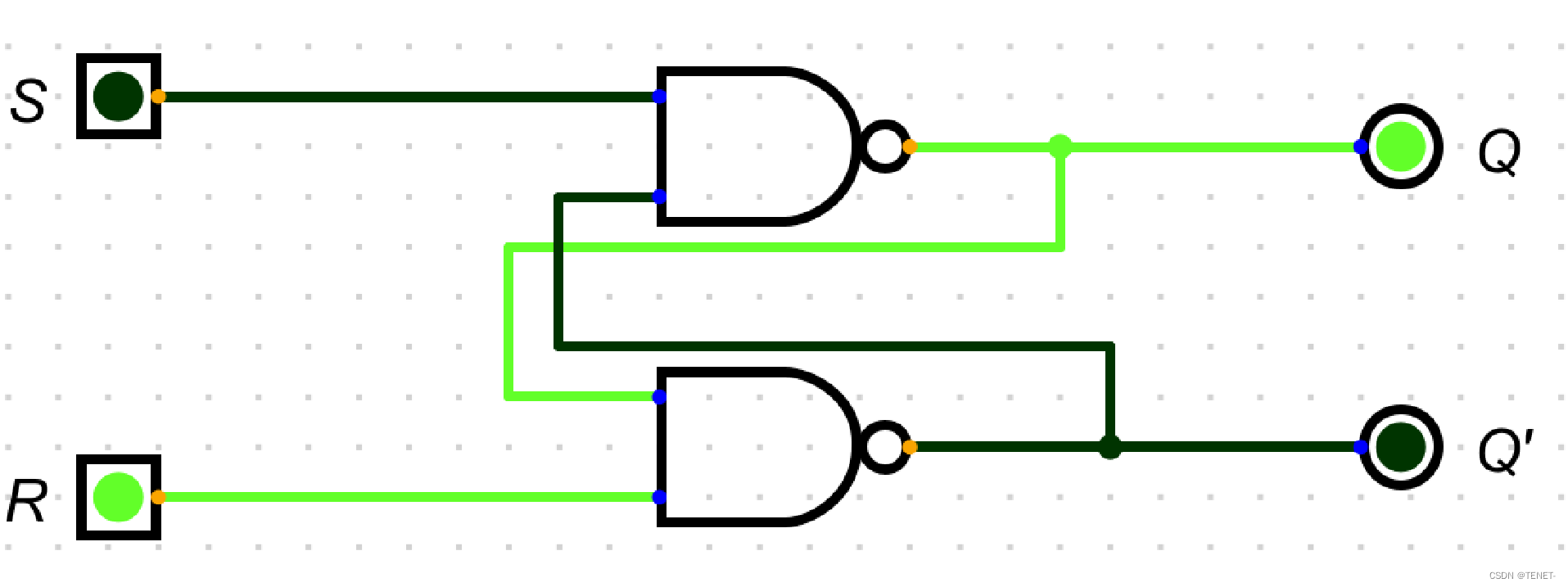

将S重新置为1,接下来将R置为0,此时经过与非计算,Q’会变为1.Q会变为0。这个过程为复位(reset)。

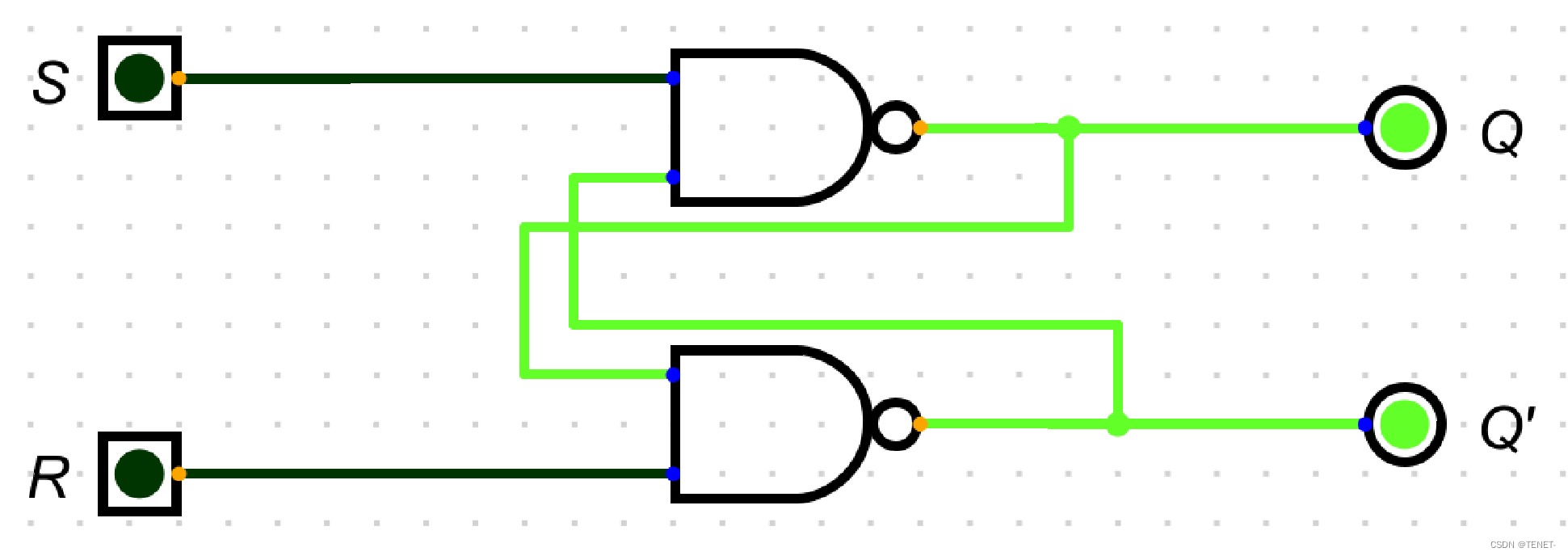

如果S和R同时为0,经过计算,Q和Q'会同时为1。但是这种情况是不允许的,因为SR寄存器要求输出的Q和Q‘永远相反。

总结:

- 当S`为1,R`为1, Q和Q`状态不变;

- 当S`为0,R`为1, Q=1、Q`=0;(置位)

- 当S`为1,R`为0, Q=0、Q`=1;(复位)

- 当S`为0,R`为0,电路无意义

| S`输入 | R`输入 | Q输出 | Q`输出 |

| 1 | 1 | 维持不变 | 维持不变 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 0 | 0 | 1(无意义) | 1(无意义) |

如果是用或非门来组成锁存器,输入输出反过来。

如果是用或非门来组成锁存器,输入输出反过来。

- 当S`为0,R`为0, Q和Q`状态不变;

- 当S`为1,R`为0, Q=1、Q`=0;(置位)

- 当S`为0,R`为1, Q=0、Q`=1;(复位)

- 当S`为1,R`为1,电路无意义

| S`输入 | R`输入 | Q输出 | Q`输出 |

| 0 | 0 | 维持不变 | 维持不变 |

| 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 1 | 1(无意义) | 1(无意义) |

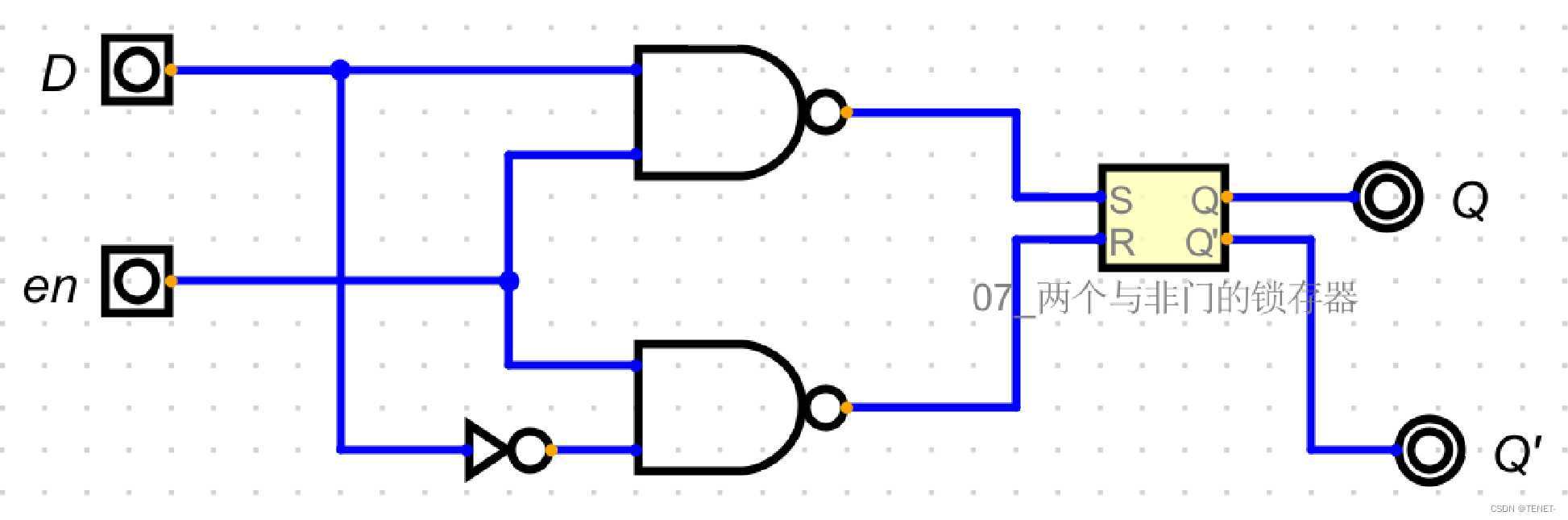

2. 带en输入的SR锁存器

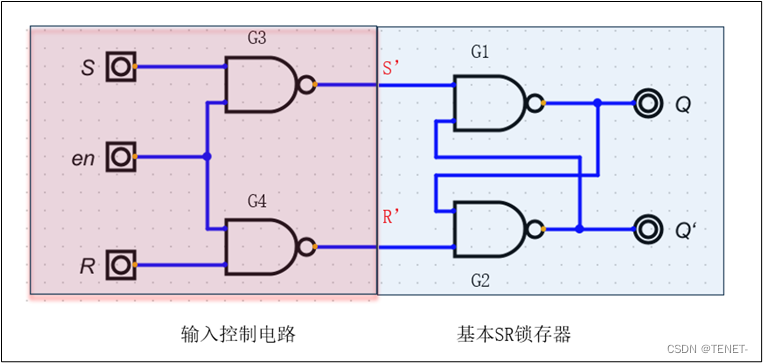

2.1 电路结构

上面的SR锁存器尽管可以锁住输出状态,但是没法控制设置输出的时机。所以需要给这个电路加上一些其他组件,在锁存器的基础上,增加一个触发信号输入端。

在这部分电路中,SR锁存器增加了一个使能(enable)输入信号en,这样可以更灵活地控制锁存器的状态。电路分为两个部分:输入控制电路和基本SR锁存器。

-

输入控制电路:

- 由两个与非门(G3和G4)构成。

- 输入信号包括S、R和en。

- 通过en信号控制,决定何时将S和R信号传递给基本SR锁存器部分。

-

基本SR锁存器:

- 由两个与非门(G1和G2)构成。

- S

和R信号由输入控制电路提供。

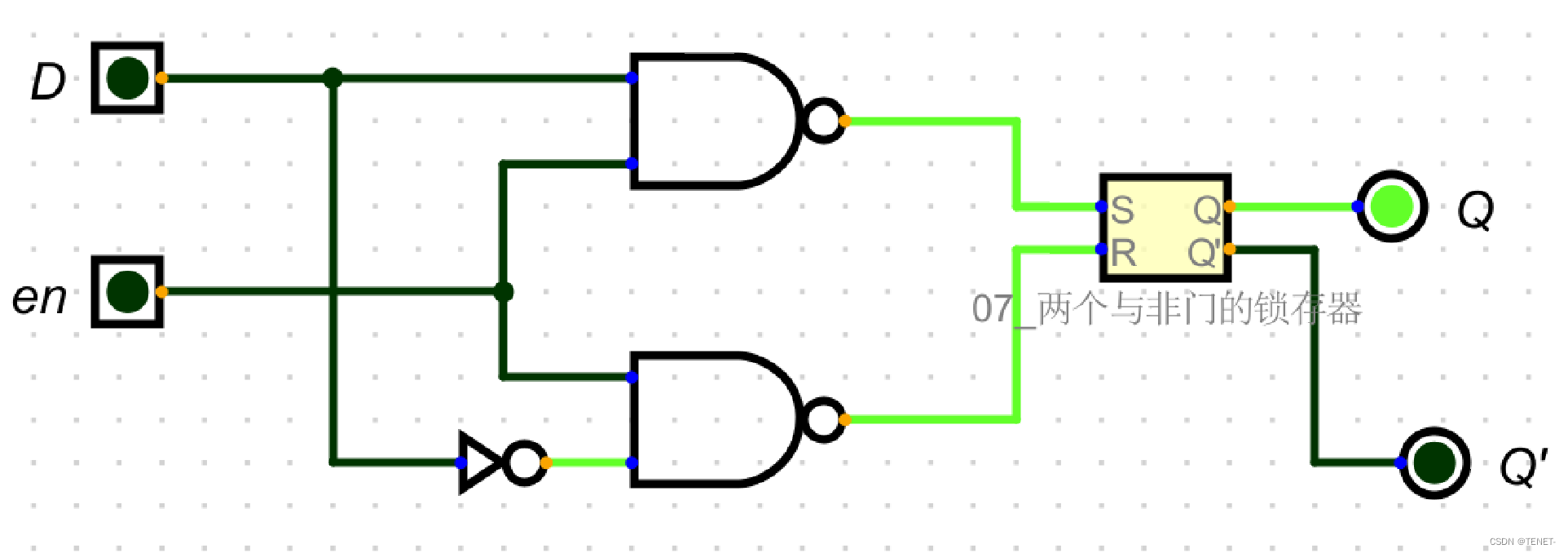

2.2 工作原理

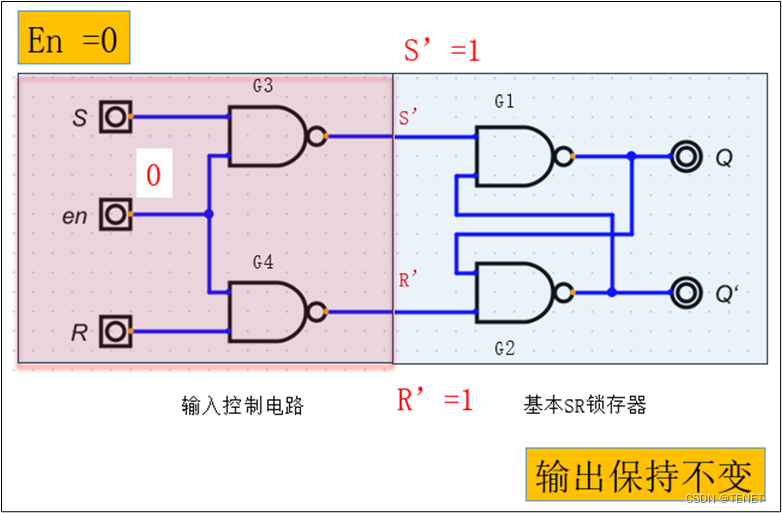

En = 0时,输出保持不变

与非门的输出为高电平(1),除非两个输入均为高电平(1)时输出才为低电平(0)。

当使能信号En为0时,输入控制电路的输出S'和R'都为高电平(1),这会导致基本SR锁存器的状态保持不变。因此,无论输入S和R如何变化,锁存器的输出Q和Q'都不会改变。

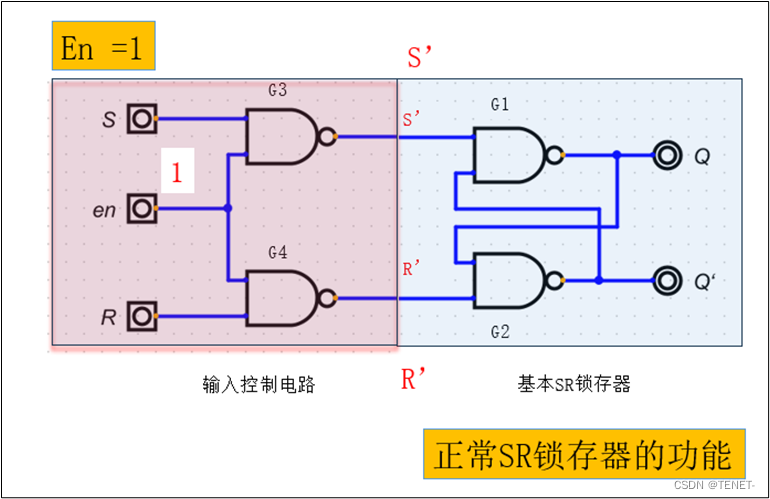

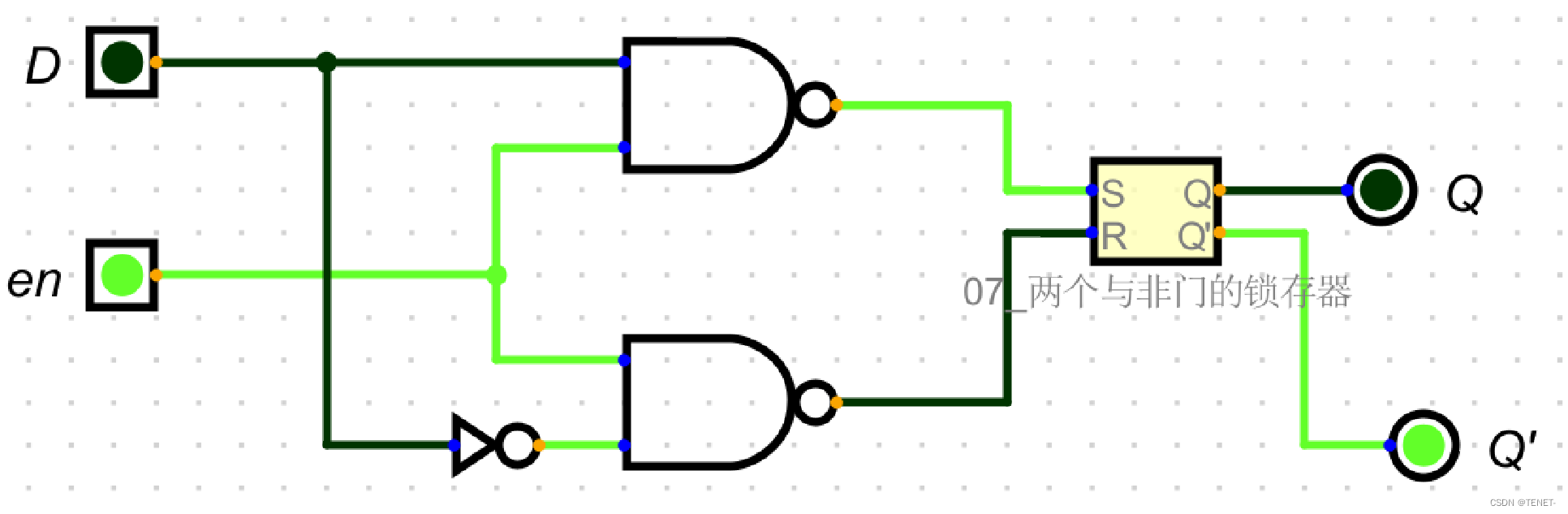

En = 1 时,正常 SR 锁存器的功能

当使能信号En为1时,输入控制电路的输出S'和R'分别为输入S和R的反相,这将使基本SR锁存器按照正常的SR锁存器功能工作。

3. 带En输入的D锁存器

3.1 电路结构

从刚才的电路可以看出,当en为1时,如果想将Q设为1,此时S应为1,R应为0;反之,如果想将Q设置为0,S应为0,R应为1。由此可得到,SR恰好为反相输入时,可以顺利的设置Q,所以对电路稍加改造,将S改名为D,并将其反相输入到R,如图,就得到了一个带en输入的D锁存器,其特性为:当en为高电平,Q和D的输入保持一致;当en为低电平,Q保持之前状态不变,从而起到存储作用。

3.2 工作原理

En = 0时,输出保持不变,不受D输入的影响。

En = 1 时,正常 SR 锁存器的功能, 输出Q的值与D输入的值相同。

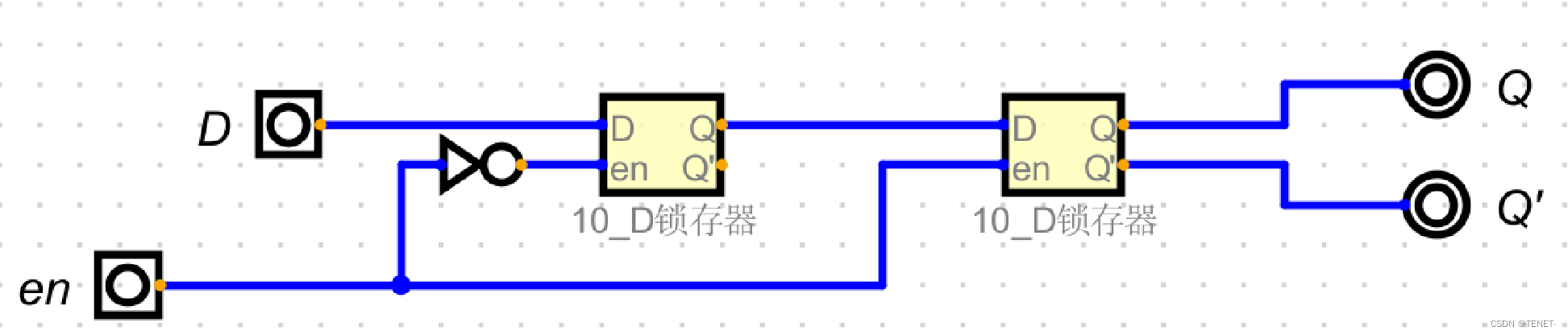

4. 边沿触发的D触发器

4.1 电路结构

对于刚才的带En输入的D锁存器,当En为1时,D的输入直接影响Q的输出。为了提高锁存器的可靠性、增强抗干扰能力,希望锁存器的状态仅仅取决于En的下降沿(或上升沿)到来的时候的输入信号状态。

解决方案:D触发器可以解决以上问题。

D触发器在时钟信号的控制下,仅在时钟信号的边沿(上升沿或下降沿)到来时更新输出,这样可以避免输入信号的毛刺和噪声对输出的影响,提高系统的稳定性和可靠性。触发器是一种时序逻辑电路,它在时钟信号的边沿(上升沿或下降沿)触发下工作。触发器每次在时钟信号的有效边沿时,采样输入信号并改变其状态。

电路图中包含两个D锁存器,分别有D、C和Q三个主要信号。

- D:数据输入信号。

- C:时钟信号。

- Q:输出信号。

4.2 工作原理

边沿触发的D触发器在时钟信号的边沿(上升沿或下降沿)到来时才会更新输出Q。这与使能信号控制的D锁存器不同,后者在使能信号为高电平时持续传递输入数据到输出。

- 时钟信号C:当时钟信号C为高电平或低电平变化时(取决于电路设计是上升沿触发还是下降沿触发),触发器才会根据输入D的状态更新输出Q。

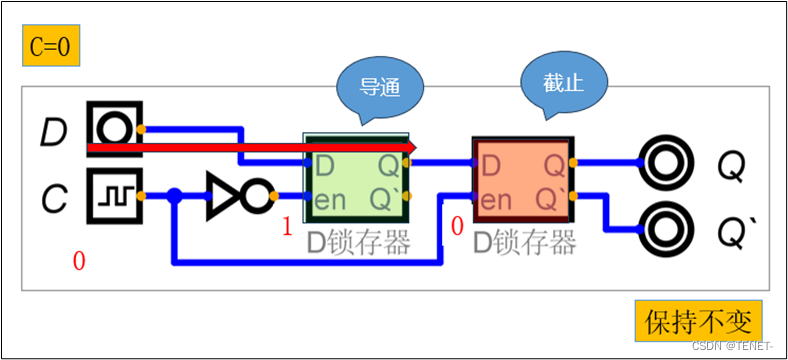

当时钟信号C=0时,电路如图所示:

- C=0:时钟信号为低电平。

- 输入信号:D信号通过反相器和两个D锁存器的传输。

状态分析:

-

第一个D锁存器(左侧):

- En = 1(因为C被反相)。

- 输入D信号通过第一个D锁存器直接传递给其输出。

- 如果D=0,则第一个D锁存器的输出Q = 0;如果D=1,则第一个D锁存器的输出Q = 1。

-

第二个D锁存器(右侧):

- En = 0(直接受C控制)。

- 第二个D锁存器处于阻止状态,其输出保持不变,Q和Q'保持之前的值。

因此,当C=0时,D信号通过第一个D锁存器传递,但不影响最终的Q输出。Q保持不变。

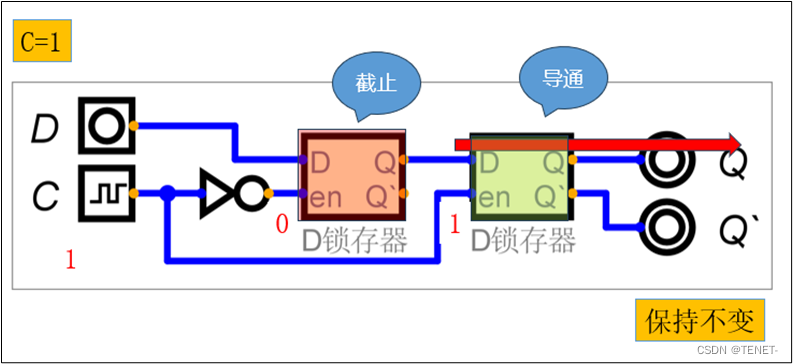

当时钟信号C=1时,电路如图所示:

- C=1:时钟信号为高电平。

- 输入信号:D信号通过反相器和两个D锁存器的传输。

状态分析:

-

第一个D锁存器(左侧):

- En = 0(因为C被反相)。

- 第一个D锁存器处于阻止状态,其输出保持不变,Q保持之前的值。

-

第二个D锁存器(右侧):

- En = 1(直接受C控制)。

- 第二个D锁存器根据第一个D锁存器的输出更新其输出。

- 如果第一个D锁存器的输出Q = 0,则第二个D锁存器的输出Q = 0;如果第一个D锁存器的输出Q = 1,则第二个D锁存器的输出Q = 1。

因此,当C=1时,D信号通过第一个D锁存器保持,但第二个D锁存器根据第一个D锁存器的输出更新其状态,Q输出更新为D的值。

C信号不论是高电平还是低电平,Q都不会随D变化;只有当C信号由0变1的一瞬间,D的值能够传递到Q。这个电路称为上升沿触发的D触发器。

7706

7706

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?