一、DC控制器

1、TLV62569(不需自举电容)

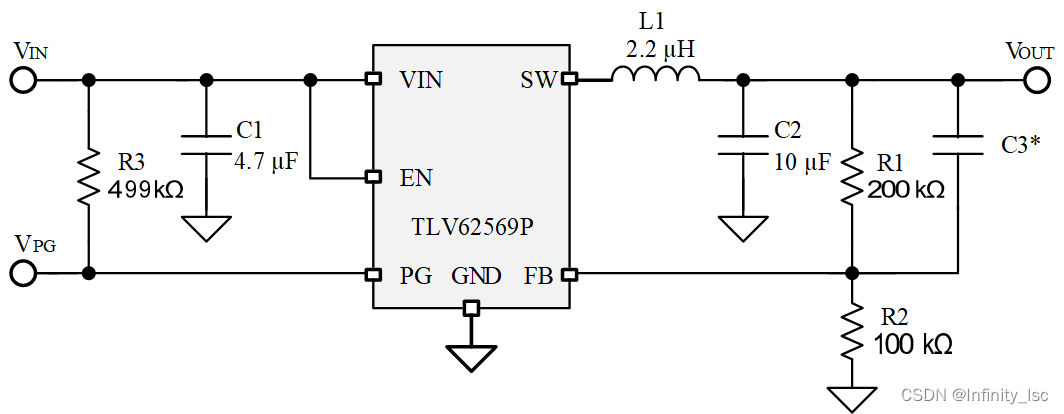

TLV62569数据手册中,典型应用电路如下所示:

2、MT2492(需要自举电容)

MT2492数据手册中,典型应用电路如下所示:其中 C2 为自举电容

二、内部结构

1、TLV62569 结构

TLV62569 内部框图如下图所示:

由上图可知,TLV62569 输出上管为 PMOS,下管为NMOS,Modulator 通过调节 PWM 占空比,控制上/下管 MOS 交替导通,满足不同负载需求。

当 Gate Drive 输出高电平时,上管 PMOS 截止,下管 NMOS 导通;

当 Gate Drive 输出低电平时,上管 PMOS 导通,下管 NMOS 截止。

2、MT2492 结构

MT2492 内部结构框图如下图所示:

由上图可知,MT2492 输出上管、下管均为 NMOS,上下管 NMOS 各由一个 Gate Drive 驱动,通过 Control Logic 控制交替导通。

由于下管 NMOS的 源极(S)接地(GND),当 Gate Drive 输出高电平时,下管 NMOS 可持续导通;

由于上管 NMOS的源极(S)接下管 NMOS 的漏极(D),故当 Gate Drive 输出高电平时,因为此时下管 NMOS 为关断状态,若不加自举电容 C2,上管 NMOS 导通后,漏-源之间压差 ,即

,无法满足

的导通条件,故无法实现持续导通,可参考:MOSFET(一):基础

![]() https://blog.csdn.net/VampireWolf/article/details/108442956 故须在上管 NMOS 的栅-源(G-S)之间添加自举电容 C2,VCC 通过 Boot Charge 给电容 C2 充电,抬高上管 NMOS的栅极电压,使得上管 NMOS 的栅-源之间存在电压差

https://blog.csdn.net/VampireWolf/article/details/108442956 故须在上管 NMOS 的栅-源(G-S)之间添加自举电容 C2,VCC 通过 Boot Charge 给电容 C2 充电,抬高上管 NMOS的栅极电压,使得上管 NMOS 的栅-源之间存在电压差 ,保证

,实现持续导通。

3、两者区别

虽然 PMOS 用作高边驱动比较方便 ,但在相同工艺、尺寸等条件下,PMOS 的导通电阻比 NMOS 大,导致 PMOS 导通损耗比NMOS 要大,因此在高边驱动中,通常还是会使用NMOS

自举仿真电路如下图所示:

4448

4448

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?