说在开头:关于大一统理论(3)

第一次超弦革命爆发了,整个物理学界忽然像着了魔一样,投入了极大的热情,成百上千人投入这一领域,在第一波运动之后,我们得到了这样一个图像:任何粒子其实都不是传统意义上的点,而是开放或则闭合的弦;当他们以不同方式振动时,就分别对应自然界中的不同粒子(电子,光子等等);我们生活在一个10维空间里,但是其中的6维是紧紧蜷缩起来的,所以我们觉察不到。如果我们将时空放大到“普朗克空间”的尺度上(10⁻³³cm),这时候我们就会发现:原本当做时空中的一个“点”,其实是一个6维的小球。那人们自然要问,为什么有6个维度是蜷缩起来的呢?这些维度有什么不同么?有没有办法证明?但是弦的尺度是如此之小,所以没有什么手段能够去直接认识/测量它,而当第一次革命的热情过后,筛除掉大量的超弦理论,仍然还有5种理论被保留了下来,而且每一种都能自圆其说,那这5种理论究竟谁是正确的呢?人们对弦论的热情很快就消退了,第一次革命尘埃落定。

到了90年代中期,爱德华.威腾在1995年的超弦年会上,证明了不同耦合常数的弦论在本质上其实是相同的;就是说这5种弦论虽然看起来相当不同,其实它们是一个大统一理论的不同变种。而当耦合常数被放大时,就出现了一个新的维度:第11维。弦不只是1维的,而是2维的。超弦理论终于从沉睡中苏醒了过来,完成了绝地反击。

这5种超弦理论就像盲人摸象一样,只摸到了大象的鼻子、脑袋、大腿、耳朵、尾巴,虽然它们摸起来完全不同,但其实都来自同一头大象。物理学家们终于可以松一口气,这个统一的理论就被称为了“M理论”。这个M表示什么意思,大家众说纷纭(中国人认为是摸理论,盲人摸象的摸)。

不管是超弦理论还是M理论,它们都还刚刚起步,但是M理论仍然取得了一定的成功,解释了黑洞熵的问题。甚至霍金在《大设计》一书中,直接将M理论称作宇宙的终极理论。不过对于物理学界来说,人们对M理论的热情并没有持续高涨,如今第二次超弦革命也已经硝烟散尽,超弦又进入了一个蛰伏期。M理论是否最终能够完成物理学的统一,现在还无法预言。(参考自:曹天元-上帝掷骰子吗)

3,高速信号传输实现

正如我们在《从频域出发理解信号》和上面章节的分析,高速信号的频谱是相当宽的,其最高频率分量取决于信号边沿时间;但一般情况下信号速率越高,则边沿时间越短(陡),从而信号的带宽越宽。那么带宽更宽或则说频率分量高,会给我们带来什么问题呢?

1. PCB板材FR-4的介电常数εr与信号的频率有关,一般随频率的增加介电常数εr减小,所以信号的高频分量传输的更快(先到达接收端);而PCB板材本身不是理想的(不均匀),传输线不是理想的(有过孔,走线宽度会变化,经过连接器等),存在各种阻抗不连续点,产生不同频率分量信号多次反射、叠加,会严重改变信号波形(出现过冲或振荡);

——具体原理及详细分析,胖友们请复习《信号完整性基础》相关内容。

2. 信号高频分量的PCB介电损耗更大,即,传输线对信号的高频分量衰减更大;最直观的表现是:原始信号里的高频分量被削弱或滤掉,在波形上看来就是边沿变缓。

——具体原理及详细分析,胖友们请复习《信号完整性基础》相关内容。

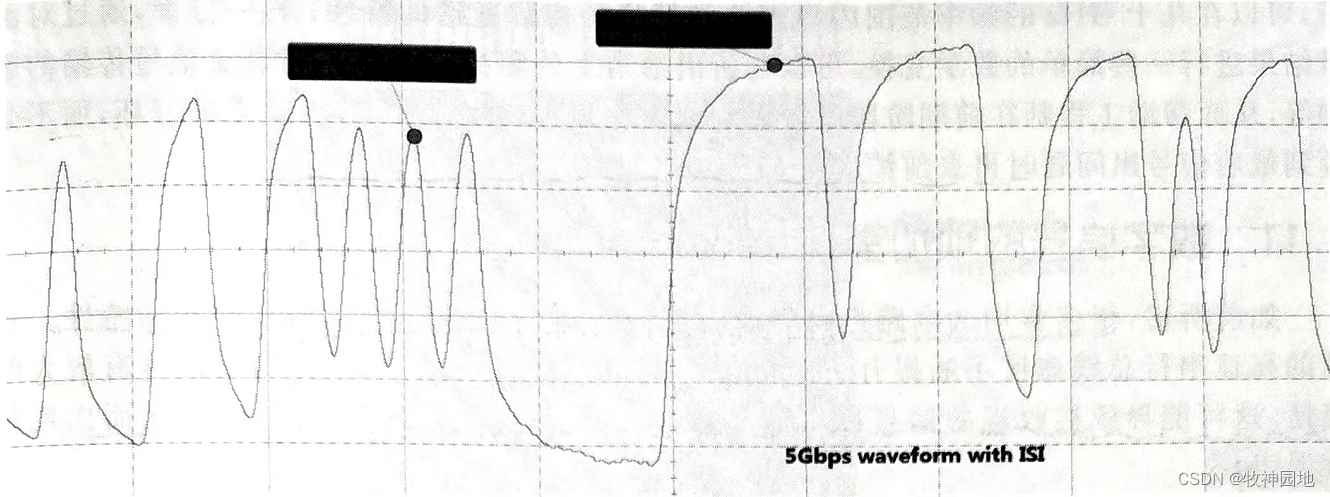

3. 信号的幅度衰减、上升/下降沿时间的改变、传输时延的改变等很多因素都与频率分量相关,不同频率分量受到的影响是不一样的;而不同的数据产生不同的频率分量(举个栗子:1010和1100代表不一样的频率分量),所以不同数字码流在传输线中受到的影响不一样,这就是码间干扰ISI(Intersymbol interference),如下图所示;

好,这样出现的结果是:常用的FR-4 PCB板材或电缆在高频时呈现高损耗的特性,并随着信号频率的不断提升,使得目前流行的板材达到极限而对信号有较大的损耗,这将导致接收端的信号非常恶劣,以至于无法正确还原和解码信号,从而出现传输误码。

我们有两种方案来解决这个问题:1,采用昂贵的PCB板材,减少高频信号的损耗;2,采用某种技术来补偿传输通道的损耗。由于低损耗PCB板材和电缆的成本太高,通产都会采用相应的信号补偿技术:预加重(Pre-emphasis)/去加重(De-emphasis)和均衡(Equalization)。一般来说,典型高速数字传输通道结构如下图所示。

3.1 预加重(Pre-emphasis)和去加重(De-emphasis)

预加重和去加重技术使用在信号的发送端;

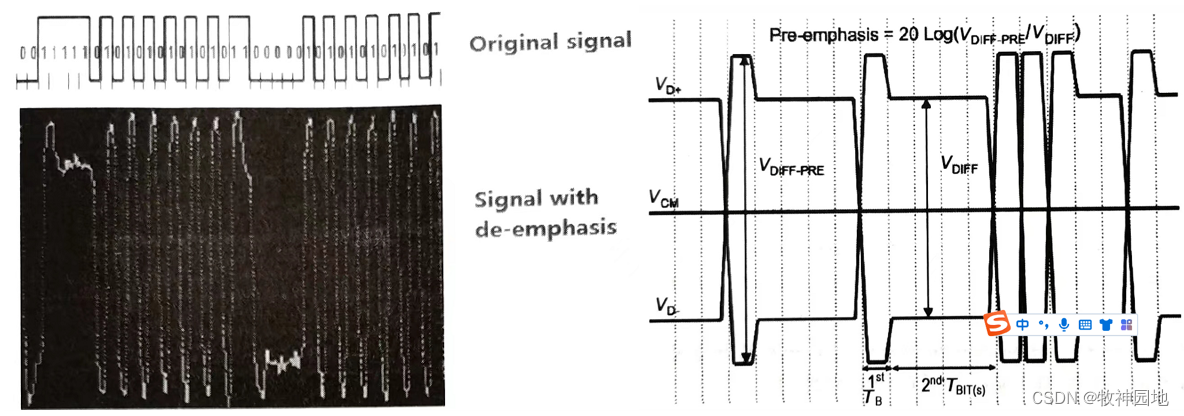

预加重技术是:通过预先对信号的高频分量进行增强,来补偿传输通道损耗的方法;如下图所示,这种方法通过增大信号跳变边沿后第一个bit的幅度(预加重)来完成的,做完预加重后序列里的第一个bit的幅度会比第二个和第三个bit的幅度要大(如下右图所示)。由于跳变bit代表了信号里的高频分量,所以这种方法实际上就是提高了发送信号里的高频信号的能量。

——其技术实现简单,所以有很多串行总线上都使用了(举个栗子:PCIe,SATA,USB3.0等)。

预加重技术对信号改善的效果取决于其预加重幅度的大小,如上右图所示为预加重幅度的定义:经过预加重后跳变bit幅度相对于非跳变bit幅度的增益(dB)。举个栗子,预加重为6dB,在发送端来看就是跳变bit的电压幅度是非跳变bit电压幅度的2倍。

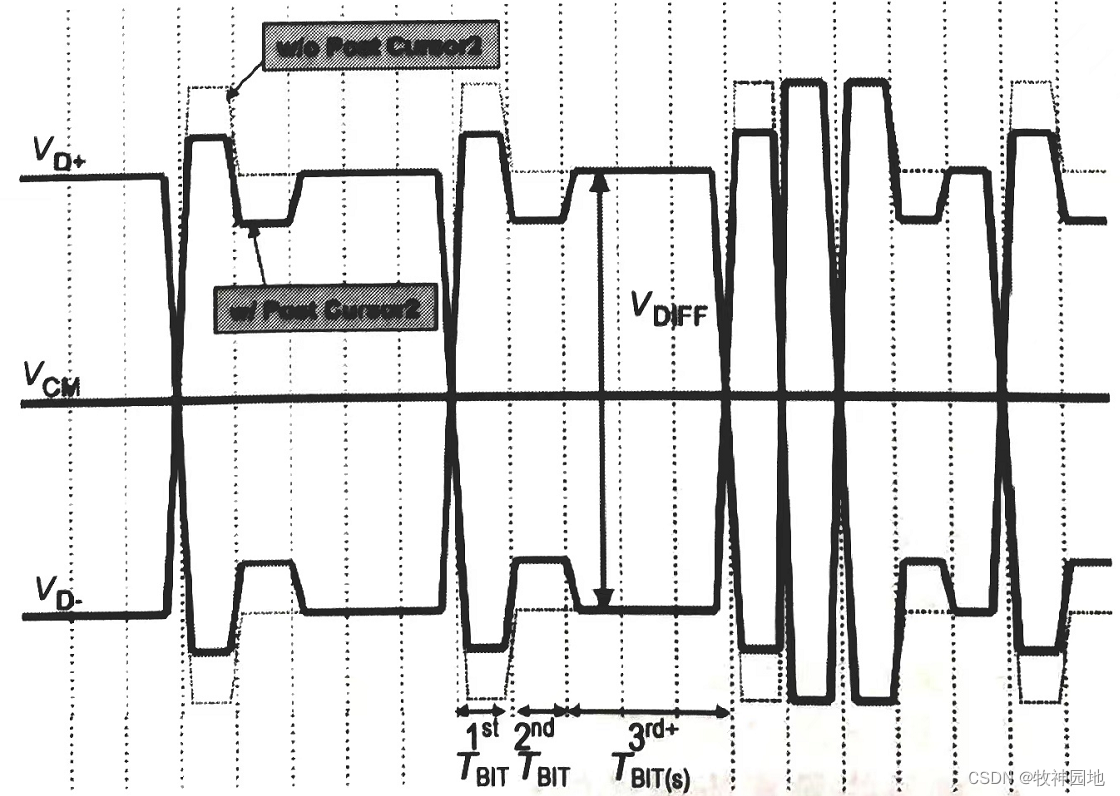

但是简单的预加重对信号的频谱改善并不是完美的,其频率响应曲线与实际传输线损耗曲线可能不相匹配(没有完美补偿传输线损耗),所以高速率的串行总线会采用更高阶数、更复杂的预加重处理,在跳变后的第二个bit的幅度也会有变化。跳变沿后的第一个bit幅度的变化称为:Post Cursor,跳变后的第二个bit的幅度变化称为:Post Cursor2。如下图所示。

由于预加重电路在实现的时候需要相应的放大电路来增加跳变bit的幅度,电路比较复杂而且增加了系统功耗,所以在实际应用中更多采用了去加重的方式(De-emphasis);去加重技术不是增大跳变bit的幅度,而是减小非跳变bit的幅度,从而得到和预加重类似的信号波形。

如下图所示。去加重通过压缩信号的直流和低频分量(连续0或1的bit流),从而改善其在传输过程中可能造成的对高频分量(短0或1的bit流)的影响。所以去加重的比例越大,信号直流电平被压缩的越厉害,因此去加重的幅度在实际应用中一般很少超过-9.5dB。

——去加重后,虽然高频分量还是有在正常的衰减,但是低频分量在发送端认为衰减的更多,从而达到接收端时高频分量和低频分量的比例保持了原始信号(只是整体幅度下降了),所以在接收端是一个更好的信号波形(虽然幅度减小了,但是“眼睛”睁的更开了:眼高增加)。

在经过预加重或去加重之后的信号,直接测量信号的发送端(Tx),它并不是一个理想的眼图(波形),但在接收端(Rx)看来(如果预加重/去加重的设置同传输线损耗相匹配)还是很不错的;这是因为在发送端通过预加重增强的高频分量,在经过PCB走线或电缆之后,高频分量会被衰减:跳变bit的幅度衰减会比非跳变bit大很多;所以在接收端看不到发送端的那种效果。因此从本质上来说预加重或去加重属于一种信号的预失真技术(为了实现在接收端信号的少失真)。

在实际应用中,高速数字电路需根据实际走线的长短调整预加重或去加重的幅度,从而在接收端得到最好的眼图效果。但当数据速率更高时,传输通道的损耗更加严重,仅靠发送端的预加重/去加重已经不大够用,所以还会在接收端采用复杂的均衡技术。

3.2 均衡(Equalization)

如上所述当随着数据传输速率的进一步更高,就需要在接收端同时使用均衡技术来改善信号质量,所谓均衡是指:在数字信号的接收端进行的一种补偿高频损耗的技术。常见的信号均衡技术有3种:CTLE(Continuous Time Linear equalization),FFE(Feed Forward Equalization)和DFE(Decision Feedbak equalization)。

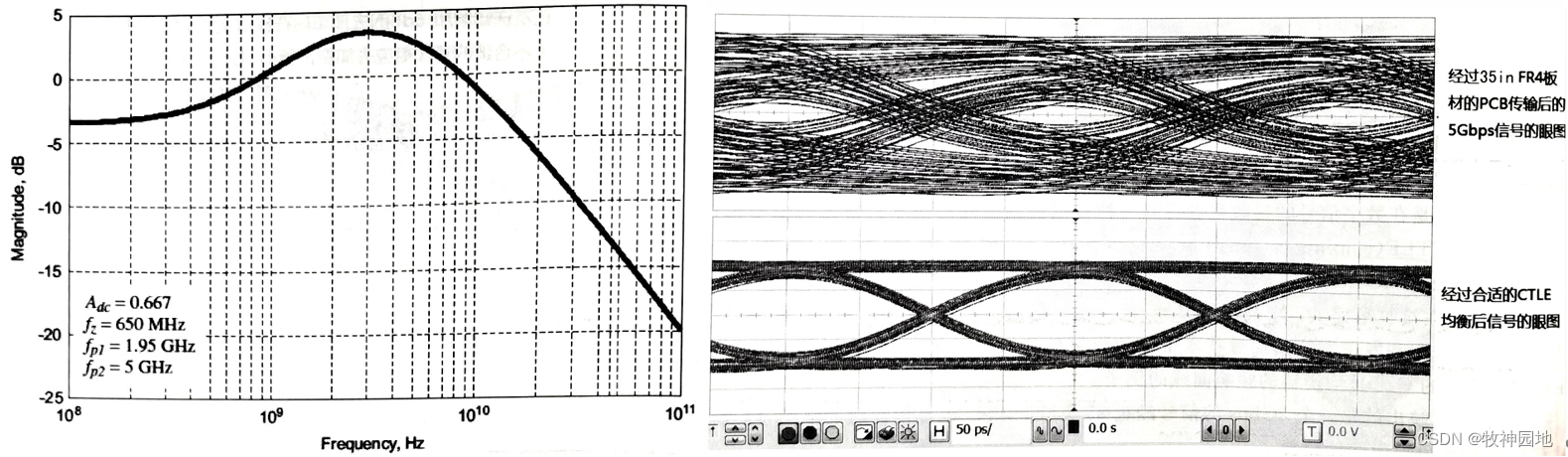

1. CTLE是在接收端提供了一个高通滤波器,可以对信号中的主要高频分量进行放大;所以它的效果和发送端的预加重技术所带来的效果是类似的;

——如下图左图所示为USB3.0采用CTLE技术,在高频段对信号有补偿(放大),如下右图所示为CTLE技术后的实际效果。

2. FFE是对当前bit位置和其前面两个bit位置的电压进行加权矫正,然后累加获得波形中当前bit位置的矫正(均衡)后的电压电平;如下图所示为通过FFE均衡后对信号的改善效果;

3. CTLE和FFE都是线性均衡技术,而DFE是非线性均衡技术,是指:通过相邻bit的判决电平对当前bit的判决阈值进行修正;设计合理的DFE可以有效补偿码间干扰(ISI)对于信号造成的影响。

1, DFE计算出一个校正值,然后将其添加到逻辑判决阈值中(改变的是阈值电压,而非信号本身),因此DFE改变当前bit的判决阈值(增大或降低),并根据这个新的均衡阈值电平对波形重新执行逻辑判决;

——V(k) = C1*S(k-1) +C2*S(k-2);其中V(k)是校正后的电压阈值;S(k-n)是位于bit位置k之前n个bit处的逻辑值;Cn是位于bit位置之前n个bit处的矫正系数(抽头系数)。

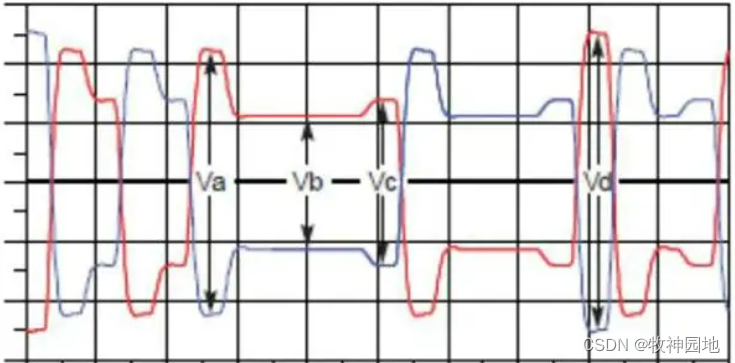

2, 对于两抽头DFE来说,需要先确定当前bit位置之前两个bit的逻辑状态值,随后算法将用其bit逻辑值乘以响应的抽头系数,最后累加起来得出当前bit的判决阈值偏移量。

4. DFE均衡器芯片相比于CTLE和FFE的均衡器芯片更加复杂,所需的门电路更多,因此大多数情况下一般优先选择CTLE或FFE的均衡方式,但在更加复杂和高速的情况下,会先用CTLE或FFE来将眼图打开,然后再用DFE进一步优化。

——在非常高速和长距离的信号传输中,通常首先使用预加重技术来提升高频分量,在经过通道损耗达到接收端后,再通过均衡技术实现长距离(>50cm)和高速(>10Gbps)的信号传输。

3.3 高速信号抖动(Jitter)

抖动是高速数字信号的关键概念,它反映的是数字信号偏离其理想位置的时间偏差;所以抖动实际上是时间上的噪声,其时间偏差的变化频率可能比较快或比较慢。通常我们定义超过10Hz以上的抖动成分称为Jitter(抖动),而变化频率低于10Hz的抖动成分称为Wander(漂移)。

Wander(漂移)一般反映的是时钟源随着时间、温度等的缓慢变化,影响的是时钟的绝对精度,一般在通信过程中,收发双方时钟会采用一定的架构进行分配和同步,所以缓慢的时钟变化很容易被锁定,因此Wander对串行高速信号传输的影响不大;而主要关心高频的Jitter。

由于信号边沿时间的偏差可能由各种因素造成的,有随机噪声和确定性的干扰;所以对于这个时间偏差通常不是一个恒定值,而是一个统计分布(正态分布),在不同应用场合可能使用有效值(RMS)衡量,也可能使用峰峰值(Peak-to-Peak)衡量,更复杂的场合还需要对该时间偏差各个成分进行分解和估计。

1. 抖动的衡量方法:不同的衡量方法,得到的抖动测量结果是不同的,如下为几种常用抖动测量方法;

1, 周期抖动(Period Jitter):对于时钟信号,我们最关心其周期是否等间隔;在理想情况下的时钟,每个周期长度都是一样的,但信号有抖动则会导致周期发生变化;所以对于时钟信号来说,我们对时钟的多个周期进行测量和统计,得到信号周期的平均值,峰峰值,RMS值等;

2, 周期到周期抖动(Cycle to Cycle Jitter):是对时钟信号相邻的两个周期相减,反映了时钟信号周期变化的快慢;对同步数字逻辑电路来说,如果时钟信号的周期变化非常缓慢,那么即使变化范围很大也不会产生误码,但如果周期的变化很快则可能造成电路故障;

3, 时间间隔误差抖动(Time Interval Error):指的是被测信号边沿相对于其参考时钟有效边沿的抖动;对于串行总线来说,其时钟信号不是特定的通道,无法进行周期抖动的测量,因此使用的就是TIE抖动的测量方法;这是一个相对位置的测量。

——对于同一个信号,用不同的测量方式可以得到不同的结果;如下图所示。

3.4 扩频时钟(SSC)

数字电路中不希望有抖动,但如果时钟太精确也会导致EMI辐射过大(关于EMI部分,后续《电磁兼容性基础》详细介绍),所以有时需要在时钟信号上引入一些抖动:SSC(Spread Spectrum Clock),扩频时钟。

——这让人看的云里雾里:一会不要抖动、一会又要引入抖动,这TM啥玩意儿。事实上在电路设计中不存在绝对的标准(相信其它事情也是如此),我们的目标/需求不同,就会有不同的设计。

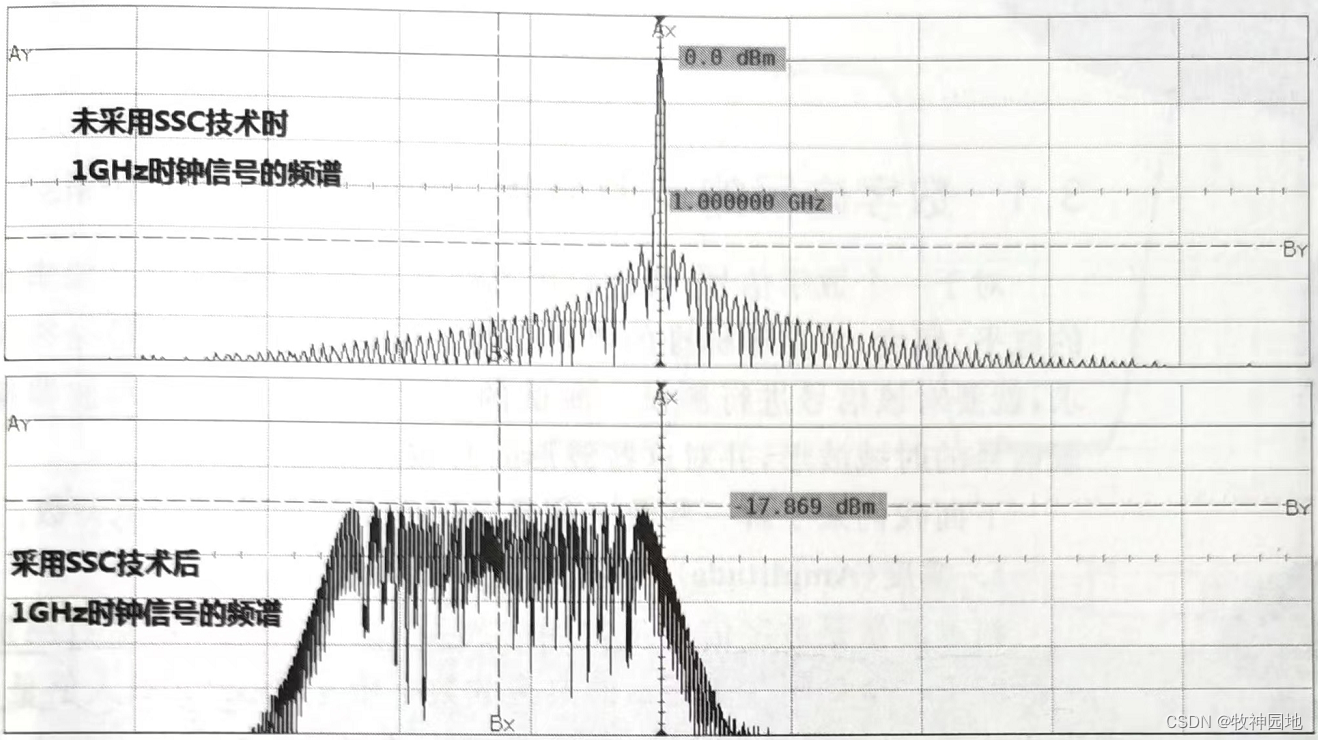

SSC扩频时钟是在数字系统的时钟源头进行轻微的调频,从而降低EMI辐射的峰值功率,扩频时钟的方法实现简单且成本较低,只要在时钟源上进行扩频则后级所有的数字信号上就都带上了扩频,因此在消费类产品(屏蔽方案成本较高,设计复杂)的高速数字总线上普遍使用。SSC扩频时钟后的EMI辐射能量频域变化如下图所示,在采用SSC技术后可以大大减小系统EMI辐射的峰值;同时需要考虑一下几个因素对数字系统的影响。

1. SSC调制深度:调制深度指对信号进行调频是被调制信号的频率变化范围;调制深度过浅,则对辐射的改善情况有限,过深则时钟频率被拉偏较多,对系统中的晶振、PLL要求过高;

——SSC调制深度一般在工作频率的0.1%~1%左右。

2. SSC的调试频率:反映的是被调制信号频率变化的快慢;如果调制频率太快,后级PLL电路可能跟踪不上,而调制频率太慢,则可能产生一些额外音频噪声;

——典型SSC的调制频率在30~33KHz。

3. SSC的调制波形:指被调制信号的频率随时间的变化波形,一般可以是:正弦波,锯齿波或三角波;三角波的调制方式由于实现简单,调制后信号的频谱接近均匀分布,因此很多总线扩频时钟采用三角波的调制波形。

写在最后

本章用了很大的篇幅讲了总线的基本概念和数字信号基础,数字信号基础是对上一专题《电平设计基础》的进一步深入,同时也是总线知识的基础,起到承上启下的作用(艾玛,终于把这章内容给圆过来了~)。总线是一个综合性的硬件技术知识应用:最底层的硬件技术知识(信号完整性)的应用和人为规范定义,是一套复杂的逻辑体系。但越复杂的东西就越容易出现漏洞(异常情况),同时又要增加更加复杂的机制来“补漏”,造成整个系统更加复杂;所以在理论上没有一个总线可以实现100%可靠的传输。

好,总线专题正式开启,但是硬件总线何其多,我自己虽然接触过不少,但深入学习过的也没几个,所以选择了自己熟悉的、常用的、有代表性的总线进行粗略介绍:IIC、SPI、LPC(板内低速总线),UART、CAN(板间低速总线),DDR DRAM、SAS(存储总线),PCIe(通用高速总线),或则再加一个MII总线(非TCP-IP协议,当年看这“红宝书”,在办公位上直接睡着了)?其它的例如:IIS,HW(不是华为,而是High Way),Localbus(当年玩的最溜的就是它了),RapidIO, FC,IB(Infiniband),SATA,EMMC,HDMI,MIPI,USB、BSCAN等等等等,有兴趣且要用到的胖友们可以学习一下。

本章部分相关内容和图片参考自:李凯-《高速数字接口原理与测试指南》;知乎-造物工厂-《掌握总线技术,看这一篇就够了!》。下一章《IIC总线》。

5649

5649

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?