如果一种晶格与另一种晶格的晶格常数几乎相同,就会发生无缺陷外延生长。

在晶格失配较小(小于0.1%)的情况下,两种晶格界面区域的晶格位点会近似匹配,从而发生生长。

如果在界面上存在弹性应变,即每个原子在边界层都会从其原始位置发生轻微位移,那么这种近似匹配就有可能发生。

虽然对于薄层来说,少量应变是可以容忍的,甚至对于量子阱激光器来说也是有益的,但一般来说,晶体中存储的应变能会因为错位(其中一个晶格中缺少一排原子)的形成而降低。

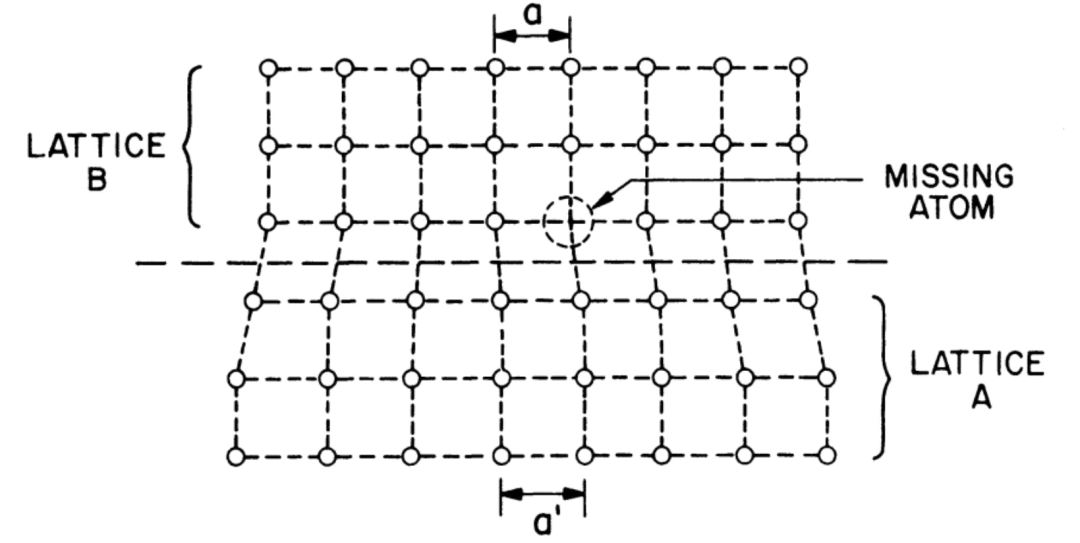

上图为立方晶格 (100) 平面外延生长过程中形成的错位示意图。两种半导体的晶格常数略有不同。

如果a是基底的晶格常数,而a‘=a−∆a为生长层的晶格常数,则每排缺失原子之间的间隔近似为:

L≈a2/∆a

在两个晶格的界面上,缺失原子列沿两个垂直方向存在。沿主晶轴(如 100)的各排之间的间距近似于上述公式 。

这种类型的缺陷在界面上被称为位错。由于它是由晶格失配(或失配)引起的,因此被称为失配位错,简称错位。

在错配位错附近,晶格是不完美的,含有许多悬空键,会导致电子和空穴的非辐射重组。因此,要制造高质量的电子光学器件,就需要无错配位错层。

失配位错的产生取决于晶格失配和生长的外延层的厚度。如果晶格失配∆a/a在-5×10-3至5×10-的范围内,则在(100)InP上生长的InGaAsP-InP双异质结构层(0.4μm厚)中不会形成失配位错。

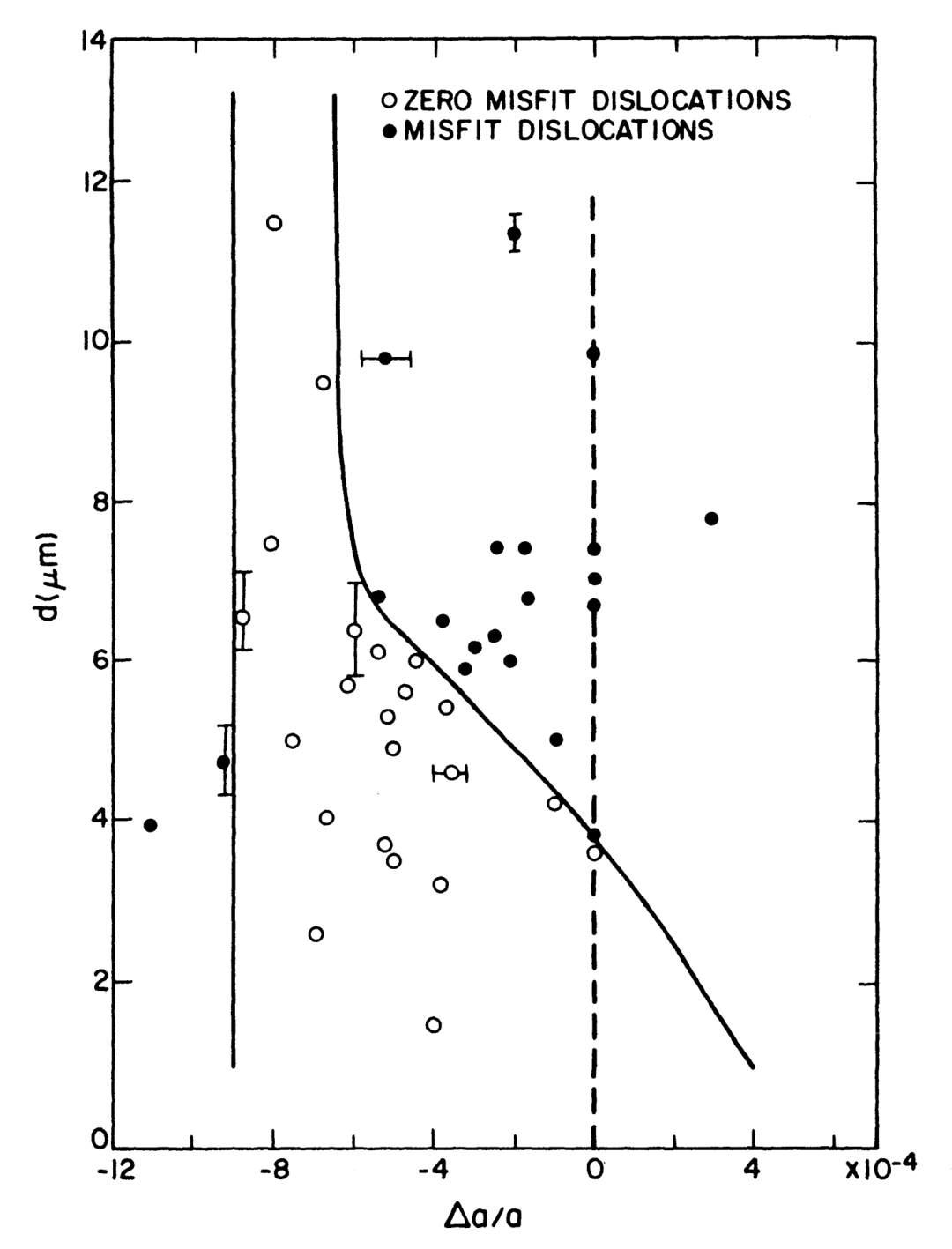

在650℃下生长在 (100) InP 上的不同厚度 InGaAs 层的错位发生与晶格失配的函数关系如下图所示。

这个图表示对于在(100)InP上通过LPE生长的InGaAs的不同层厚度,作为晶格失配的函数的失配位错的发生。在以实线为界的区域中没有观察到错配位错。

如上图所示,实线代表未观察到错位的边界。对于厚的无错位的 InGaAs 层的生长,发现其可容忍的室温晶格失配介于 -6.5×10-4 和 -9×10-4 之间。

产生这种负晶格失配的原因是 InGaAs 和 InP 的热膨胀系数不同,在 650℃ 的生长温度下,完全匹配的层会产生负室温晶格失配。

由于错配位错是在生长温度附近形成的,因此生长温度下的晶格匹配对于产生无位错层非常重要。

773

773

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?