Asynchronous Clock Domain Crossing

时钟间有两种关系:

1. 同步时钟:两个时钟间有可预知的相对相位,通常它们来自相同的时钟源(晶振),且有一个公共周期。

2. 异步时钟:两个时钟间有可预知的相对相位,通常它们来自不同的时钟源(晶振)。

特殊的时钟关系:官方称为Unexpandable Clocks(不可扩展时钟),是指时序引擎在1000个周期内无法判断两个时钟是否有公共周期,比如MMCM生成一个周期为5.125ns的时钟clk1和一个周期为6.666ns的时钟clk2,两者在1000个时钟周期内时钟上升沿无法再次对齐,因此可以视为一种特殊的异步时钟。

在异步时钟间做时序分析,分析结果是不准确且不可信的,需要通过设置时钟组来忽略异步时钟的时序路径上的时序分析。忽略时序分析不意味着数据的跨时钟域传输就是安全的,仍需要设计+约束去保证,如同步器、握手协议、格雷码+最大路径延迟等。

原文如下:

1. The Timing Constraints wizard analyzes the topology of clock domain crossing (CDC) paths between asynchronous clocks and recommends clock groups or false path constraints whenever it is safe to do so.

2. Asynchronous clocks are clocks with no known phase relationship, which typically happens when they do not share the same primary clock or do not have a common period. For this reason, slack computation on asynchronous CDC paths is not accurate and cannot be trusted.

3. You are responsible for adding timing exceptions on these paths, such as set_clock_groups, set_false_path, or set_max_delay -datapath_only to either completely ignore timing analysis or just ignore the clock skew and uncertainty. Also, the design must implement proper CDC circuitry to prevent metastability.

4. In the Vivado Design Suite, the wizard only identifies flip-flop-based synchronizers for synchronous data and asynchronous reset

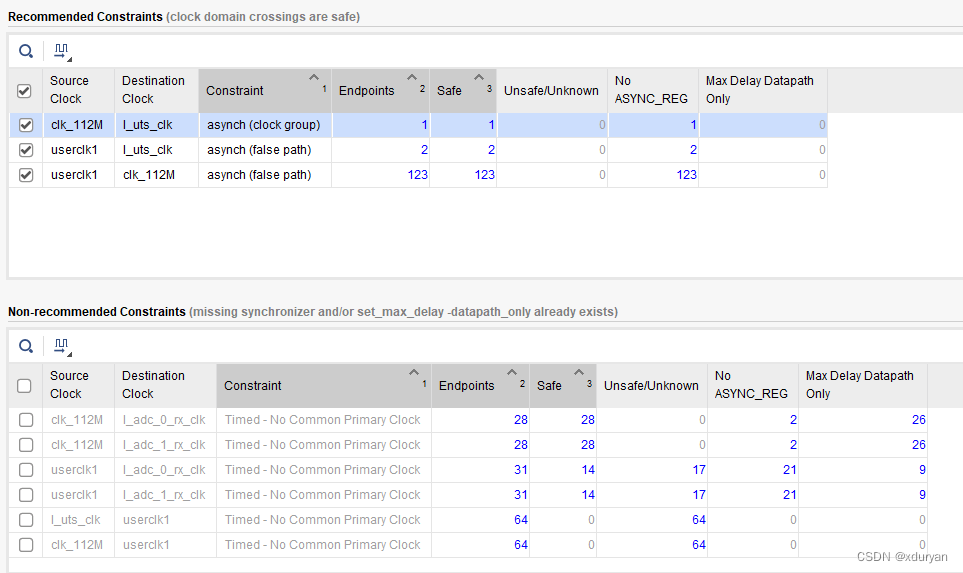

如下图所示,Wizard会识别两类异步时钟,Recommended 和Non-recommended。

上图中:

asynch(clock group):for the cases where it is safe to ignore timing in both directions, in which case a set_clock_groups constraint is created.

asynch (false path) :when it is only safe to ignore the paths in one direction, in which case a set_false_path constraint is created.

Safe:表示异步时钟之间有Synchronizer或Max Delay Datapath Only约束,如Non-recommended部分第3和第4行,Safe有14条路径,包括5条用户路径(Synchronizer)和9条FIFO跨时钟域路径(Max Delay Datapath Only);

Unsafe/Unknown:表示异步时钟间没有Synchronizer或Max Delay Datapath Only约束,如Non-recommended部分第5和第6行;

No ASYNC_REG:表示有Synchronizer但是至少有一级Synchronizer未设置ASYNC_REG属性约束。Xilinx推荐对Synchronizer设置ASYNC_REG属性约束,理由如下:

1. Xilinx recommends that all synchronizer flip-flops have their ASYNC_REG property set to true in order to preserve the synchronizer cells through any logic optimization during synthesis and implementation, and to optimize their placement for best Mean Time Between Failures (MTBF) statistics.

Max Delay Datapath Only:一般都是FIFO内部使用格雷码编码跨时钟域路径,对路径对打延迟进行约束,保证跨时钟域信号的正确性。

Recommended Asynchronous Clock Groups Constraints

原文如下:

1. All paths have synchronizers in both directions.

2. No path is covered by a set_max_delay -datapath_only in either direction (set_clock_groups has higher precedence and overrides any existing set_max_delay).

要满足两个条件:1、双向都有同步器;2、无set_max_delay约束。

Non-recommended Asynchronous Clock Groups Constraints

原文如下:

1. At least one path is missing a synchronizer in either direction.

2. At least one path is covered by set_max_delay -datapath_only in either direction.

3. For the cases where the wizard does not recommend a constraint due to the presence of some set_max_delay -datapath_only, the other CDC paths that are normally timed must be reviewed individually and possibly ignored by additional false path constraints.

3389

3389

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?