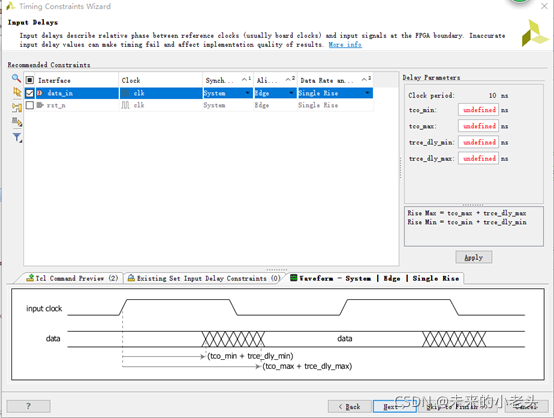

本篇用vivado timing constraints wizard来进行set_input_delay的约束,set_input_delay界面如图一所示,包括interface,clock,synchronous,alignment,data rate and edge。几个参数,synchronous选择是系统同步还是源同步,aligment选择是边沿同步还是中心同步,data rate and edge 选择是上升沿采样,下降沿采样还是双沿采样。首先我们用系统同步方式来进行分析验证,选择系统同步,上升沿采样时,右边有tco_min,tco_max,trce_dly_min,trce_dly_max四个参数,tco_min为外部芯片的tco最小值,tco_max为外部芯片的tco最大值,trce_dly_min为数据信号从外部芯片到FPGA管脚的最小延时,trce_dly_max为数据信号从外部芯片到FPGA管脚的最大延时,此时vivado默认clk到FPGA和到外部芯片的skew为0,符合我们前面分析的公式input_delay = Tco+Tlogic_PCB – Tskew_PCB。

图一

系统同步方式要求清楚外部芯片的TCO和数据信号到达FPGA的延时以及clk到达外部芯片和FPGA的skew。

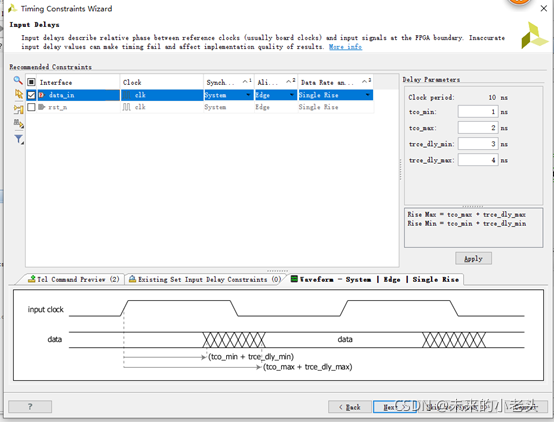

我们设定了如图二的约束,设置完成后,在xdc文件中创建了如下约束:

set_input_delay -clock [get_clocks clk] -min -add_delay 4.000 [get_ports data_in]

set_input_delay -clock [get_clocks clk] -max -add_delay 6.000 [get_ports data_in]

图二

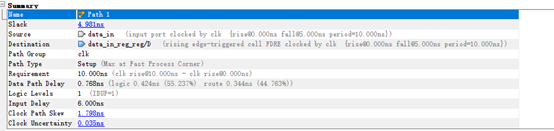

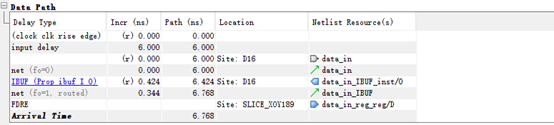

继续让软件完成布局布线,查看IO口的时序路径分析如图三图四图五所示:

图三

图四

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?