本系列参考文献 — FPGA时序与约束分析-吴厚航

FPGA从综合到实现需要的过程如下:synth_design -> opt_design -> place-design -> phys_opt_design -> route_design

1、时序约束的理解

2、时序约束的基本路径

3、时序约束的步骤

4、时序约束的主要方法

5、查看相关时序信息

1、时序约束的理解

FPGA的设计约束分为物理约束和时序约束:

- 物理约束主要包括 I/O 接口约束,布局约束,布线约束以及配置约束。其中 I/O 接口约束主要为引脚分配、电平标准设定等物理属性的约束。

- 时序约束是涉及FPGA内部的各种逻辑或走线的延时,反应系统的频率和速度的约束。

FPGA实现时序约束与分析的流程可以定义为:

- 提出时序要求:设计者根据实际的系统功能,通过时序约束的方式提出时序要求;

- 根据要求布线:FPGA编译工具根据设计者的时序要求,进行布局布线;

- 给出时序报告:编译完成后,FPGA编译工具针对布局布线的结果,套用特定的时序模型给出最终的时序分析和报告。

- 根据报告修改时序设计:设计者通过查看时需报告,确定布局布线后的时序结果是否满足者及要求。

时序约束中的欠约束和过约束:

- 欠约束:约束的过松,约束要求比实际要求低;

- 过约束:约束的过紧,约束要求比实际要求高。

2、时序约束的基本路径

时序约束所覆盖的时序路径主要有一下4类:

- reg2reg,FPGA内部寄存器之间的时序路径;

- pin2reg,输入引脚到FPGA内部寄存器的时序路径;

- reg2pin,FPGA内部寄存器到输出引脚的时序路径;

- pin2pin,输入引脚到输出引脚之间的时序路径(不通过寄存器)。

3、时序约束的步骤

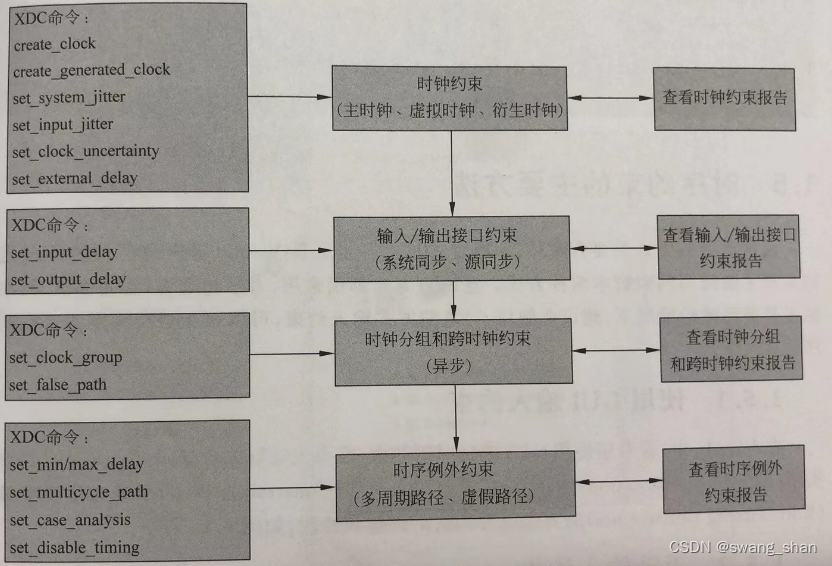

时序约束通常分为4个主要步骤:时钟约束 —> 输入/输出接口约束 —> 时钟分组和跨时钟约束 —> 时序例外约束。

4、时序约束的主要方法

注意: 时序约束辅助工具或者相关的TCL命令,都必须在 open synthesis design / open implemention design 后才能有效运行。本章示例中在synthesis和implemention目录下操作一样。

(1)、GUI

1)、时序约束向导

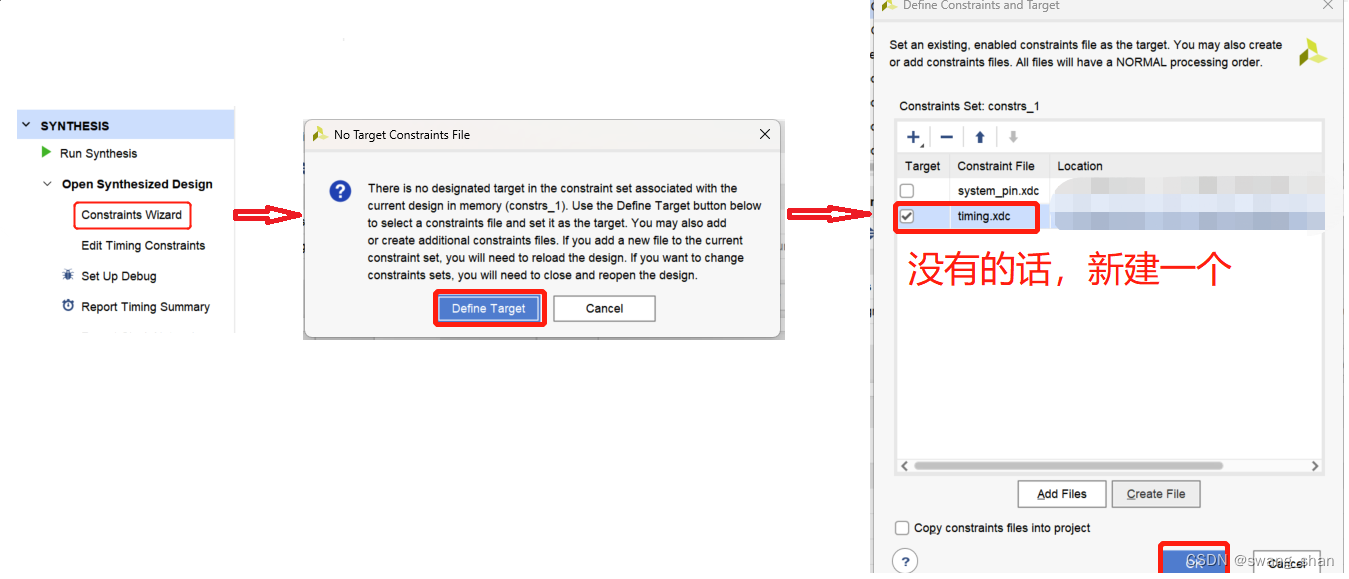

时序约束向导首次打开,需要选定时序约束的目标XDC文件,流程如下图。

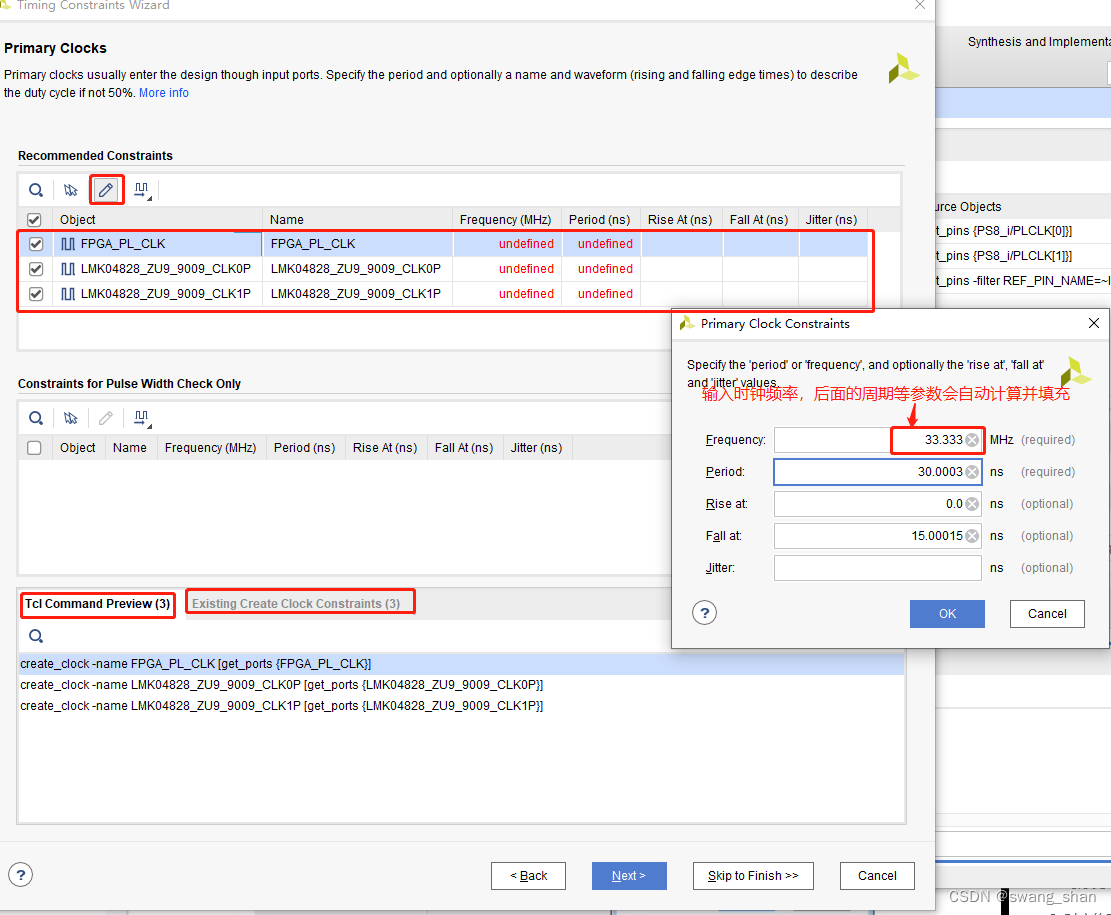

已有目标xdc文件后,打开时序约束向导,在弹出的窗口点击next后,按照 primary clocks/generated clocks等时钟顺序一页一页显示添加约束。会显示当前需要添加约束的部分时钟(只显示get_port,pins和nets不显示)以及已经约束的时钟。

2)、时序约束编辑器

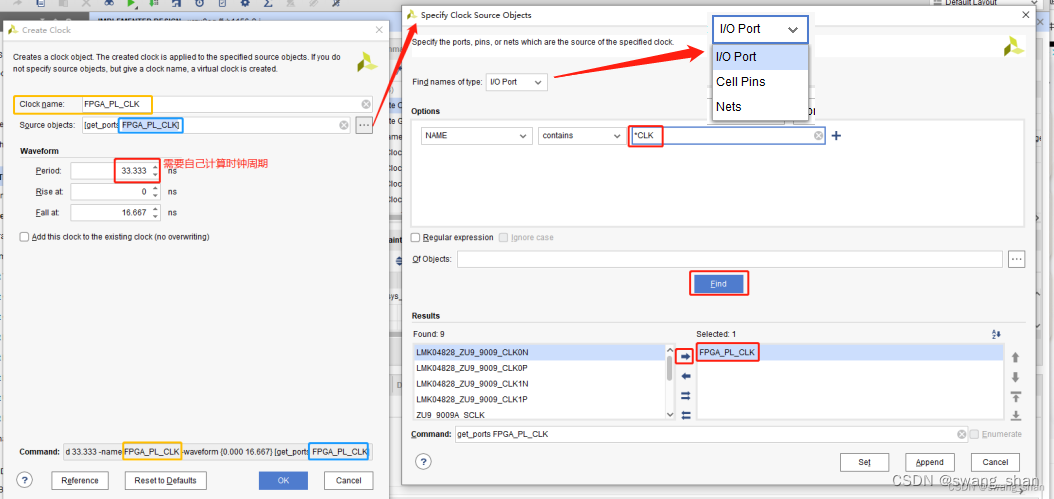

时序约束编辑器打开方法见下图。在时序约束界面可以按照左边的Clocks分组添加时钟约束。

详细时钟添加流程见下图:

如果当前没有指定目标约束文件,在点击保存会弹出下图界面,只要选定目标文件即可。

(2)、手动输入约束

在.xdc文件中进行编辑。在 vivado 的 Language Templates 中,有基本语法模板。

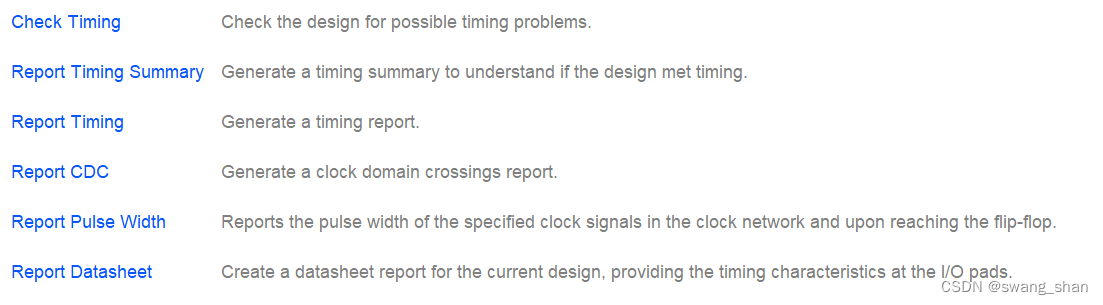

5、查看相关时序信息

相关tcl命令见下图:

(1)识别设计时钟

查看所有时钟:report_clock_networks(Tcl),打印已约束和未约束的所有时钟。

时序确认报告: check_timing(Tcl),打印工程基本信息以及12条check timming。这12条报告中,可以确认当前工程的时序约束状态,明确有多少路径目前没有被约束。

(2)查看时钟信息:

查看已约束时钟的详细信息: report_clocks(Tcl)打印包含时钟周期在内的的所有时钟信息。

查看是否有 unsafe 时钟:report_clock_interaction(Tcl) 或 Implentation- Report Clock Interaction(推荐)。

查看时序约束状态:report_timing_summary (Tcl)或者 Implentation- report timing summary (推荐)或者直接 open implemented design ,查看 Timing 窗口,主要查看WNS、TNS、WHS、THS、WPWS、TPWS这6个参数,参数具体含义及标红报错修改方法见后续文章。

541

541

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?