前言

MIPI联盟于2013年成立 “MIPI I3C Working Group” ,并在2018年发布I3C协议规范V1.0版本。I3C具有复杂的协议规范,本文只对相应的硬件知识进行一个简单的归纳总结。

注:个人水平能力有限,出错点请各位大佬不吝赐教。

1、简介

MIPI联盟,即移动产业处理器接口(Mobile Industry Processor Interface 简称MIPI)联盟。MIPI(移动产业处理器接口)是MIPI联盟发起的为移动应用处理器制定的开放标准和一个规范。

I3C,全称Improved Inter-Integrated Circuit,顾名思义,它是I2C(Inter-Integrated Circuit)的横向升级版,可向下兼容。

在标准CMOS I/O上,它支持10Mbps的最低数据速率,具有更高性能的高数据速率(HDR)模式的选项,与现有选项相比,性能和功耗效率大幅提升。它还提供多主机支持、动态寻址、命令代码兼容性和高级电源管理功能(如睡眠模式)的统一方法。

2、接口特性

2.1 基础原则

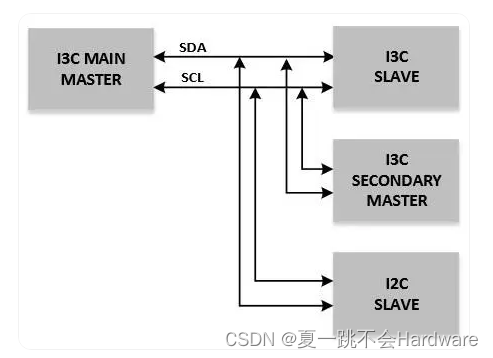

I3C与I2C一样,为2线传输(SDA、SCL),但是支持多主机和多从机。

a、2线串行接口(使用SDA和SCL),时钟频率高达12.5 MHz。

b、向下兼容I2C。

c、I3C采用动态寻址,由主设备给从设备分配动态地址,同时也支持静态I2C寻址。

d、支持I2C单数据速率消息传送 (SDR)。

e、支持可选的高数据速率消息传送模式 (HDR)。

f、支持多点,支持带内中断,支持热插拔。

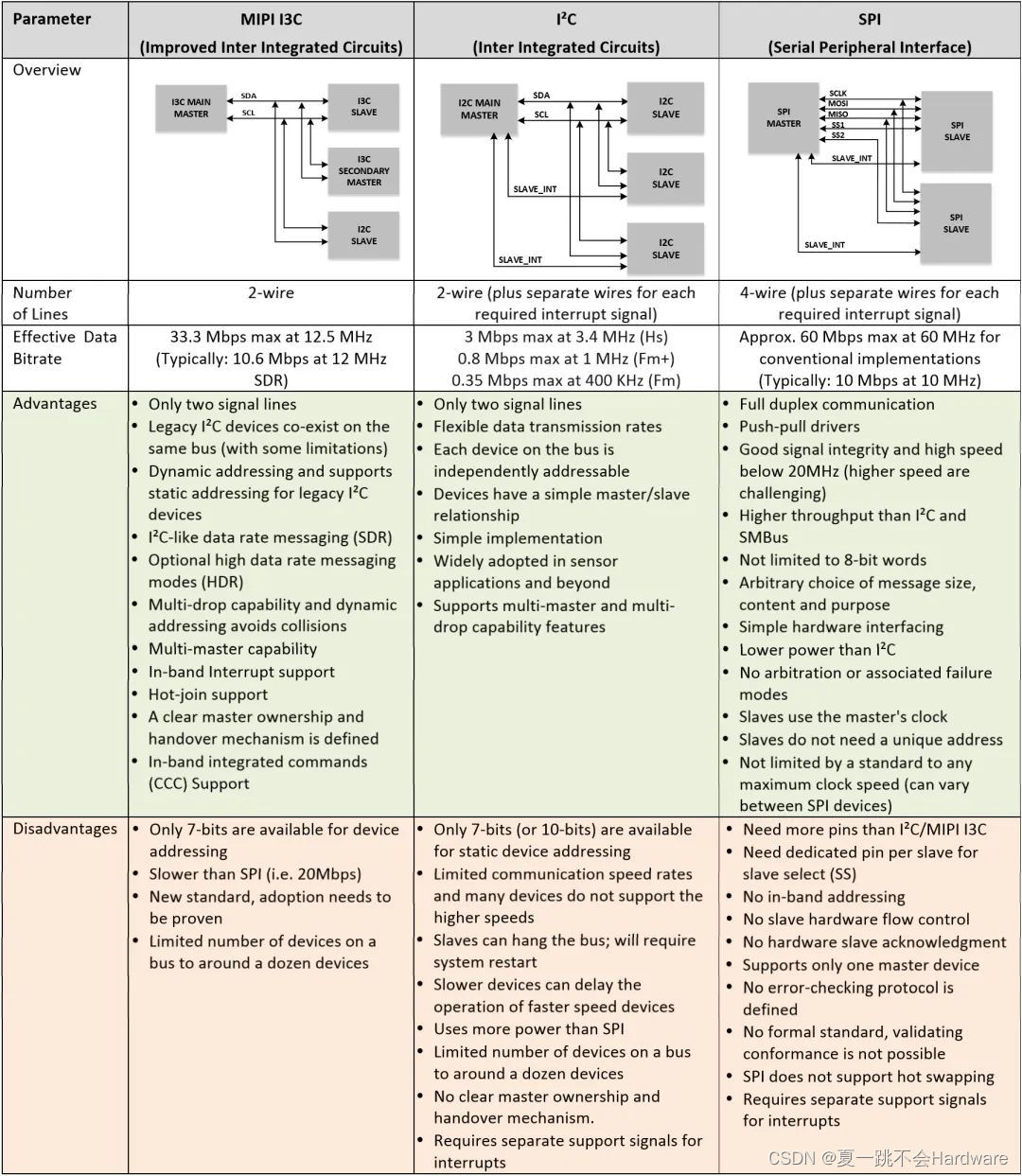

上表中可以看出I3C与I2C和SPI的特性对比,传输速率以及频率要求等。以及各接口协议的优缺点。

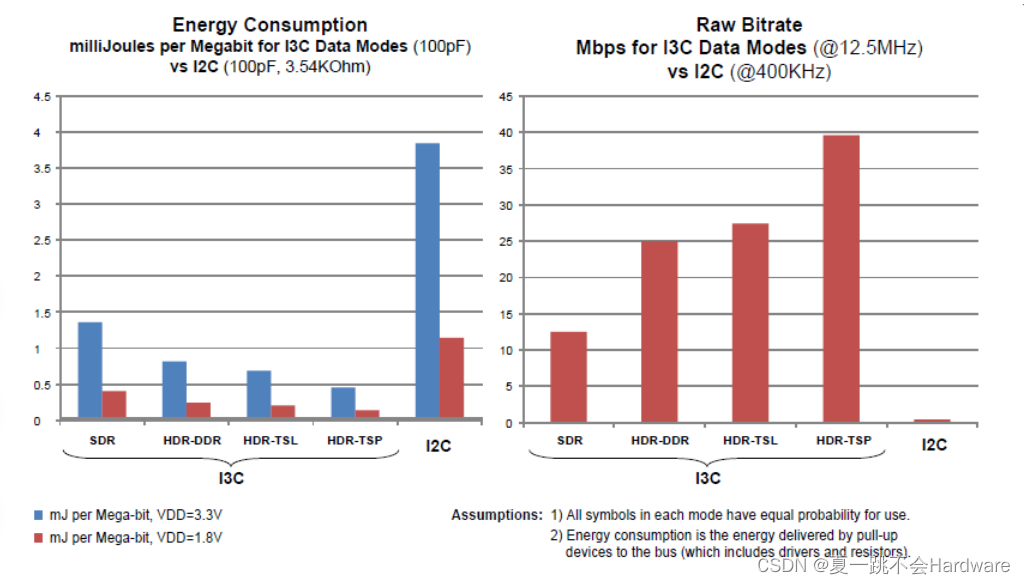

(1)功耗:最低支持1.2V电平(支持1.8V/3.3V,不支持5V)。在同样的电平标准下,整体功耗远小于I2C。

(2)速度:SDR模式(单边沿采样)基础速率12.5Mbps(最低10Mbps),HDR模式(双边沿采样)理论最大速率39.5Mbps(实际有效传输速率在33.3Mbps左右)。

(3)总线结构:两线(SDA/SCL)串行接口,开漏/推挽可灵活切换,支持多主多点功能(Multi-Controller and Multi-drop capabilities)。

(4)热加入机制(Hot-Join):I3C协议支持热加入机制,以允许从设备在已配置后加入I3C总线。

(5)动态地址(transaction):支持,从设备地址由当前的主控制器(Active Controller)初始化后分配,通常在上电后完成。

(6)中断机制(In-Band Interrupt):支持内中断,从设备通过I3C总线产生中断并通知主控制器,节省1根INT线。

当所有设备共同挂载到1个I3C总线时,总线被命名为“混合快速总线(Mixed Fast Bus)”,若仅有I3C设备时,被成为“纯总线(Mixed Bus)”;还有1个“混合低速/受限总线(MixedSlow/Limited Bus)”。混合快速总线和混合低速/受限总线的主要区别就在于I2C设备是否存在50ns的尖峰滤波器。

2.2 术语定义

简单介绍几个常见术语,详细内容还请阅读协议规范。

ACK:应答信号,NACK没有应答;

Address Arbitration:地址仲裁,为了避免争用;

Arbitration:仲裁,如果两个设备同时传输,则需要仲裁来确定总线控制,如果主设备寻址多个从设备,那么从设备传输过程中可能也需要仲裁;

Bridge Dvices:桥设备,I3C总线上的设备允许从本地I3C总线协议转换为另一种协议(SPI、UART等);

Bus Available Condtion:总线可用状态,SCL和SDA至少保持高电平时间,然后设备能够在总线上启动事务;

Bus Free Condtion:总线空闲状态,在STOP之后START之前至少保持时间;

Bus Idle Condtion:总线空闲状态的延长持续时间,指示有设备可能热加入I3C总线;

2.3 主从设备

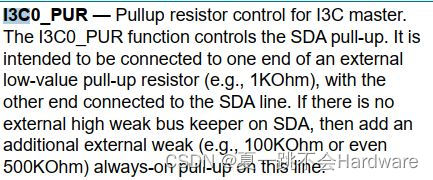

I3C总线要求一次只有一个设备作为I3C主设备。在I3C术语中,这个I3C Master Devecs就是Current Master。在典型应用中,当前主设备是总线上的I3C设备,它发送大部分的I3C命令(CCC编码),寻址所有从设备(广播)或则特定单个从设备(定向)。Current Master也是I3C总线上唯一允许发送I2C消息的设备。除了发送I3C命令和I2C消息外,I3C主设备还可以:生成总线时钟;管理上拉结构;管理动态地址分配过程,包括热连接事件;管理START来自总线上从设备的请求以及地址仲裁请求;支持I2C传统从设备;支持I3C SDR模式。

除了主机外,I3C总线还支持多个从主机,即第二主机,但是其地位低于主机。

I3C总线最多支持11个从机,数量受多种因素影响,例如PCB走线,设备容性负载,从设备类型等。

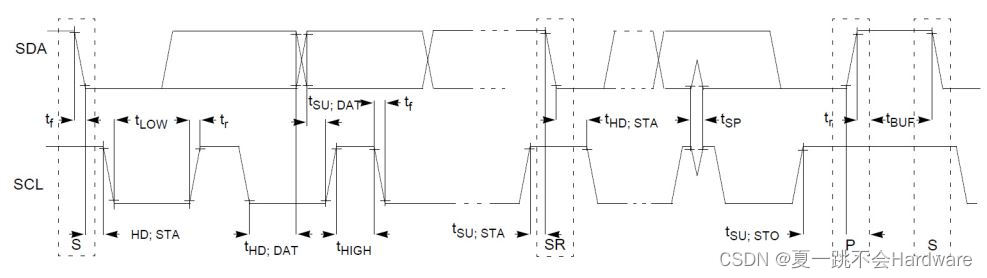

3、时序协议

对内部寄存器不详细介绍,仅对时序做简单叙述。I3C具有多种模式,下面为基础的时序图,各种时序参数请自行参阅协议文档。I3C相比I2C和SPI还是比较复杂的,I3C同时引入了CDR,可以想象,2线的标准引入如此多的功能,必然带来更多的复杂性。

3.1 通信启动

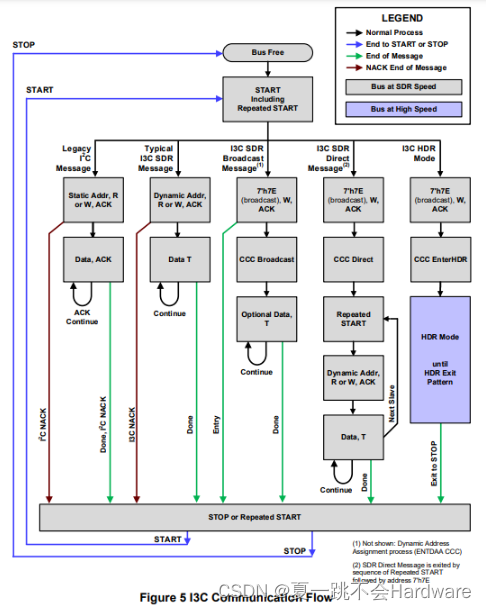

所有的I3C通讯都在一个帧中完成。帧起始于START,接着是数据传输,最后是STOP。

HDR模式下:首先发送一个I3C专用广播地址,然后发送一种EnterHDR CCC命令,接着传送数据,最后产生HDR终止模式序列HDR Exit来退出HDR模式

I3C是一种基于帧封装的通讯方法。帧中包含通讯载荷。协议中的载荷可以使SDR也可以是HDR。帧的传输控制仍然使用类似标准I2C通讯协议的管理方法。

I3C的帧通常至少包含START,Header,Data,STOP.

跟在START后的Header允许总线仲裁。Master使用Header来选定SLAVE。Slave可以通过总线仲裁机制实现多种目的:在线中断请求,热接入,候选主设备请求。

通用命令代码被用于实现进入High Data Rate模式。理解一点很重要,I3C的HDR消息模式下总线活动与传统I2C并不兼容。例如,HDR-TSP模式下数据载荷的编码方案是同时在SDA和SCL线上以3进制位流进行数据传输,并将时钟信息嵌入到通讯协议里

I3C一次只允许一个Master控制总线,但提供将Master角色从一个Device转交到另外一个Device的握手协议。

3.2 通信格式

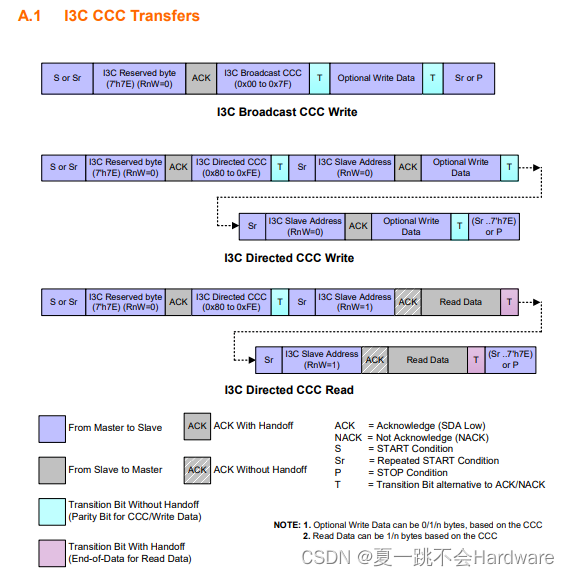

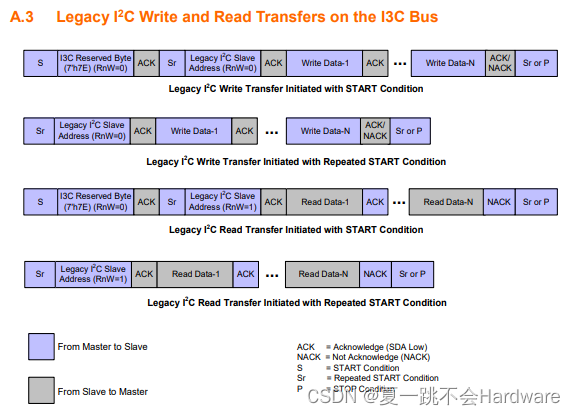

分别给出了I3C基础通信和兼容I2C的通信格式:

3.3 通信协议

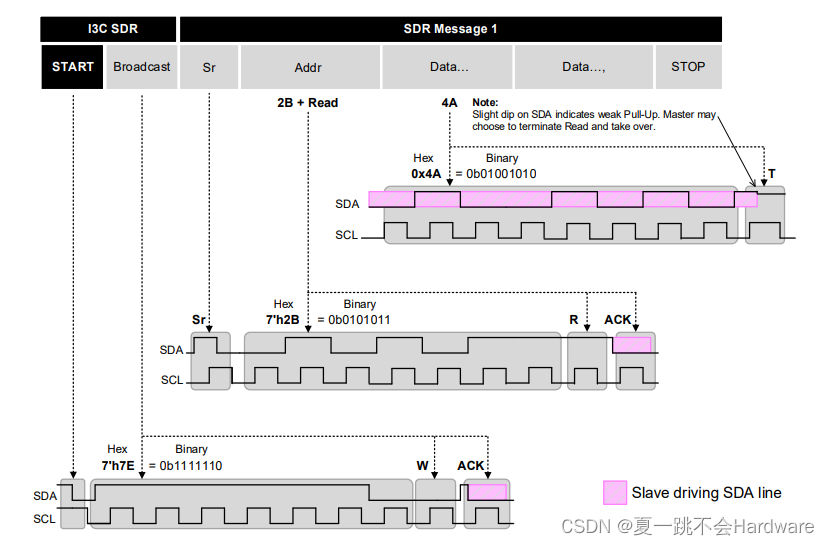

I3C的SDR:

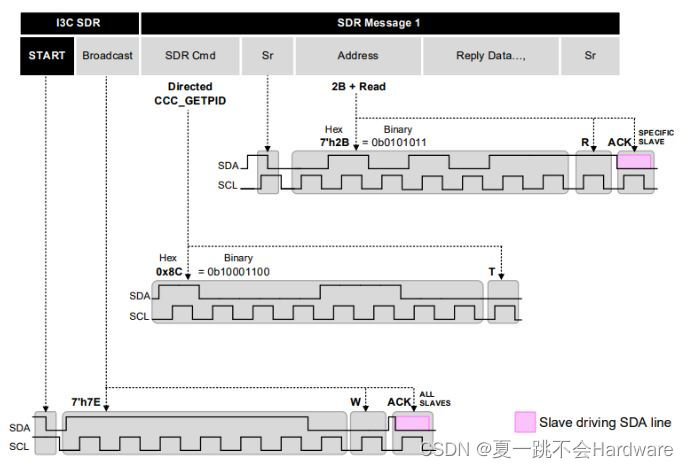

SDR下的CCC:

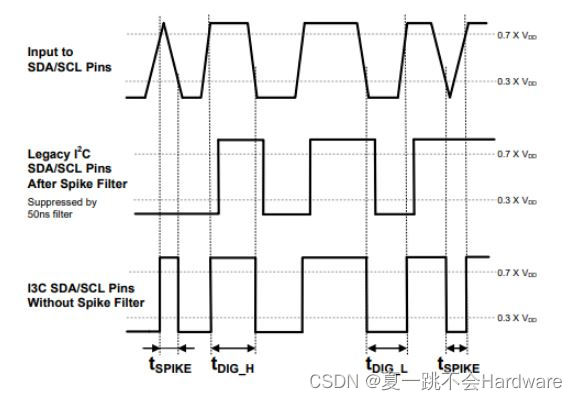

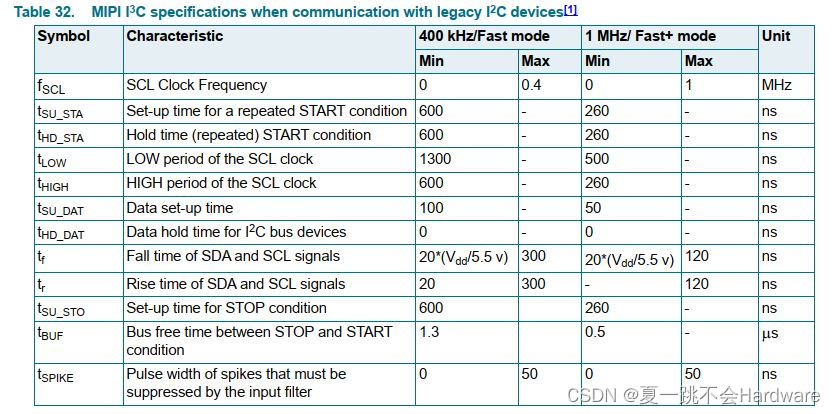

与传统I2C设备相比,需要满足其相应的尖峰滤波器时序参数,以确保传统I2C设备能正确忽略掉I3C的高速模式。建议SDA和SCL都带有尖峰滤波器。

4、应用

I3C最初的设计初衷是作为用于所有数字接口传感器的单一接口用于移动应用。但是,它现在适用于MCU、传感器、控制器、电源调节器、FPGA等的所有中速嵌入式和深度嵌入式应用中。由于I3C的低功耗特性,允许多点连接,适用于所有嵌入式系统

以NXP芯片为例:LPC553X MCU,支持一个I3C接口用于连接外围器件。

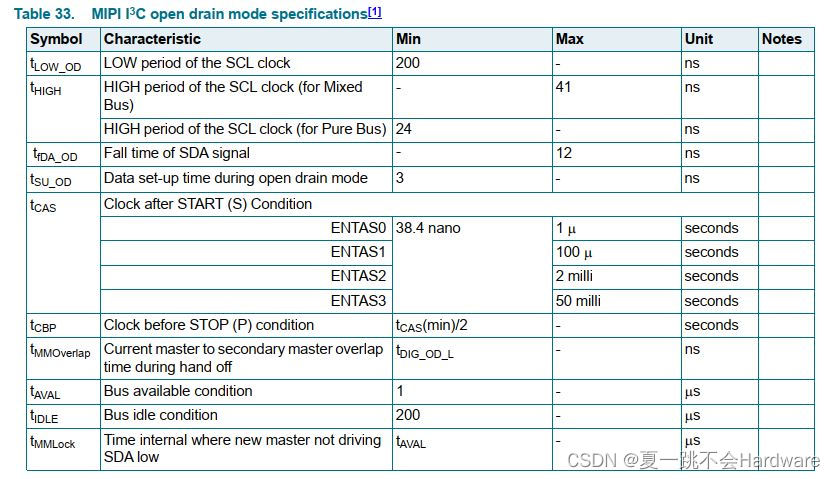

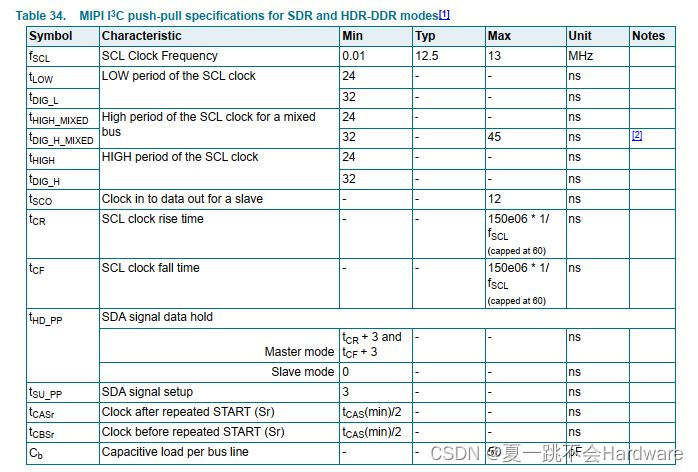

Datasheet中给出了I3C接口相关传输模式的时序特性:

还需要关注该芯片I3C接口的典型功耗,其功耗与频率有关系。

该芯片还带有一个I3C推挽模式I/O口:

并给出了相应的电路设计参考供设计者借鉴。

3、与I2C的区别

功能上具有一些差别,主要是针对I2C的一些缺点进行改进。

I3C相对于I2C具有更高的传输速率,更低的功耗。

简单来说,I3C就是I2C的升级版本,具有更高的传输速率,更多的功能,更低的功耗。

I3C协议较为复杂,想要进一步学习可以研读协议规范手册。

1863

1863

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?