调频连续波雷达具备成本低、时带积大、信号能量高、抗背景杂波能力强、便于携带等优势,在特种测量、检测与安防中发挥了巨大的作用。在连续波雷达的诸多技术中,提高测量精度和检测概率是极为重要的一个环节,因此对这两个方面的深入研发具有重要的实际意义。论文的主要工作包括:1.介绍了锯齿波FMCW雷达的具体流程图和工作原理,推导了测距、测速和测角原理,论述了锯齿波FMCW雷达的距离速度耦合与解耦合问题;分析了距离分辨率与速度分辨率。2.设计了基于FPGA+DSP框架的锯齿波FMCW雷达中频硬件平台,充分发挥FPGA的并行逻辑能力和DSP的计算能力。方案主要包括:中频信号的预处理模块、数据采样模块、FPGA信号处理模块、DSP模块外围电路、UPP通信协议和电源模块,阐述了整体电路的电磁兼容性和布局设计中需要注意的问题。3.对连续波雷达的目标检测算法进行了推导、仿真和验证。主要包括:FIR滤波器滤除高频背景杂波;针对FFT算法的栅栏效应采用FFT+Chirp-Z算法以提高测量精度;针对CA-CFAR检测算法出现遮蔽效应以及审核式恒虚警算法容易出现虚警的问题,提出相应的改进算法来改善这两个问题;针对传统的MUSIC算法无法测量相干信号角度的问题,使用改进的MUSIC测角算法改善了这一问题;提出将满足一定要求的数据处理结果反馈于信号处理中的测距、测速与测角算法的思路,提高信号处理算法的效率。4.对整个系统的硬件和软件分别进行测试,分析测试结果;然后对整个雷达系统进行外场实验,并分析测试结果以及产生误差的原因,为进一步优化提供了可靠的实践基础。实验结果表明本系统工作稳定,可以较为准确地测量出目标的位置,测试得到的主要指标达到了项目设计要求,实现了信号处理的实时性。

1 评估板简介

- 基于TI OMAP-L138(定点/浮点DSP C674x+ARM9) + Xilinx Spartan-6 FPGA处理器;

- OMAP-L138与FPGA通过uPP、EMIFA、I2C总线连接,通信速度可高达228MByte/s;

- OMAP-L138主频456MHz,高达3648MIPS和2746MFLOPS的运算能力;

- FPGA兼容Xilinx Spartan-6 XC6SLX9/16/25/45,平台升级能力强;

- DSP+ARM+FPGA三核核心板,尺寸为66mm*38.6mm,采用工业级B2B连接器,保证信号完整性;;

- 支持裸机、SYS/BIOS操作系统、Linux操作系统。

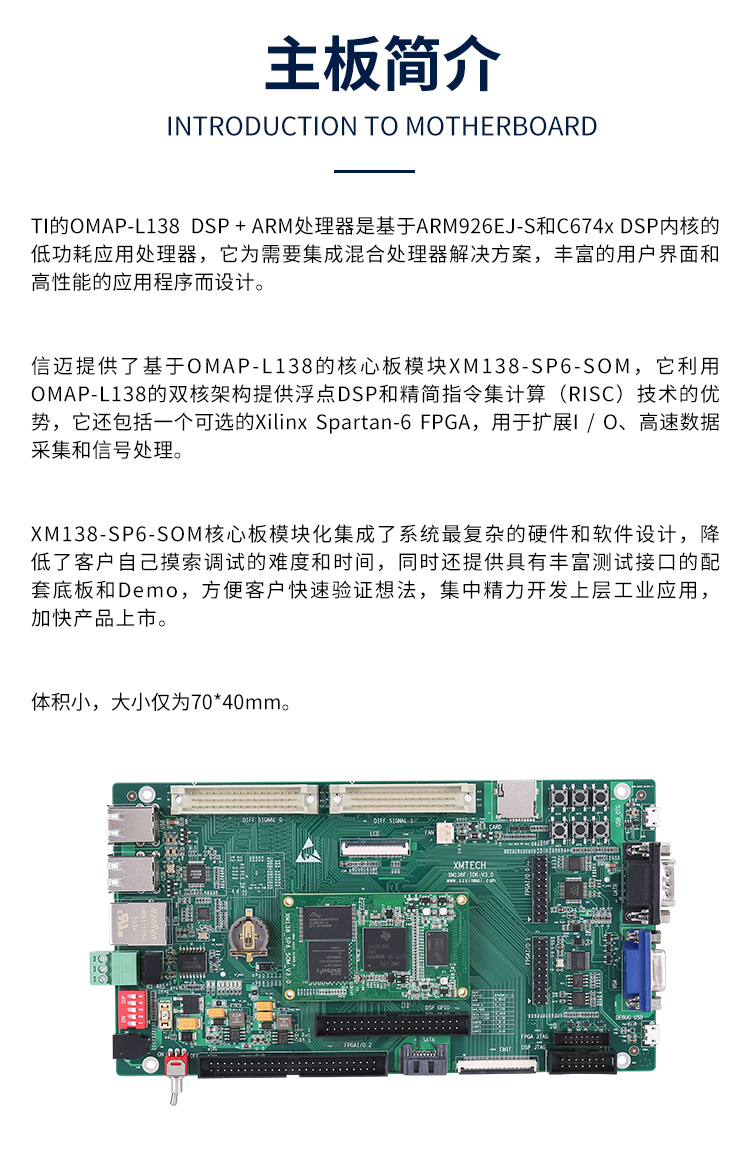

图1 开发板正面和侧视图

XM138F-IDK-V3.0 是一款基于深圳信迈XM138-SP6-SOM核心板设计的开发板,采用沉金无铅工艺的4层板设计,它为用户提供了 XM138-SP6-SOM核心板的测试平台,用于快速评估XM138-SP6-SOM核心板的整体性能。

XM138-SP6-SOM引出CPU全部资源信号引脚,二次开发极其容易,客户只需要专注上层应用,大大降低了开发难度和时间成本,让产品快速上市,及时抢占市场先机。不仅提供丰富的 Demo 程序,还提供详细的开发教程,全面的技术支持,协助客户进行底板设计、调试以及软件开发。

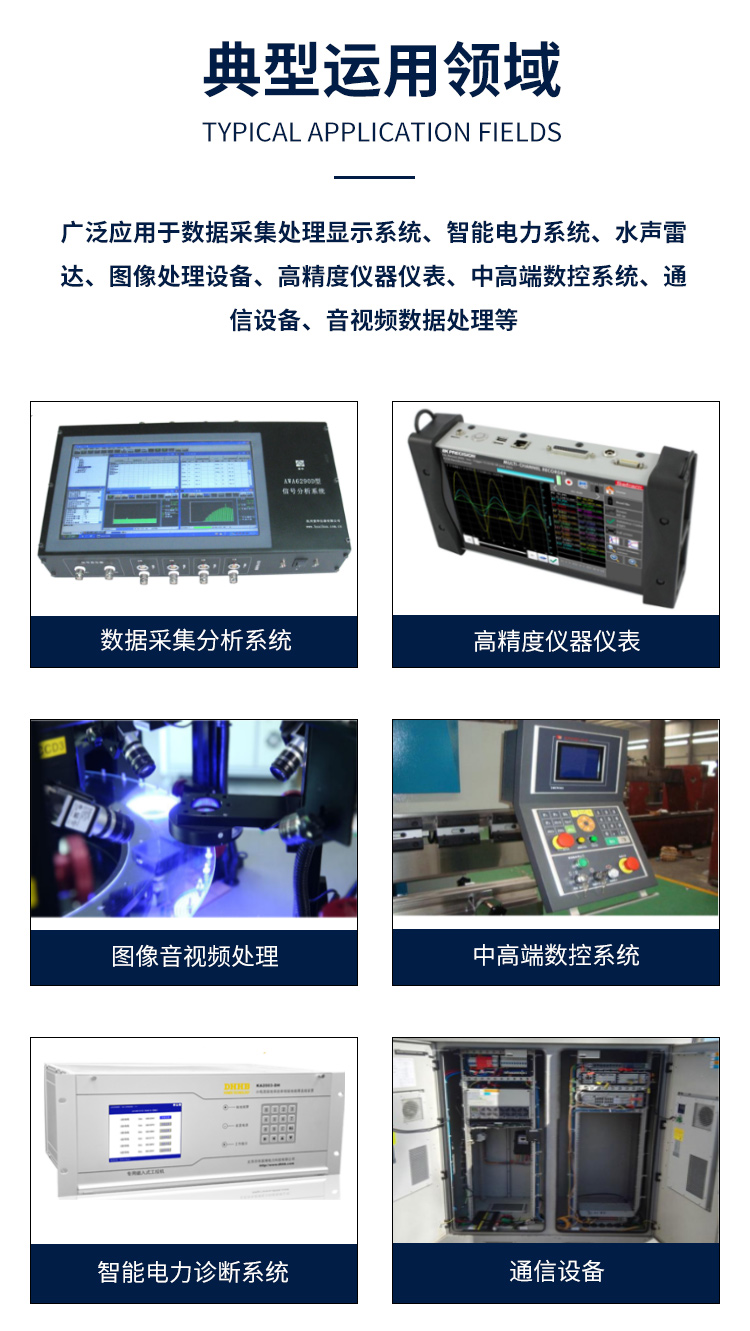

2 典型运用领域

数据采集处理显示系统

智能电力系统

图像处理设备

高精度仪器仪表

中高端数控系统

通信设备

音视频数据处理

图2 典型应用领域

3 软硬件参数

开发板外设资源框图示意图

图3 开发板接口示意图

图4 开发板接口示意图

1469

1469

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?