随着图像处理

、

工业控制

、

无线通信等领域的飞速发

展

,

对数据采集系统的速度

、

精度等性能要求也越来越高

。

这些要求都对数据采集系统的设计和实现提出了新的挑

战

。

目前数据采集系统的设计方案通常分为以下几类

:

1

)

以微处理器单一控制芯片和

A

/

D

转换器形式为主

,

该设计

方案简单

,

在对性能要求不高的应用场合为了降低成本甚

至可以采用集成

A

/

D

转换器的微处理器

[

1

]

。

2

)

采用通用

计算机配置数据采集卡的方式

[

2

]

,

通常需要开发计算机端

应用程序

,

可以完成复杂的计算

,但不同的采集卡相应的驱

动程序不同

,

如果需求改变需要更换采集卡时

,

相应的应用

程序也需要重新开发

。

因此

,

该设计方案通用性差

,

实时性

不高

。

3

)

以

ARM

和

FPGA

或

DSP

和

FPGA

组合方式作为

采集系统的核心

[

3

-

5

]

,

ARM

处理器适合控制领域

,

DSP

处理

器适合信号处理领域

,

FPGA

器件由于其自身特点

,

适合高

速并行采集与处理领域

,

具有

ARM

或者

DSP

等处理器无

法比拟的优势

。

这类组合方式结合各自特点

,

处理能力强

,

应用范围广

。

通过以上分析

,

设计了

ARM

处理器和

FPGA

器件作为数据采集系统的核心

,

ARM

处理器使用

Marvell

公司的

PXA270

,

FPGA

器件使用

Altera

公司的

Cyclone

系

列

EP1C6

,

前端采集芯片使用

Ti

公司的高精度

、

大动态

24

位

A

/

D

转 换 器

ADS1278

进 行 模 数 转 换

。

ARM

和

FPGA

之间的数据交换采 用 双 口

RAM

芯 片 来 实 现

FIFO

功 能

。

系统中

ARM

处理器作为系统控制核心

,

负责控制整个系

统工作时序

、

并将数据通过网络上传到服务器中进行存储

。

FPGA

负责

A

/

D

转换器的模式配置

,

数据传输

。

该组合方

式结合

ARM

在控制方面和

FPGA

在采集方面的优势

,

具

有通用性强

、

配置灵活的特点

。

2

系统设计

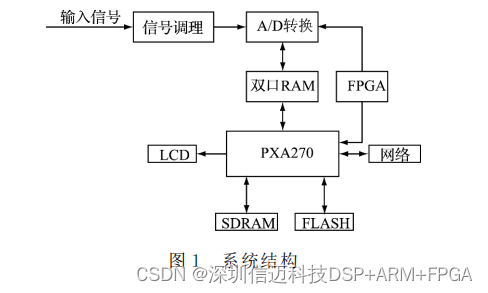

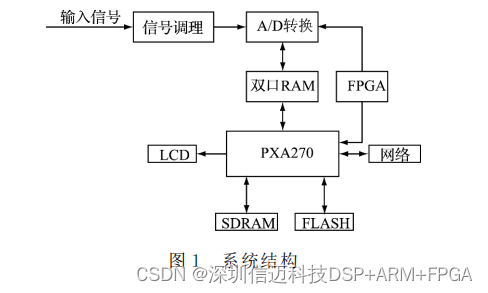

本系 统 硬 件 主 要 由 信 号 调 理 电 路

、

模 数 转 换 器

ADS1278

、

FPGA

器 件

Cyclone

系 列

EP1C6

、

双 口

RAM

IDT7205

和处理器

PXA270

及外围电路

[

6

]

组成

,

系统结构框

图如图

1

所示

。

输入信号经过信号调理电路后

,

进入

A

/

D

转换器进行数据转换

,

将模拟信号转换成

23

位尾数和一符

号位的数据

,

FPGA

配置

A

/

D

转换器并将转换的数据按照

顺序存储到双口

RAM

中

,

当转换数据存储满后中断

ARM

处理器

,

ARM

处理器将数据从双口

RAM

读出进行运算

,

并通过网络接口将采集数据传输到服务器

。

2.1 24

位

A

/

D

转换芯片

ADS1278

ADS1278

[

7

]

是德州仪器

(

TI

)

公司推出的采样率高达

128KS

/

s

、

24

位

8

通道同步采样

Σ

-

Δ

ADC

。

支持多种工

作模式

,

内部集成线性相位数字滤波器

,

数据输出接口支

持

SPI

或可选帧同步

,

便于与

FPGA

互连

。

可满足国防

、

航天和医疗应用

。

ADS1278

转换器内部集成的数字滤波器通过奈奎斯特

采样将输入信号抽取为长度为

1

比特的高分辨率数字信

号

。

8

通道输入信号分别进入独立的

8

个

A

/

D

转换器

,

它

内部由高阶斩波器

、

数字滤波器

、

调制器组成

,

可将输入模

拟信号经过高阶滤波器后得到数字信号

。

ADS1278

的

MODE

[

0..1

]、

FORMAT

[

0..2

]、

SYNC

、

CLK

、

SCLK

、

DRDY

、

DOUT

[

8..1

]

引 脚 分 别 于

FPGA

的

IO

口 相 接

,

其 中

,

MODE

[

0..1

]

引 脚 状 态 决 定

A

/

D

的工作模式

,

FORMAT

[

0..2

]

引脚状态决定数据输

出格式选择

,

CLK

引 脚 需 要 输 入

A

/

D

转换器工作时钟

,

SYNC

、

SCLK

、

DOUT

[

8..1

]

引脚是控制

A

/

D

转换的数据

串行输出帧同步

、

时钟

、

8

通道数据

。

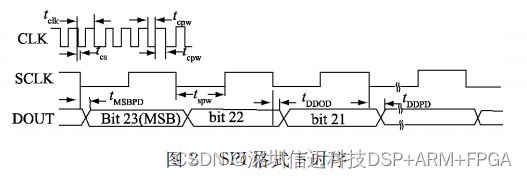

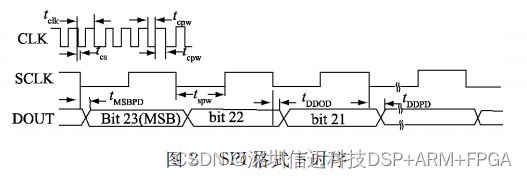

图

2

为

ADS1278

的

SPI

格式下

,

时钟和数据时序图

。

2.2 ARM

与

FPGA

的接口设计

本 系 统 核 心 采 用

ARM

和

FPGA

的 组 合 方 式

,

在

ARM

和

FPGA

之 间 采 用

3

片 双 口

RAMIDT7205

进 行

24bit

数据传输

,

其中

,

FPGA

器件控制

A

/

D

转换

,

并将转

换数据按照一定顺序存储到双口

RAM

中

,

当数据存储完

后将中断

ARM

,

ARM

将双口

RAM

中的数据进行读取

,

比使用

FIFO

传输的方案降低了成本

、

提高了数据传输的

吞吐量

。

本系 统 中

FPGA

的设计作用如下

:

复 位 并 配 置

ADS1278

的工作 模 式

,

FPGA

内部设置一个地址加法器

控制将

A

/

D

转换器的数据写入双口

RAM

中

,

当 双 口

RAM

写满 后

,

大 小

24 KB

,

地址加法器复位

。

ARM

与

FPGA

的接口方式 有 很 多 种

,

如

IIc

、

spi

等串行接口或总

线等并行接口

,

串行接口由于本身的局限性限制了其在大

数据量

、

实时数据的传输的应用

,

而总线的形式更合理一

些

,

稳定性较之更好一点

。

但

ARM

与

FPGA

通 过 地 址

、

数据

、

控制总线直接连接的方式在大数据传输时会影响系

统的效率

,

因 此

,

在

ARM

与

FPGA

之 间 采 用 双 口

RAM

进行连接的方 式

,

ARM

与

FPGA

异 步 工 作

,

提 供 了 系 统

的效率

。

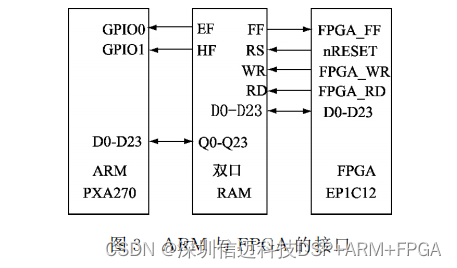

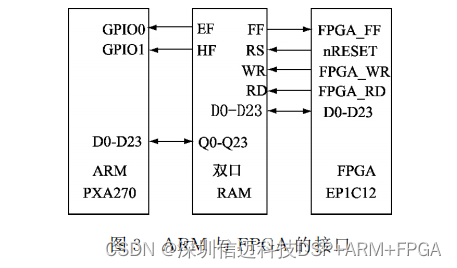

其接口如图

3

所示

。

FPGA

的 控 制 信 号

WR

、

RD

、

nRESET

与 双 口

RAM

IDT7205

的复位信号

RS

、

读写信号

WR

和

RD

连接

,

数据

总线

D0

~

D23

与双口

RAM

的数据总线连接

,

FPGA

通过

内部地址加法器依次将将

A

/

D

转换器的数据串并转换后

写入双 口

RAM

中

。

双 口

RAM

的

EF

、

HF

信 号 分 别 与

PXA270

的

GPIO0

和

GPIO1

连接

,

接受数据写满后产生

的中断

。

PXA270

提 供

6

个分区的静态存储器

Bank0

~

Bank5

,

设计将双口

RAM

的存储空间映射到

PXA270

的

Bank3

上

。

3

驱动程序设计

为了实现

ARM

与

FPGA

通过双 口

RAM

的 数 据 传

输

,

需要设计嵌入式

Linux

下的驱动程序

[

8

]

。

当

FPGA

将

数据写到双口

RAM

中

,

根据双口

RAM

中数据的状态中

断

ARM

处理器进 行 数 据 读 取

。

这一过程主要需要中断

和总线驱动程序配合

。

在中断驱 动 程 序 中

,

通 过

request

_

irq

()

函 数 为 双 口

RAM

的中断分配中断请求

(

IRQ

)

号

,

当处理器检测到这

一

IRQ

号对应的中断产生时

,

将启动该

IRQ

对应的中断

服务例程

[

9

]

。

IRQ

号与中断处理例程是一一对应的

,

在系

统

/

porc

/

interrupts

文件中可以为设备选择

IRQ

号

。

FP

-

GA

将

A

/

D

转换的数据写入双口

RAM

后

,

当数据写满后

会中断

ARM

处理器

,

ARM

会响应中断处理例程

,

读取双

口

RAM

中的 数 据

。

中断处理例程首先要清除

PXA270

的中断寄存器相应的位

,

需要通过对状态寄存器相应位进

行写 操 作

,

这是为了能够继续响应双口

RAM

产 生 的 中

断

。

然后是设置数据传输标志位

,

当主程序中检测到标志

位

,

进而调用总线驱动程序进行数据传输

,

这种工作方式

可以避免中断处理例程的冗长

,

提高系统传输效率

。

由于应用程序工作在用户空间

,

它无法完成对总线的

操作

,

而驱动程序工作在内核空间

,

可完成对总线的操作

,

因此

,

在总线驱动程序中

,

必须支持应用程序对总线的操

作

,

以完成数据的传输

。

传统的

Linux

应用程序需要通过

总线驱动程序完成对总线空间的访问方法是通过

2

个函

数完成用户空间与内核空间之间的数据传递

,

其中内核空

间向用户空间传输数据使用

copy

_

from

_

user

函数

,

用户空

间向内核空间传输数据使用

copy

_

to

_

user

函 数

。

copy

_

from

_

user

,

copy

_

to

_

user

等

。

这种方法虽然能完成

2

个空

间的数据传输

,

但是效率不高

,

最好的方法是将内核空间

能访问的物理地址直接映射到用户空间

,

Linux

内核提供

了

remap

_

page

_

range

函数

,

应用程序对该用户空间的地

址访问相当于直接对物理地址的访 问

[

9

]

。

本 文 的 总 线 驱

动程序就是直接映射的方法

,

来完成快速的读写

。

下面是驱动程序代码段

,

它使用

remap

_

page

_

range

()

函数在驱动程序中完成

mmap

系统调用中物理空间到虚

拟空间的映射

,

remap

_

page

_

range

()

函数原型如下

:

intremap

_

page

_

range

(

vma

_

area

_

struct

*

vma

,

un

-

signedlongfrom

,

unsignedlongto

,

unsignedlongsize

,

pg

-

prot

_

tprot

);

remap

_

page

_

range

()

函数的调用需要初始化

。

虚拟内存空间指针

vma

、

起始地址

、

物理地址

、

映射区

域字节 数 等 参 数

。

首 先 计 算 物 理 地 址

,

然 后 通 过 右 移

PAGE

_

SHIFT

位

,

本系统使用

PXA270

的

Bank3

的物理

空间

,

起始地址

0x0c000000

,

大 小 为

4KB

映 射 到 虚 拟 空

间

。

驱动程序中

,

还需要判断虚拟内存大小和偏移了指定

距离后物理内存的大小

,

如果虚拟内存过大

,

应该返回并

提示映射超出允许的内存空间

。

调用

remap

_

page

_

range

()

函数过程如下

:

remap

_

page

_

range

(

vma

,

vma-

>

vm

_

start

,

0x0c000000 + vma-

>

vm

_

pgoff

<<

PAGE

_

SHIFT

,

vma-

>

vm

_

end- vma-

>

vm

_

start

,

pgprot

_

noncached

(

vma-

>

vm

_

page

_

prot

));

应用程序中调用

mmap

系统就是对

mmap

()

函 数 的

参数初始化

。

mmap

()

函数原型如下

:

void

*

mmap

(

void

*

start

,

size

_

tlength

,

intprot

,

int

flags

,

intfd

,

off

_

toffset

);

首先将文件描 述 符

fd

指 定 的 设 备 文 件 与

start

处 开

始的内存空间关联

,

通常将

start

设为

0

,

mmap

()

函数返回

实际关联 的 内 存 地 址

。

length

为内存映射的字节长度

,

prot

为内 存 保 护 类 型

,

flag

为 映 射 类 型

,

MAP

_

SHARED

标识符表示与其他所有映射这个对象的进程共享内存区

域

。

本设计调用

mmap

()

函数过程如下

:

base=

(

unsignedlong

*

)

mmap

(

0

,

0X100

,

PROT

_

READ

|

PROT

_

WRITE

,

MAP

_

SHARED

,

fd

,

0

);

4

系统实验结果分析

本系统中

,

FPGA

外部晶振频率采用

32.768MHz

,

经

过内 部

16

分 频 器 后 得 到

2.048 MHz

时 钟 频 率 作 为

ADS1278

的工作时 钟

。

ADS1278

完 成

8

通 道

24

位 精 度

的采样 传 输 大 约 需

24

μ

s

,

采 样 数 据 被

FPGA

写 入 双 口

RAM

基本在采样结束后同步完成

。

当双口

RAM

数据被

写满后

,

中断

ARM

处理器进行数据读取

,

ARM

的工作频

率为

520 MHz

,

外部总线时钟频率为

104 MHz

,

配 置

PXA270

外部

Bank3

的

MSC

寄存器为

0x7ff4

满足系统对

双口

RAM

时序读写的需要

。

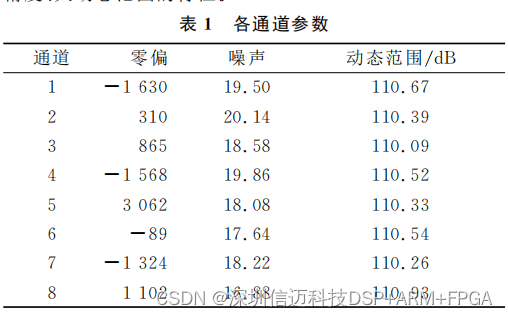

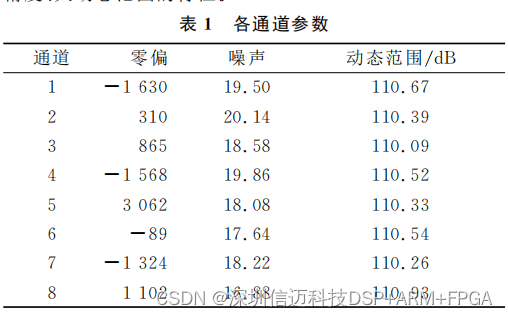

为了提高采集精度

,

首 先 需 要 对

A

/

D

转 换 器 进 行 零

偏校准

,

零偏校准后

,

通过动态范围计算公式

20×lg

(

信号

电压

/

噪声电压

)

得到各通道实际动态范围如表

1

所 示

。

其中零偏电压以转换后的数字形式给出

。

从表

1

中动态

范围一列中可以看出

,

系统各通道实现的动态范围都接近

A

/

D

转换器

24

位采样精度时的理想动态范围

111dB

[

7

]

,

测量结果表明本文设计的系统可充分发挥

A

/

D

转换器高

精度

、

大动态范围的特性

。

信迈提供ARM+FPGA+AD的设计与批量生产解决方案。

3052

3052

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?