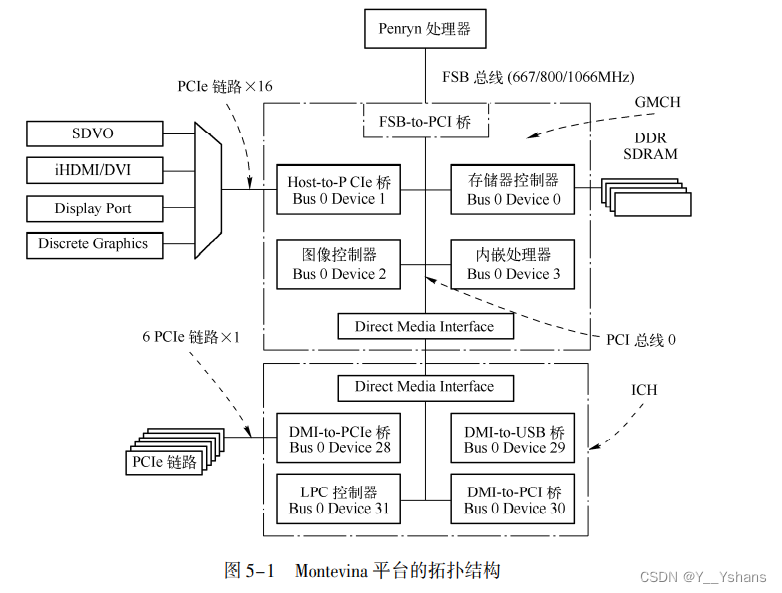

摘要:以Montevina平台为例,说明在x86处理器系统中,PCIe体系结构的实现机制

第 5 章 Montevina 的 MCH 和 ICH

GMCH ( Graphics and Memory Controller Hub):图形和内存控制器集线器

GMCH 和 ICH 之间使用 DMI(Direct Management Interface)接口相连,MCH集成了一些对带宽要求较高的虚拟 PCI 设备, 如 DDR 控 制器、 显卡等。 而在 ICH 中集成了一些低速 PCIe 端口, 和一些速度相对较低的外部设备, 如 PCI⁃to⁃USB 桥、 LPC 总线控制器等。

5. 1 PCI 总线 0 的 Device 0 设备

我觉得这一节简单浏览一下就可以,需要看的时候再回头来看

Device0除了要管理存储器域地址还要管理DDR SDRAM。

5. 2 Montevina 平台的存储器空间的组成结构

在 Montevina 平台中包含一个 Mobile 处理器、 MCH、 ICH 和一个无线网卡 适配器组成。

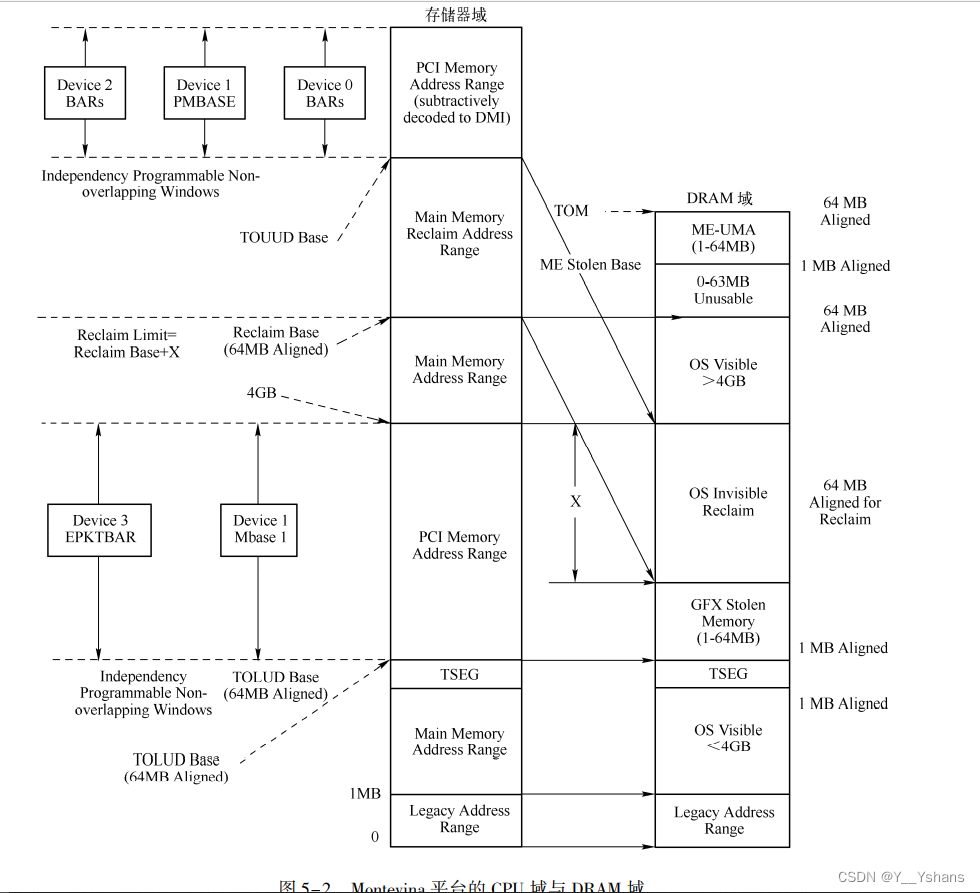

Montevina 平台使用的地址空间由存储器域地址空间和 PCI 总线域地址空间组成。

Montivina 平台除了具有存储器域、 PCI 总线域之外, 还存在一个 DRAM 域。

在 Montevina 平台中, DRAM 域地址空间并不能与存储器域地址空间完全对应。

Legacy地址空间是x86一直都有的,大小1MB

GFX (显卡控制器) 借用的空间:1-64MB,CPU不能访问这段空间

TSEG 空间:这段空间的大小为 1 MB ~ 8 MB。 这段空间仅在 CPU 进入 SMM 模式时, 才 能够被 CPU 访问。

小于 4 GB 的操作系统可用内存空间:在 Montevina 平台中, 如果主存储器的大小超过 4 GB, 那么这段物理空间将被分为三段 供操作系统使用, 分别是小于 4 GB 的空间、 大于 4 GB 的空间和 Reclaim 空间。 如图 5-2 所示, 这几段空间在存储器域中的地址并不连续。

.OS Invisible Reclaim 空间:这段地址存储器域的地址相同,当处理器使能 Reclaim 机制 (也称为 Remapping 机制) 后, CPU 才能访问这段地址空间。

大于 4 GB 的操作系统可用空间:这段空间在存储器域和 DRAM 域中的地址相等, 只有实际的物理内存大于 4 GB 时, 存 储器域和 DRAM 域中才有这段空间。

ME (Manageability Engine) ⁃UMA 借用的空间:其大小为 1 ~ 64 MB。 其基地址为 TOM 寄存器中的值减去 ME⁃UMA 借用空间的大小。 由 于 TOM 寄存器中的值需要 64 MB 对界, 因此有时在其下会出现一个 0 ~ 63 MB 大小的空洞。 这段空洞是被浪费的空间, 除了 DRAM 控制器可以访问这段空间外, 在处理器系统中的其 他部件均不能访问这段空间。

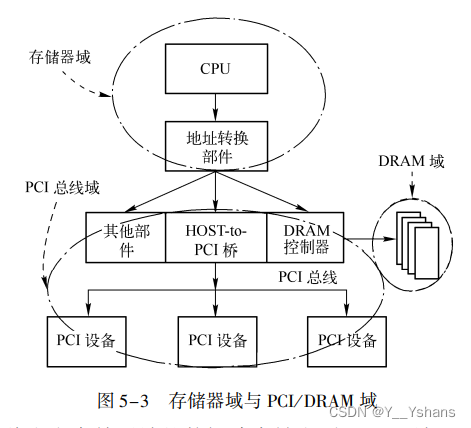

在 x86 处理器系统中, 除了具有 DRAM 域地址空间外, 还具有 PCI 地址空间。 CPU 访 问这些地址空间时, 需要进行地址转换, CPU 访问 DRAM 域时, 需要进行存储器域地址空间到 DRAM 域地址空间的转换;

5. 3 存储器域的 PCI 总线地址空间

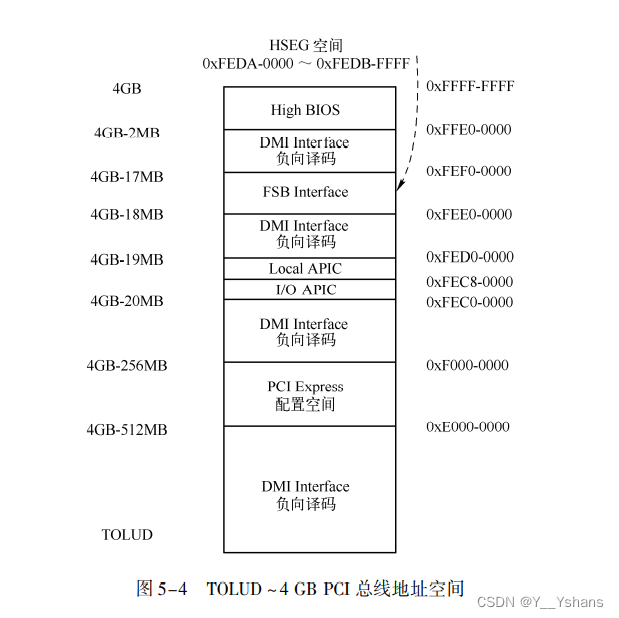

由图 5-2 可知, Montevina 平台中存储器域的 PCI 总线地址空间分为 TOLUD ~ 4 GB 和 TOUUD ~ 64 GB 这两段空间。

5. 3. 1 PCI 设备使用的地址空间

5. 3. 2 PCIe 总线的配置空间

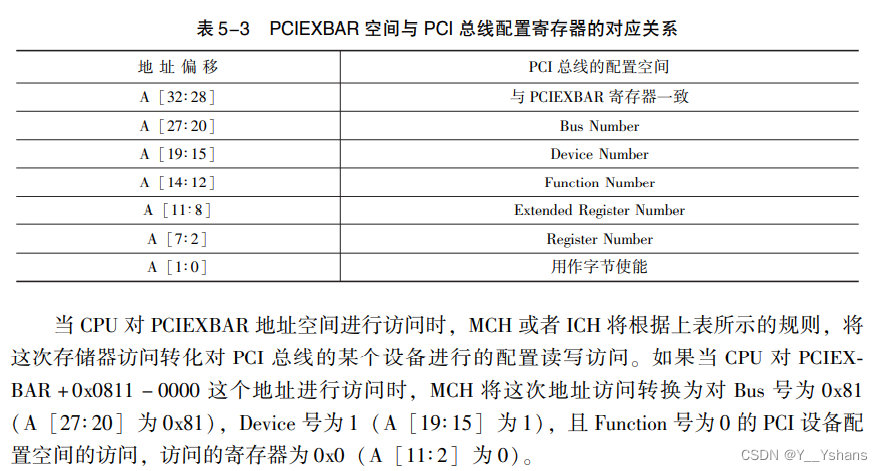

x86 处理器使用了两种机制访问 PCIe 设备的扩展配置空间。 首先 x86 处理器提供了两个 I / O 端口寄存器, CONFIG_ADDRESS 和 CONFIG_DATA 寄存器, 使用这两个寄存器访问 EP 配置空间的方法与访问 PCI 设备类似, 详见第 2. 2. 4 节。 然而这两个寄存器只能访问 PCI 设 备的基本配置空间, 即 PCIe 设备配置空间的前 256 个字节, 而之后的扩展配置空间需要通过 ECAM 方式进行访问。

使用 ECAM 机制与使用 CONFIG_ADDRESS 和 CONFIG_DATA 这对寄存器, 间接访问 PCIe 设备的配置空间有较大的不同。 ECAM 机制是一种直接寻址方式, 在 x86 处理器系统 中, 只有使用 ECAM 方式才可以访问 PCIe 设备的扩展配置空间。

Montevina 平台使用 256 MB 物理空间映射 PCI 设备的配置寄存器, 因为在 Montevina 平 台中有一棵 PCI 总线树, 因此最多具有 256 条 PCI 总线, 每一条 PCI 总线最多可以挂接 32 个 PCI 设备, 每一个设备最多有 8 个 Function, 而在每一个 Function 中最大的 PCI 总线配置 寄存器空间为 4 KB。

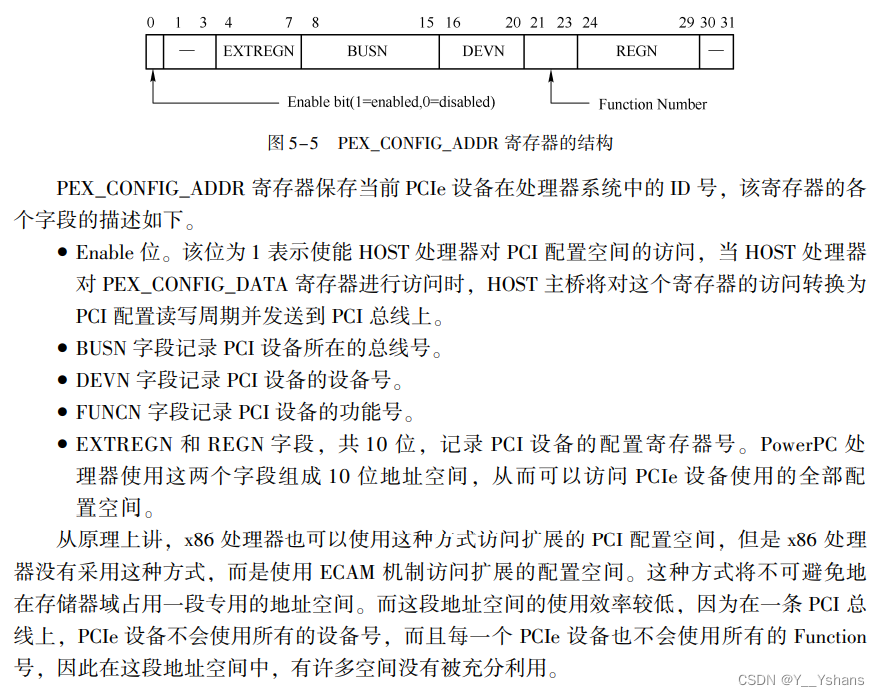

虽然采用 ECAM 方式可以访问之前使用 CONFIG_DATA 和 CONFIG_ADDRESS 寄存器不 能访问的 PCI 扩展配置寄存器空间, 但是也带来了一些问题。 在一个处理器系统中, 同一条 PCI 总线上的 Device Number 不一定连续, 而且在多数 PCI 设备中也不会有 8 个 Function, 这 将造成 PCIEXBAR 空间会留有许多空洞。 虽然 Montevina 平台提供了 256 MB 的 PCIe 设备使 用的配置空间, 但是这些空间的实际利用率较低。 PowerPC 处理器也可以使用 ECAM 方式映射 PCI 配置空间, 如 MPC8548 处理器可以使 用 PCIe 桥中的 Outbound 寄存器 ( PEXOWARn) 将 PCI 配置空间映射到存储器域。 此外 PowerPC 处理器还可以使用 PEX _CFG _DATA 和 PEX _CFG _ADDR 这两个寄存器访问

总结

简单的理解一下Montevina平台

参考文章:

PCI_Express_体系结构导读——王齐

2507

2507

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?