一、FPGA引脚文件

UG586-Zynq-7000 All Programmable SoC Packaging and Pinout (Advanced Product Specification)详细介绍了Zynq-7000 AP SoC的封装于引脚布局和配置信息,同时还包括引脚定义、Bank信息、机械图纸、引脚布局以及其他关于与Zynq-7000接口相关的详细信息。

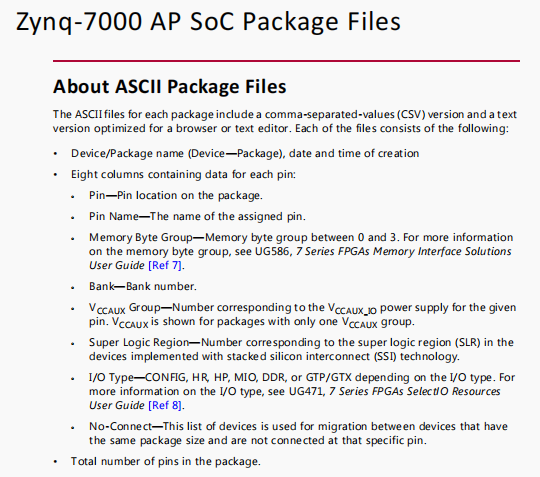

在UG865文档的第26页,提到了ASCII引脚文件,以下是文档中关于ASCII引脚文件的描述:

ASCII引脚文件是一种文本文件,它以ASCII编码格式列出了FPGA所有引脚及其相关信息。这些信息包括引脚的位置、名称、所属的内存字节组、Bank编号、电源组、超级逻辑区域、I/O类型以及是否为无连接引脚等。ASCII格式的文件易于阅读和解析,可以方便地在文本编辑器或浏览器中查看,也便于进行自动化处理和分析。以XC7Z020-1CLG484C设备为例,演示如何找到引脚文件。

第一步,执行关键词检索 。输入"XC7Z020-1CLG484C “ASCII” "进行检索,确保输入时使用双引号,以精确匹配该型号的ASCII引脚文件 。

第二步,在搜索结果中,找到标题与内容与下图相符的条目,确认无误后点击进入(Zynq 7000 SoC Package Devices Pinout Files (xilinx.com))详细页面。

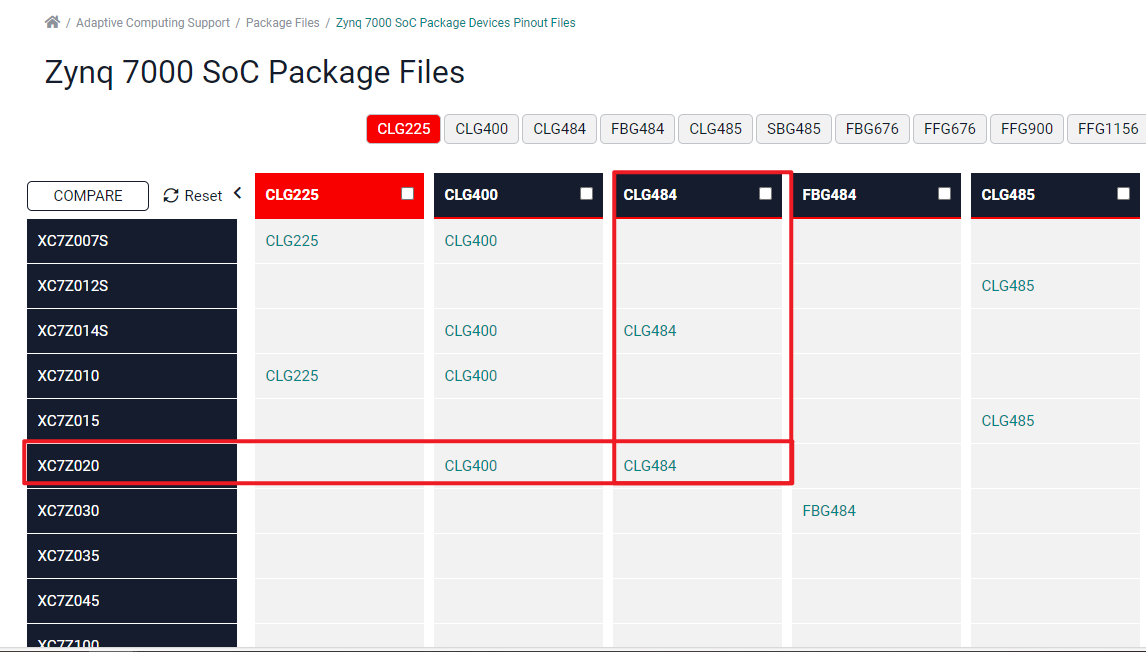

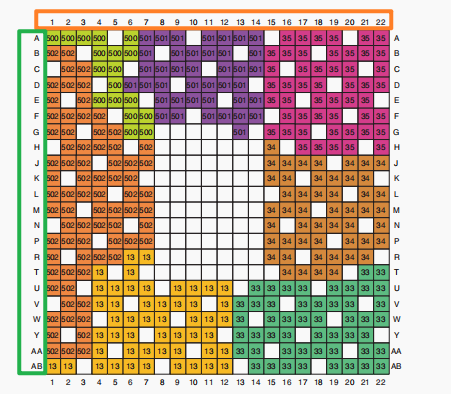

第三步,通过读取表格的行、列信息便可找到目标芯片的型号,如下图行列交叉位置即为XC7Z020-1CLG484C,点击打开便可获取引脚文件。

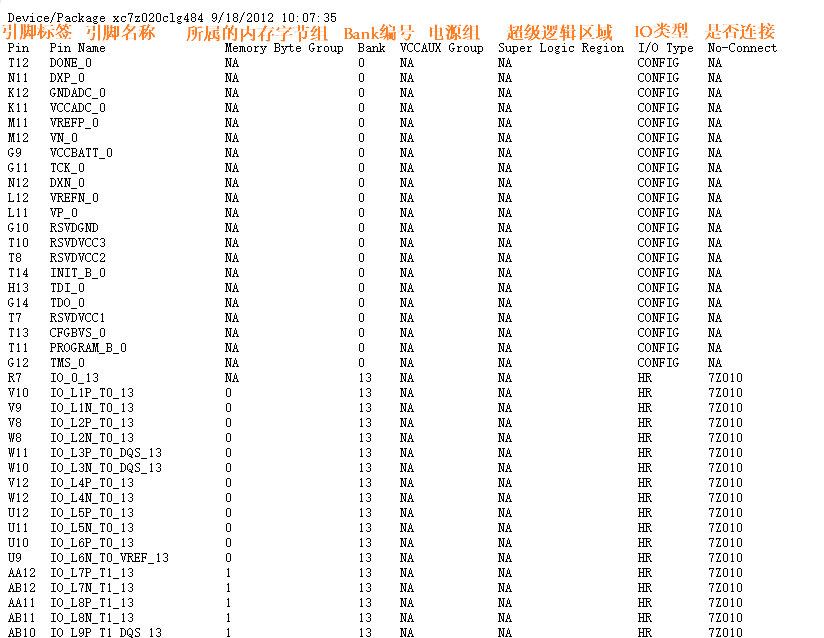

引脚文件展示:

二、引脚标签(Pin)

FPGA芯片引脚的物理位置标识。引脚的标签由字母和数字组成, 字母为行,数字为列。封装的详细布局图,见UG586-Zynq-7000 All Programmable SoC Packaging and Pinout (Advanced Product Specification),41页。

三、引脚名称(pin Name)

用于描述了引脚的功能和特性,如电气特性、信号类型、所属的信号组或功能模块。引脚名称定义可能比较长且复杂,可按照功能和用途进行分类:

| 引脚类型 | 描述 |

|---|---|

| Reserved Pin–保留引脚 | 为特定的功能保留的引脚,如配置、时钟输入、JTAG接口等,不能被用户配置为其他用途。 |

| Special Pin–特殊引脚 | 具有特殊功能或用途的引脚,如模拟输入、ADC输入、温度传感器等。 |

| Programmable Logic(PL)Pin–可编程逻辑引脚 | 可编程逻辑部分(PL)的一部分,可以被配置为多种不同的功能,如GPIO、时钟、差分信号等。 |

| Processing System(PS)Pin–处理系统引脚 | 与Zynq-7000 AP SoC的处理系统部分相关的引脚,通常用于连接处理系统中的外设,如DDR内存、SPI接口、I2C接口等。 |

| Mutli-IO(MIO) Pin–多功能I/O引脚 | 可配置的I/O引脚,可以被映射到不同的PS外设,如UART、GPIO、SPI等。 |

| Configuration Pin–配置引脚 | 用于初始化FPGA配置,包括JTAG(边界扫描)接口和配置时钟引脚。 |

| Power and Ground Pin–电源和地引脚 | 为Zynq-7000 AP SoC提供必要的电源和接地。 |

也可按照信号属性来分类:

| 信号属性分类 | 描述 |

|---|---|

| I/O Type (输入/输出类型) | 引脚支持输入和输出功能。Xilinx有时有仅输入的引脚,所以要注意这些。 |

| Differential Pair (差分对) | 表示这是一个差分信号的正输入P或N负输入。差分信号对于提高信号的抗干扰能力、传输速度和可靠性非常有用。 |

| 有效电平 | 后缀B表示低电平有效 |

不同功能和用途的Pin Name的定义方式,会有些差异:

(1)保留引脚定义

Bank0中的所有特殊保留引脚。

- GNDADC, VCCADC:这是XADC在AMS系统中的参考地和参考电源。

- VREFP, VREFN:这是Bank0的输入阈值电压。

- VCCBATT:这是解密器电池供电电压。如果你不使用解密器,你可以安全地将其拉到GND。

- DXN, DXP:这些是温度感应二极管引脚。这个二极管访问可以用来监测温度,尽管根据UG865,你应该使用XADC内的温度传感器而不是这个二极管。

- VP, VN:这是构成XADC第17个输入的正和负模拟输入。

- RSVDGND, RSVDVCC#:这些是专用引脚。RSVDGND必须保持未连接,RSVDVCC[3:1]必须拉到VCCO_0(银行0电压)。

- CFGBVS:这个引脚决定了配置Bank(Bank0)将运行在什么电压。如果拉高,它将是3.3V/2.5V操作,或者如果拉低,它将是1.8V操作(这对于低功耗应用很好)。

- INIT_B, PROGRAM_B, DONE:这些信号在编程FPGA时使用。

- TCK, TDI, TDO, TMS:这些信号组成了JTAG接口。JTAG是一种边界扫描技术,允许FPGA被编程和接口。

(2)特殊引脚(Special Pin)

- DQS:DQS是数据选通信号,用于DDR存储器的读或写操作。这个信号在DDR存储的数据传输起着关键作用,确保数据的同步和准确性。

- VREF:VREF是DDR存储器的一个参考电压,通常设置为DDR供电电压的一半,即1/2 VDD电压。这个参考电压用于DDR存储器的校准,确保数据传输的准确性。

- SRCC, MRCC:这两个引脚与时钟用于时钟信号输入和输出有关,有助于减少时钟的偏斜和抖动。这对于提高系统性能和稳定性非常重要。

- PUDC_B:PUDC_B引脚用于控制FPGA所有IO引脚在上电的状态。如果这个引脚被拉低,所有IO口将被上拉至高电平,如果引脚被拉低,则所有IO口引脚将处于浮空,由外部负载将决定。这种配置可以确保系统在上电时的稳定性。PUDC_B引脚属于Bank 0组。

- **AD#P/N:**是Zynq-7000 AP SoC中的XADC(模数转换器)输入引脚。这些引脚的命名中包含“#”,这里的“#”代表一个从0到15的数字。每个引脚会被标记为“P”或“N”,但不会同时标记为两者。这些引脚构成了32个单端信号输入,或者16个差分信号输入,它们连接到AMS(模拟混合信号)模块的输入端。XADC(模数转换器)能够将这些模拟信号数字化,并将数据读入可编程逻辑(PL)中,同时也可以被处理系统(PS)读取。这些功能使得这些引脚在设计中非常实用和强大。

(3)PL引脚的定义(PL Pin Deffintions)

分解一个典型的PL引脚定义,例如“V10 -I0_L1P_T0_13”:

- IO:表示脚支持输入和输出功能。需要注意的是,FPGA有些引仅有输入的功能。

- L1P:表示这是一个差分信号的正输入。差分信号有助于提高信号的抗干扰能力,传输速度和可靠性。这里的"L1"表示差分对1,而“P”表示正极。

- T0:与存储器控制器的软IP相关,7系列设备有软IP存储器控制器,用于与各种存储器设备接口。然而,它们依赖于IO结构内的原语,需要在特定位置的IOBank中放置。

- 13:表示该引脚所在的IO Bank编号。

PL引脚定义命名方案:

<Input/Output Definition>

注意:引脚可以有多个特殊功能,并且会简单地用下划线(_)连接在一起。

(4)PS引脚定义(PS Pin Definitions)

- CLK:PS系统的主输入时钟。

- VREF:PS的DDR的参考电压。

- MIO#: "MIO"代表多功能IO引脚池,这些引脚可供处理系统(PS)的外设映射使用。存在一个复用机制,它允许不同的PS外设根据需要映射到这些MIO引脚上。引脚的命名方式是“MIO#”,这里的“#”代表一个从0到53的数字。这些引脚的映射配置可以通过EDK GUI(嵌入式开发套件)的图形用户界面进行设置。这样的设计提供了灵活的IO资源配置,以适应不同的设计需求。

- **SRST_B:**这是PS的复位引脚。这个引脚用于重置处理器核心。

- DDR_*😗*Zynq-7000的PS使用了大量的DDR信号。在这里,我不会一一介绍它们,但它们包括控制信号、数据线和地址线。

PS引脚定义的命名方案:

PS_<MIO Number, Function, or Special Feature>_

PS(Processor System)和PL(Programmable Logic)是两个不同的部分,它们在处理系统中的功能和位置也有所不同。

- PS通常负责处理器的运行和管理,包括指令执行、内存访问、输入输出控制等。它通常位于处理系统的核心区域,与处理器和其他关键组件直接相连。

- PL则专注于可编程逻辑电路的设计和实现,如数字信号处理、模拟信号转换、存储器管理等。它通常位于处理系统的边缘区域,通过AMBA总线或其他接口与PS连接。

四、Memory Byte Group-内存字节组

“Memory Byte Group”(内存字节组),可以帮助我们快速识别引脚在DDR存储器接口中属于哪个字节组。在Zynq-7000系列SoC中,内存字节组的概念与DDR存储器接口的布局有关。每个DDR引脚在DDR存储器接口中负责传输一个字节的数据,而这些引脚通常被组织成多个字节组。

在Zynq-7000 SoC的数据表中,提供了关于内存字节组的详细信息,包括每个引脚在DDR存储器接口中的位置和它们所属的字节组。这些信息对于确保DDR存储器接口的正确配置和优化数据传输效率至关重要。

例如,如果一个引脚被标记为属于特定的内存字节组,那么在配置DDR存储器接口时,设计人员需要确保相应的数据路径和控制信号正确地映射到这个字节组上。这种配置有助于提高系统的性能和数据传输的可靠性。

五、Bank

Bank是一组具有相似电气特性的引脚,而每个Bank可能支持不同的电源电压,例如,一些Bank可能支持1.2V至1.8V的电压,而其他Bank可能支持更高的电压,如2.5V或3.3V;不同的信号标准,例如如LVCMOS、LVDS、HSTL等;不同的电气特性,例如不同的输入输出特性,如驱动强度、摆率控制等。以XC7Z020-1CLG484C为例,Bank0组的所属引脚按照功能和用途分属于配置引脚(Configuration Pin),BanK500则属于可编程逻辑引脚(PL)。设计人员可以通过IO Bank编号便可确认引脚的电气特性和设计要求,而IO也指示了引脚在芯片封装上的物理位置.

六、I/O类型

有五种不同的I/O类型:

- CONFIG:此类型是为上述保留引脚描述部分中描述的配置引脚保留的。

- HR:HR代表高范围。这些Bank允许从1.2V到3.3V的电压。这些允许非常宽的输入范围的I/O电压,这非常方便。

- **HP:**HP代表高性能。这些I/O设计用于与高速存储器接口和其他高速数字数据传输。这些Bank只支持高达1.8V的I/O。

- MIO:这些是PS可以路由其外设的可配置(可复用)I/O引脚。哪些外设可以连接到哪些引脚有限制。此外,并非所有外设都可以同时带出,因为有比MIO引脚更多的外设。

- DDR:这些引脚与PS上的DDR存储器接口。

七、No-Connec

由于这些引脚在7010和7020之间(或7030和7045之间)不存在,若无迁移计划,这些引脚对设计而言无关紧要,可以忽略。

836

836

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?