搞定锁存器和触发器(SR、D、T、JK)

开胃小菜——基本双稳态电路

双稳态存储电路:简称双稳态电路,具有0、1两种逻辑状态,一旦进人其中一种状态,就能长期保持不变的单元电路

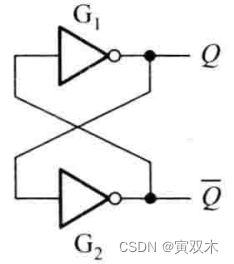

将两个非门G1和G2接成如图所示的交叉耦合形式,则构成最基本的双稳态电路。

从图所示电路的逻辑关系可知,

若

Q

=

0

Q = 0

Q=0 ,经非门G2反相,则

Q

‾

=

1

\overline{Q} = 1

Q=1 。

$ Q $ 反馈到G1输人端,又保证了

Q

=

0

Q = 0

Q=0 。

由于两个非门首尾相接的逻辑锁定,因而电路能自行保持在

Q

=

0

,

Q

‾

=

1

Q = 0,\overline{Q} = 1

Q=0,Q=1 的状态,形成第一种稳定状态。

反之,若

Q

=

1

,

Q

‾

=

0

Q = 1,\overline{Q} = 0

Q=1,Q=0 ,则形成第二种稳定状态。

在两种稳定状态中,输出端

Q

Q

Q 和

Q

‾

\overline{Q}

Q 总是逻辑互补的。

可以定义

Q

=

0

Q = 0

Q=0 为整个电路的0状态,

Q

=

1

Q = 1

Q=1 则是1状态。

电路进人其中任意一种逻辑状态都能长期保持下去,并可以通过Q端电平检测出来

因此,它具有存储1位二进制数据的功能。

锁存器

锁存器(Latch)是一种对脉冲电平敏感的双稳态电路,它具有0和1两个稳定状态,一旦状态被确定,就能自行保持

直到有外部特定输人脉冲电平作用在电路一定位置时,才有可能改变状态。这种特性可以用于置入和存储1位二进制数据。

1、SR锁存器

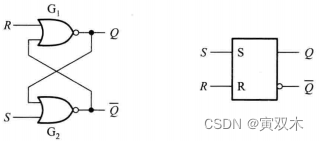

1.1 或非门SR锁存器

将双稳态电路的非门换成 或非门(都是0时为1) ,则构成基本或非门SR锁存器

逻辑电路 & 逻辑符号:

S

S

S 和

R

R

R 是两个输人端,

Q

Q

Q 和

Q

‾

\overline{Q}

Q 是两个输出端

定义

Q

=

0

Q = 0

Q=0 和

Q

‾

=

1

\overline{Q} = 1

Q=1,为锁存器的0状态

Q

=

1

Q = 1

Q=1 和

Q

‾

=

0

\overline{Q} = 0

Q=0 ,为锁存器的1状态

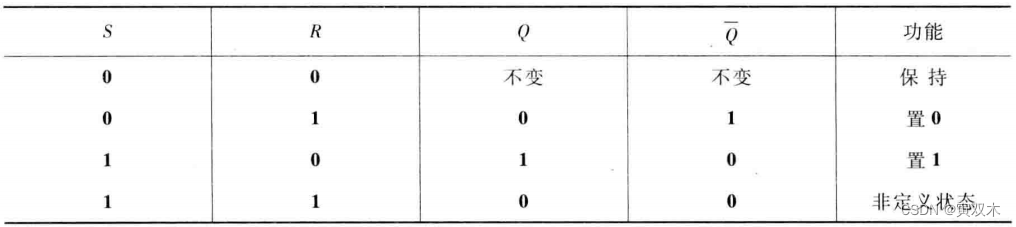

输出输入状态表:

S = 0 ,R = 1 (0状态)

对于或非门而言,S=0 不会影响 G2 的输出状态

如果电路初始为1状态,即

Q

=

1

Q = 1

Q=1 、

Q

‾

=

0

\overline{Q} = 0

Q=0

R=1 作用于G1,则

Q

=

R

+

Q

‾

‾

=

1

+

0

‾

=

0

Q = \overline{R + \overline{Q}} = \overline{1 + 0} = 0

Q=R+Q=1+0=0

反馈到G2,则

Q

‾

=

S

+

Q

‾

=

0

+

0

‾

=

1

\overline{Q} = \overline{S + Q} = \overline{0 + 0} = 1

Q=S+Q=0+0=1

电路状态翻转,翻转为0状态

假如初始状态为0状态,即

Q

=

0

Q = 0

Q=0 和

Q

‾

=

1

\overline{Q} = 1

Q=1

R=1 作用于G1,则

Q

=

R

+

Q

‾

‾

=

1

+

1

‾

=

0

Q = \overline{R + \overline{Q}} = \overline{1 + 1} = 0

Q=R+Q=1+1=0

反馈到G2,则

Q

‾

=

S

+

Q

‾

=

0

+

0

‾

=

1

\overline{Q} = \overline{S + Q} = \overline{0 + 0} = 1

Q=S+Q=0+0=1

状态没有发生改变,保持0状态

最终状态:0状态

S = 1 ,R = 0 (1状态)

同理可推算

最终状态:1状态

S = R = 0 (不起作用)

Q

=

R

+

Q

‾

‾

=

0

+

Q

‾

‾

=

Q

Q = \overline{R + \overline{Q}} = \overline{0 + \overline{Q}} = Q

Q=R+Q=0+Q=Q

Q

‾

=

S

+

Q

‾

=

0

+

Q

‾

=

Q

‾

\overline{Q} = \overline{S + Q} = \overline{0 + Q} = \overline{Q}

Q=S+Q=0+Q=Q

显然,

S

S

S 和

R

R

R 对信号

Q

Q

Q 和

Q

‾

\overline{Q}

Q 不起作用,电路保持不变

S = R = 1(非定义状态)

无论

Q

Q

Q 和

Q

‾

\overline{Q}

Q 原来是什么状态,S=R=1将强制

Q

=

R

+

Q

‾

‾

=

1

+

Q

‾

‾

=

0

Q = \overline{R + \overline{Q}} = \overline{1 + \overline{Q}} = 0

Q=R+Q=1+Q=0

Q

‾

=

S

+

Q

‾

‾

=

1

+

Q

‾

=

0

\overline{Q}= \overline{S + \overline{Q}} = \overline{1 + Q} = 0

Q=S+Q=1+Q=0

锁存器处在既非1,又非0的非定义状态。

若S和R同时回落到0,则无法确定回落瞬间,锁存器将落人1状态还是0状态

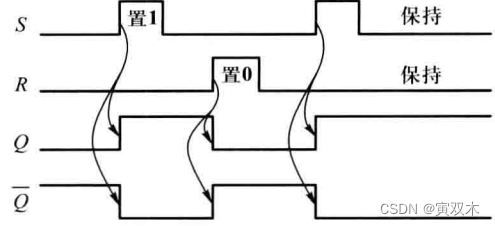

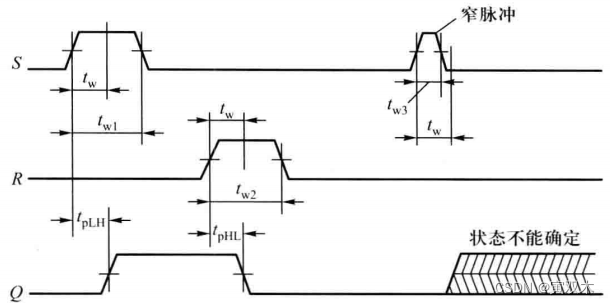

SR锁存器的典型工作波形:

SR锁存器的定时图:

定时图是表达时序电路动态特性的工具之一

它表达了电路动作过程中,输出对输人信号响应的 延迟时间 ,以及对各输人信号的时间要求

图中,脉冲信号的上升沿和下降沿均用斜线表达,表示存在一定的 上升时间 和 下降时间

脉冲沿的基准时间定位在 上升沿和下降沿的50% 处。

其中,传输延迟时间

t

p

L

H

t_{pLH}

tpLH 和

t

p

H

L

t_{pHL}

tpHL ,脉冲宽度

t

w

t_w

tw

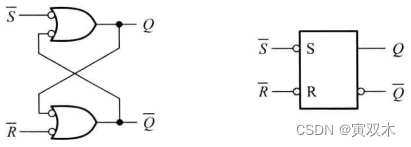

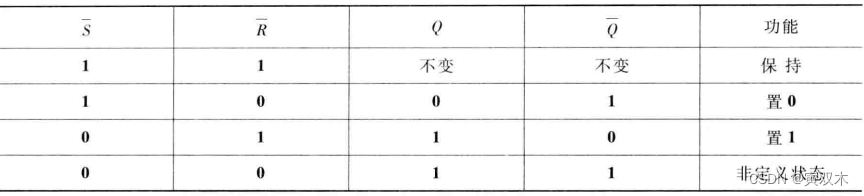

1.2 与非门SR锁存器

将双稳态电路的非门换成 与非门(都是1时为0) ,则构成基本与非门SR锁存器

逻辑电路 & 逻辑符号:

输出输入状态表:

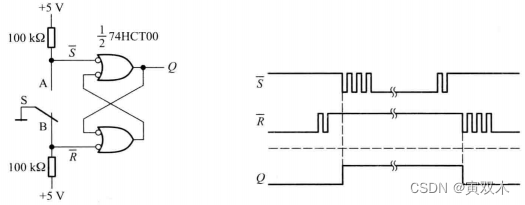

应用:

用 基本SR锁存器 构成 机械开关 去抖动电路

电路以及波形图:

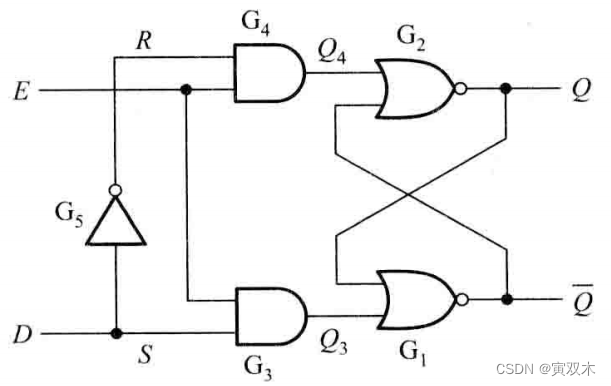

1.3 门控SR锁存器

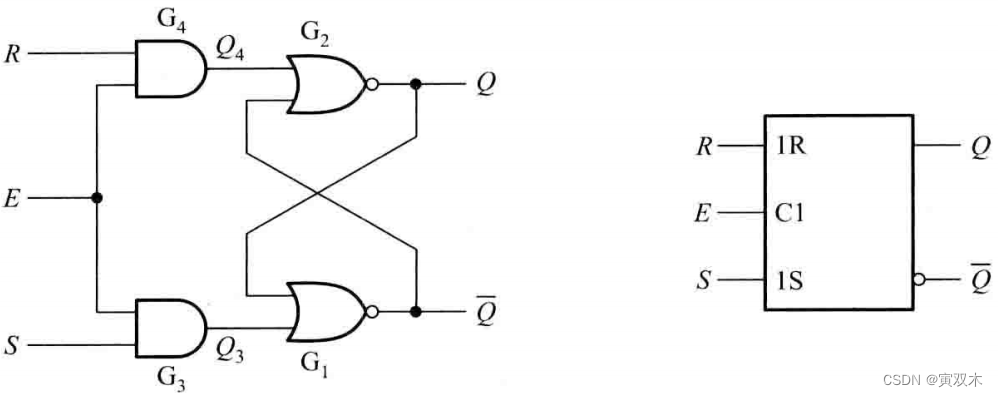

逻辑电路 & 逻辑符号:

当

E

=

0

E = 0

E=0 时,

Q

3

=

Q

4

=

0

Q3 = Q4 = 0

Q3=Q4=0,S、R端的逻辑状态不会影响到锁存器的状态;

当

E

=

1

E =1

E=1 时,S、R端的信号被传送到基本SR锁存器的输人端,从而可确定

Q

Q

Q 和

Q

‾

\overline{Q}

Q 端的状态,其功能跟或非门SR锁存器一致

PS:前缀后缀

如上图所示是门控SR锁存器的逻辑符号,其方框内用C1和1R、1S表达内部逻辑之间的关联关系。

C表示这种关联属于控制类型,其后缀用标识序号“1”表示:该输人的逻辑状态对所有以“1"作为前缀的输入起控制作用。

因置位和复位输入均受C1的控制,故S和R之前分别以标识序号“1”作为前缀。

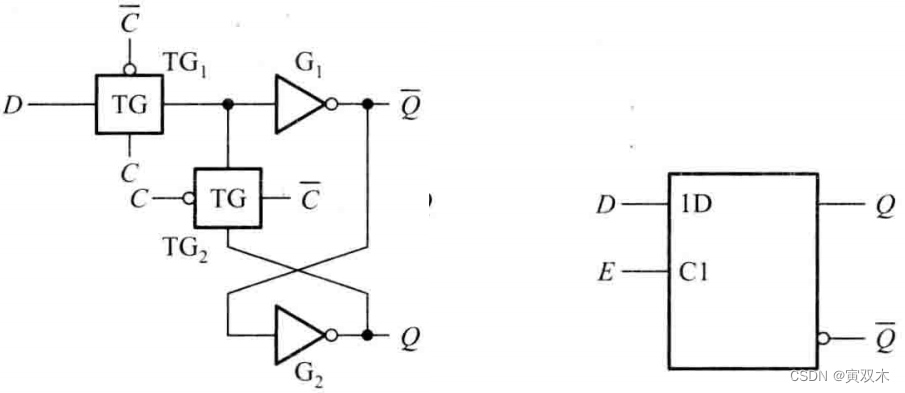

2、D锁存器

2.1 传输门控D锁存器

双稳态电路中插人两个传输门TG1和TG2,则可构成传输门控D锁存器

逻辑电路 & 逻辑符号:

D锁存器有两个输人端:使能端E和数据输人端D。

D锁存器有两个输人端:使能端E和数据输人端D。

当E = 0时,C = 1,C = 0,TG1断开,TG2导通,如右图所示,其原理与双稳态电路相同。

当E = 1时,C = 0,C = 1,TG1导通,TG2断开,如左图所示,输入数据D经G1、G2两个非门,使

Q

=

D

Q = D

Q=D ,

Q

‾

=

D

‾

\overline{Q} = \overline{D}

Q=D。

显然,Q端跟随输入信号D的变化。

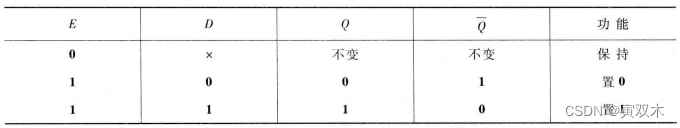

功能表:

2.2 逻辑门控D锁存器

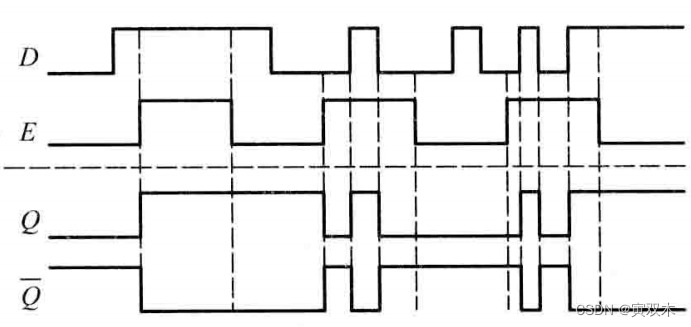

逻辑门控D锁存器的逻辑电路:

逻辑门控D锁存器的的波形图:

在门控SR锁存器的S和R输人端之间连接了一个非门G5,从而保证了SR=0的约束条件,消除了可能出现的非定义状态。

仿照前面的分析方法,你会发现,它的逻辑功能与传输门控D锁存器完全相同,所以逻辑符号亦相同。

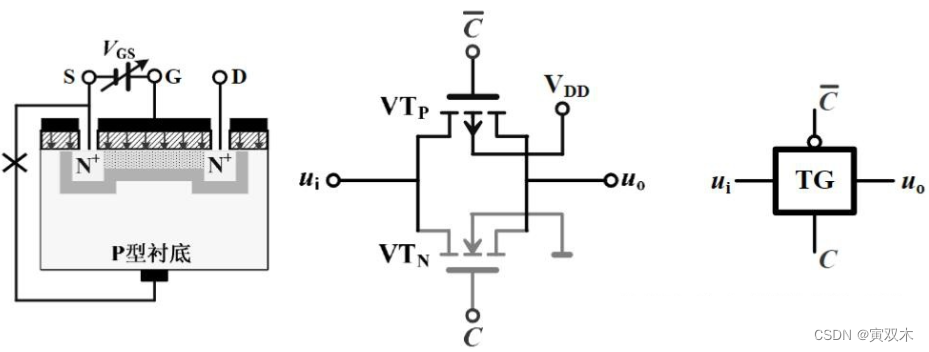

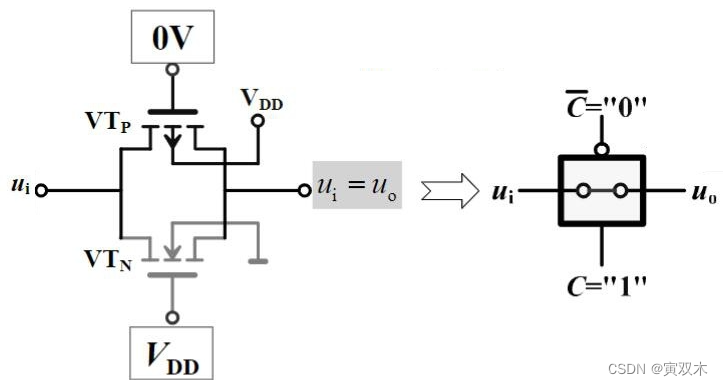

PS:传输门

概念

在MOS管中,源极与衬底间的连接已被断开,PMOS管的衬底与高电平紧密结合,而NMOS管的衬底则与低电平相连

这两晶体管的栅极,连接着一对互补的控制信号

C

C

C 及其反相信号

C

‾

\overline{C}

C

通过精确调节栅极与衬底间的电压差,实现了对导电沟道电阻状态的精密控制,进而决定了电流的流通与否

将俩个MOS管的源极、漏极直接相连作为输入端子、输出端子

这种MOS管的漏极和源极完全可以互换使用,因而这种电路的输入端与输出端也可以互换

这便是具有信号传输双向特性的CMOS传输门,简称TG门

原理分析

1、当C端接入低电平(0V), C ‾ \overline{C} C 端接入高电平( V D D V_{DD} VDD )

两个MOS晶体管的 栅极与衬底 之间的电压差为0,不会在晶体管中形成导电沟道。

无论是NMOS晶体管还是PMOS晶体管,都将处于截止状态。

传输门的输入端和输出端之间将表现出高阻抗状态,导致传输门整体截止。

2、当C端接入高电平(

V

D

D

V_{DD}

VDD ),

C

‾

\overline{C}

C 端接入低电平(0V)

两个MOS晶体管的 栅极与衬底 之间的电压差大于晶体管开启压降,在晶体管的漏极和源极之间形成导电沟道。

NMOS晶体管 和 PMOS晶体管,都将处于导通状态。

传输门的输入端和输出端之间将表现出低阻状态,传输门相当于导通

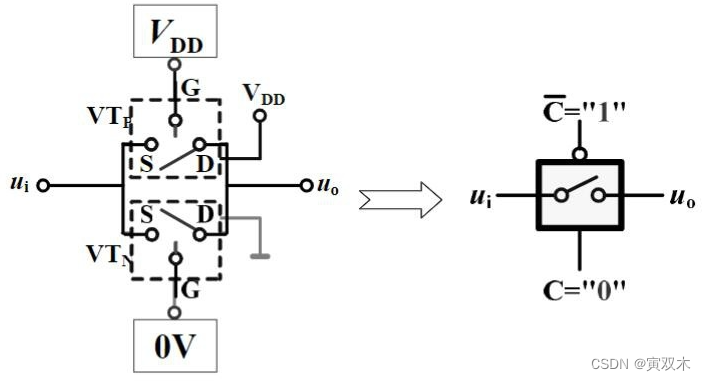

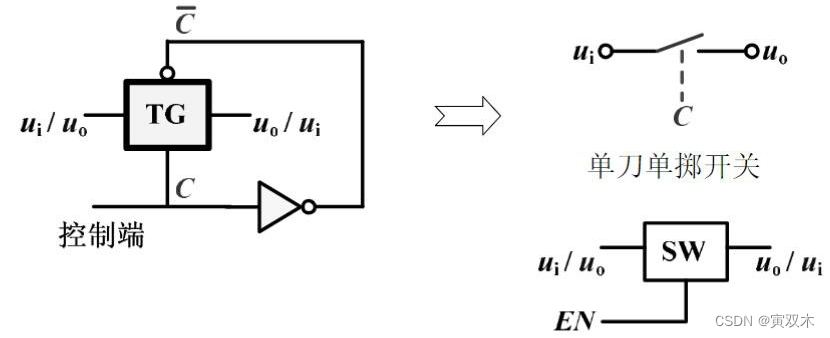

传输门单刀单掷开关

逻辑电路 & 逻辑符号:

使用 CMOS反相器 提供一对互补的控制信号,将传输门设计成 可控单刀单掷开关 。

在此电路符号中,标记为

E

N

EN

EN 的端子代表模拟开关的使能控制端。

当使能端接收 高电平信号 时,模拟开关导通,允许信号通过;

当使能端接入 低电平信号 时,模拟开关断开,阻断信号流通。

触发器

很多时序电路要求存储电路只对时钟信号的上升沿或下降沿敏感,而在其他时刻保持状态不变。

对时钟脉冲边沿敏感的状态更新称为触发,具有触发工作特性的存储单元称为触发器。

目前应用的触发器主要有三种电路结构: 主从触发器 、 维持阻塞触发器 和 利用传输延迟的触发器。

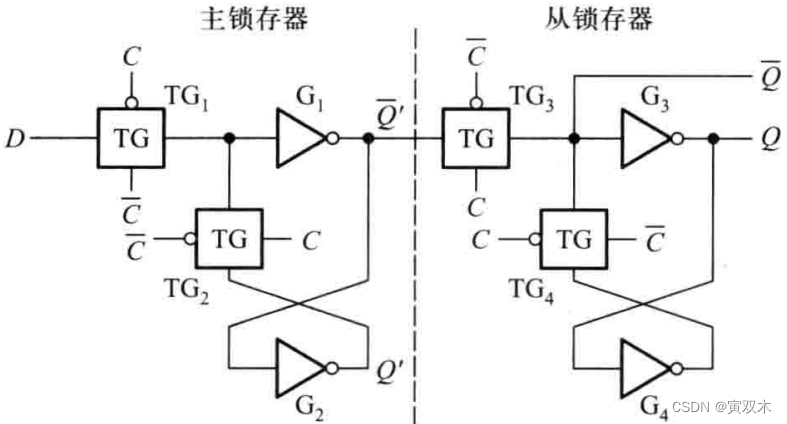

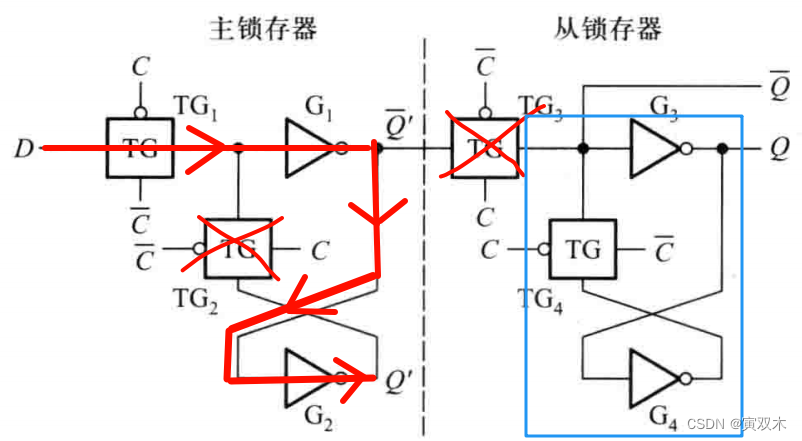

1、电路结构——主从触发器(以DC触发器为例)

由于CMOS主从结构的D触发器在芯片上占用的面积最小,逻辑设计方法也较简单,在大规模CMOS集成电路得到普遍应用,因而在目前的工程实践中也会更多地面对这种D触发器

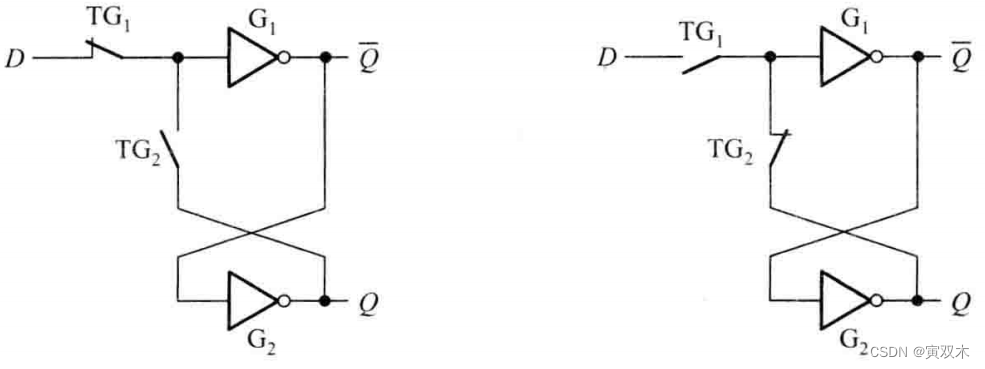

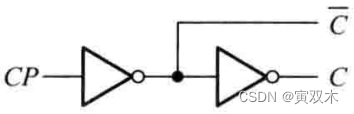

CMOS主从D触发器的逻辑电路:

将两个D锁存器级联,则构成典型的CM0S主从D触发器,

图中左边的锁存器称为主锁存器,右边的称为从锁存器。

主锁存器与从锁存器的使能信号相位相反

利用两个锁存器的交互锁存,则可实现存储数据和输人信号之间的隔离。

(1)、CP = 0

C

‾

=

1

\overline{C} = 1

C=1 ,

C

=

0

C=0

C=0,使TG1导通,TG2断开,D端输人信号进人主锁存器,这时Q’跟随D端的状态变化,使

Q

′

=

D

Q'=D

Q′=D 。

同时由于TG3断开,切断了从锁存器与主锁存器之间的联系,而TG4导通,使G3的输人端和G4的输出端经TG连通,构成最基本的双稳态电路,使从锁存器维持原来的状态,即触发器的输出状态不变。

故而此时,主锁存器处, D D D 经过两个非门出入到 Q ′ Q' Q′处( Q ′ = D Q'=D Q′=D ),从锁存器是一个基本的双稳态电路

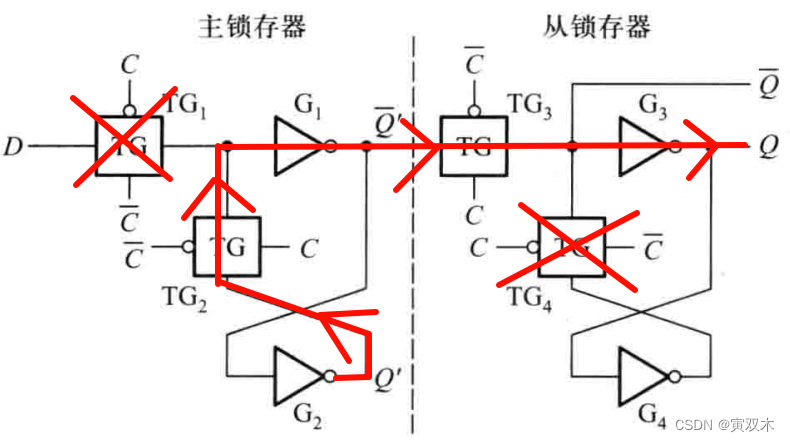

(2)、CP:0→1

C

‾

=

0

\overline{C} = 0

C=0 ,

C

=

1

C=1

C=1,使TG1断开,从而切断了D端与主锁存器的联系,

同时TG2导通,将G1的输人端和G2的输出端连通,主锁存器锁存CP跳变前D端的数据。

这时,TG3导通,TG4断开,Q’端信号传送到Q端。

若

Q

′

=

1

Q'=1

Q′=1 ,

Q

′

‾

=

0

\overline{Q'} = 0

Q′=0 ,经TG3传送给G3的输人端,于是

Q

=

1

Q=1

Q=1 ,

Q

‾

=

0

\overline{Q} = 0

Q=0

故而此时,

Q

′

Q'

Q′ 经过两个非门输出(

Q

=

Q

′

Q = Q'

Q=Q′ ,即

Q

=

D

Q = D

Q=D )

2、触发器的逻辑功能

触发器在每次时钟触发沿到来之前的状态称为现态,之后的状态称为次态。

触发器的逻辑功能:以输入信号和现态为变量,以次态为函数的逻辑关系,用特性表、特性方程或状态图来描述这种关系。

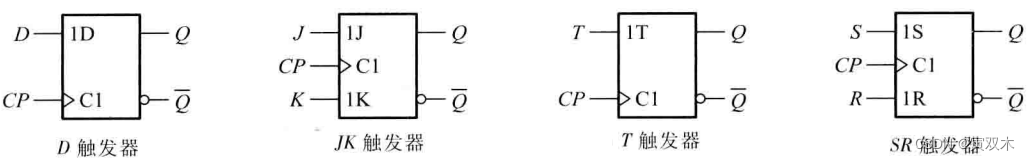

按照触发器的逻辑功能,通常分为D触发器、JK触发器、T触发器和SR触发器等几种不同类型。

1.特性表

以输人信号和触发器的现态为变量,以次态为函数,描述它们之间逻辑关系的真值表称为触发器的特性表。

2.特性方程

触发器的逻辑功能也可以用逻辑表达式来描述,称为触发器的特性方程

3.状态图

触发器的功能还可以用状态图更为形象地表示

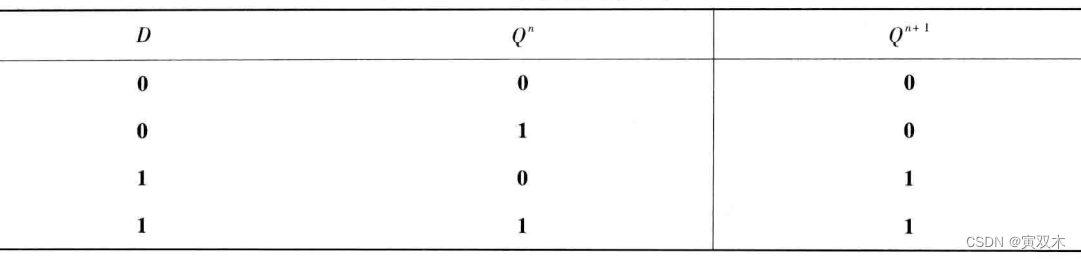

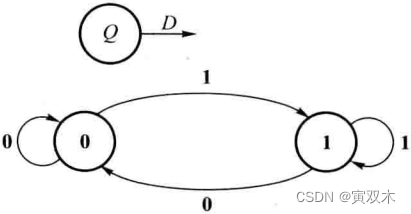

1、D触发器

D触发器特性方程: Q n + 1 = D Q^{n+1}=D Qn+1=D

D触发器特性表:

输人信号D 和 现态Qn 的每种组合都列出了相应的 次态Qn+1

D触发器状态图:

可以由D触发器的特性表导出。

图中,

圆圈内数据: 为触发器的状态Q,分别标示为0和1,代表了触发器的两个状态;

4根带箭头的方向线: 表示状态转换的方向,分别对应特性表中的4行,

方向线的起点: 为触发器的现态

Q

n

Q^n

Qn

箭头指向: 相应的次态

Q

n

+

1

Q^{n+1}

Qn+1;

方向线旁边数据: 标出了状态转换的条件,即输入信号D的逻辑值

由特性表、特性方程或状态图均可看出,

当D=0时,D触发器的下一状态将被置0( 即

Q

n

+

1

=

0

Q^{n+1}=0

Qn+1=0 );

当D=1时,将被置1( 即

Q

n

+

1

=

1

Q^{n+1}=1

Qn+1=1)。

在时钟脉冲的两个触发沿之间,触发器状态保持不变,即存储1位二进制数据。

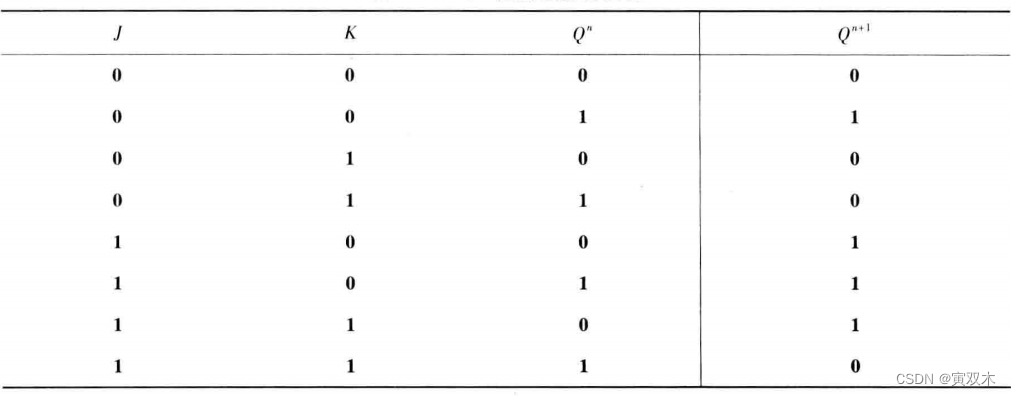

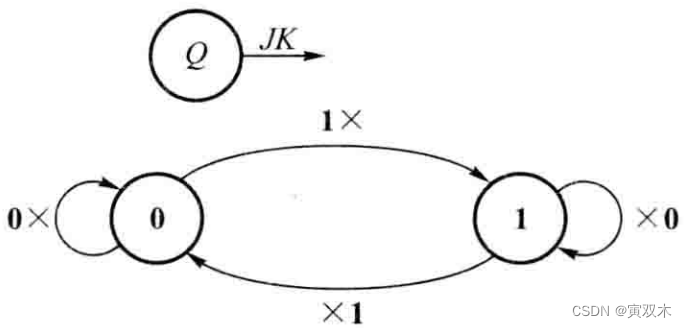

2、JK触发器

JK触发器特性方程: Q n + 1 = J Q n ‾ + K ‾ Q n Q^{n+1} = J\overline{Q^{n}} +\overline{K}Q^n Qn+1=JQn+KQn

JK触发器特性表:

输人信号J、K 和 现态Qn 的每种组合都列出了相应的 次态Qn+1

JK触发器状态图:

它有两个输人变量,每根方向线旁都标有两个逻辑值,分别为

J

、

K

J、K

J、K 的值。

在每一个转换方向上,J、K中总有一个是无关变量。

例如,JK触发器特性表第5行和第7行,

Q

n

=

0

Q^{n}=0

Qn=0 转换为

Q

n

+

1

=

1

Q^{n+1}=1

Qn+1=1

条件是

J

=

1

J = 1

J=1,而

K

K

K 既可以取0,也可以取1

状态图中的转换条件则以1x表示。

所以,状态图中的4根方向线实际对应表中8行。

综上所述,

当

J

=

K

=

0

J=K=0

J=K=0 时,JK触发器状态保持不变(

Q

n

+

1

=

Q

n

Q^{n+1}=Q^{n}

Qn+1=Qn)

当

J

=

0

,

K

=

1

J=0,K=1

J=0,K=1 时,触发器的下一状态将被置0(

Q

n

+

1

=

0

Q^{n+1}=0

Qn+1=0)

当

J

=

1

,

K

=

0

J=1,K=0

J=1,K=0 时,将被置1(

Q

n

+

1

=

Q

n

Q^{n+1}=Q^{n}

Qn+1=Qn)

当

J

=

K

=

1

J=K=1

J=K=1 时,触发器的下一状态将翻转(

Q

n

+

1

+

=

Q

n

‾

Q^{n+1}+=\overline{Q^{n}}

Qn+1+=Qn)。

在所有逻辑类型的触发器中,JK触发器具有最强的逻辑功能

在外部

J

、

K

J、K

J、K 信号控制下,它能执行 保持 、 置0 、 置1 和 翻转 四种操作

并可用简单的附加电路转换为其他功能的触发器。

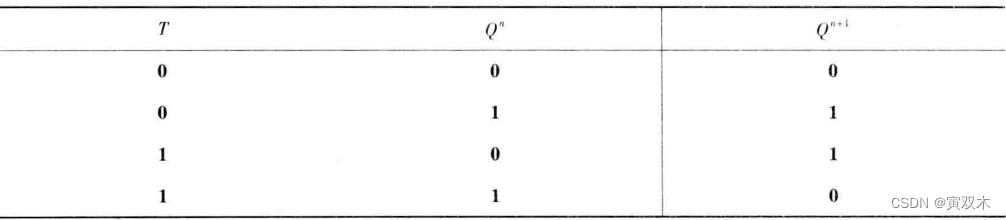

3、T触发器

T触发器特性方程: Q n + 1 = T Q n ‾ + T ‾ Q n Q^{n+1} =T\overline{Q^{n}}+\overline{T}Q^n Qn+1=TQn+TQn

T触发器特性表:

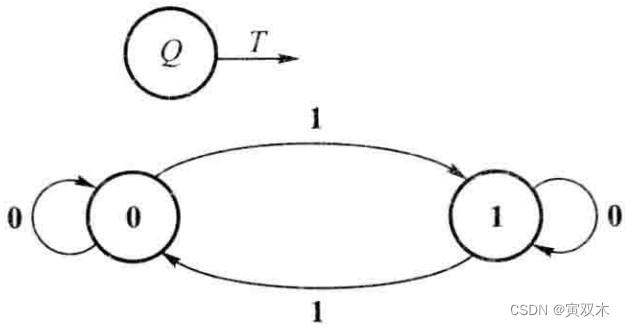

T触发器状态图:

T触发器的功能是

T

=

1

T=1

T=1 时为翻转状态,

Q

n

+

1

=

Q

n

‾

Q^{n+1} = \overline{Q^{n}}

Qn+1=Qn

T

=

0

T=0

T=0 时为保持状态,

Q

n

+

1

=

Q

n

Q^{n+1} = Q^{n}

Qn+1=Qn

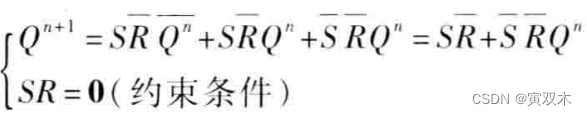

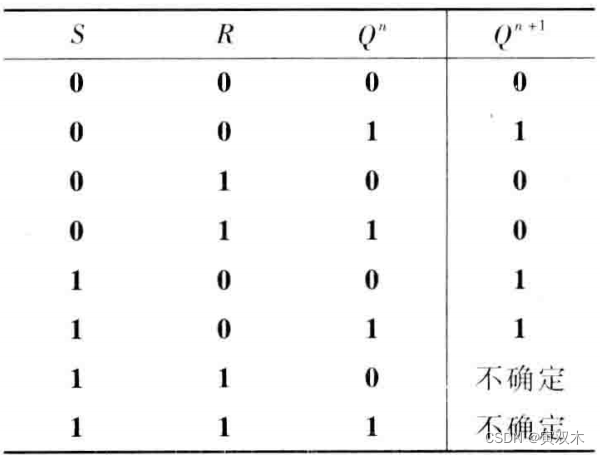

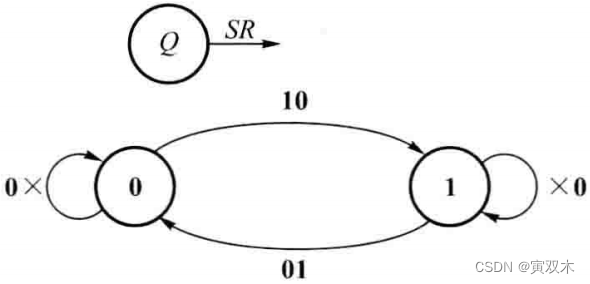

4、SR触发器

SR触发器特性方程: Q n + 1 = S + R ‾ Q n Q^{n+1} = S + \overline{R}Q^n Qn+1=S+RQn(约束条件: S R = 0 SR = 0 SR=0 )

由于

S

=

R

=

1

S=R=1

S=R=1 时,触发器的次态是不能确定的,触发器可能将失去控制,SR触发器的使用必须遵循SR=0的约束条件

化简得,SR触发器特性方程:

Q

n

+

1

=

S

+

R

‾

Q

n

Q^{n+1} = S + \overline{R}Q^n

Qn+1=S+RQn(约束条件:

S

R

=

0

SR = 0

SR=0 )

SR触发器特性表:

SR触发器状态图:

3、扩展:D触发器逻辑功能的转换

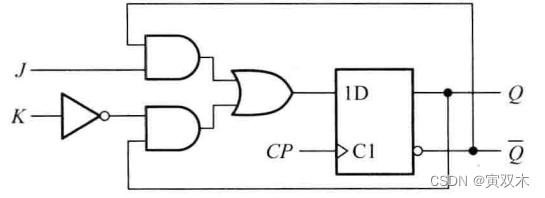

D 触发器 构成 JK 触发器

特性方程: Q n + 1 = D = J Q n ‾ + K ‾ Q n Q^{n+1} = D = J\overline{Q^{n}} +\overline{K}Q^n Qn+1=D=JQn+KQn

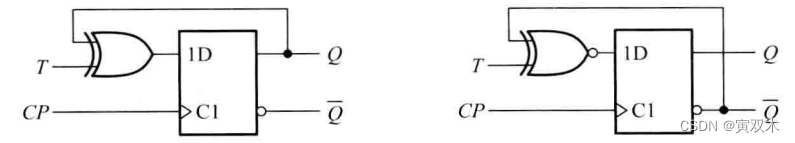

D 触发器 构成 T 触发器

特性方程: Q n + 1 = D = T Q n ‾ + T ‾ Q n = T ⨁ Q n = T ⨀ Q n ‾ Q^{n+1} = D =T\overline{Q^{n}}+\overline{T}Q^n = T\bigoplus Q^n = T\bigodot \overline{Q^n} Qn+1=D=TQn+TQn=T⨁Qn=T⨀Qn

只需在D输人端前增加一个异或门或者同或门即可实现两种T触发器逻辑电路

PS:动态特性

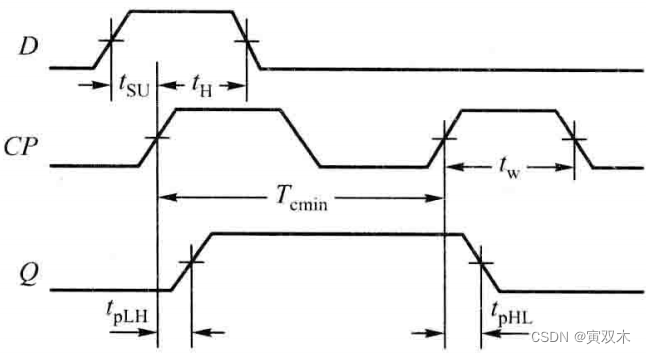

定时图

定时图显示了CP上升沿触发的D触发器的动态特性

它反映了输出对时钟信号响应的延迟时间,以及对输人逻辑信号和时钟信号的定时要求。

传输延迟时间 t p d t_{pd} tpd

时钟脉冲

C

P

CP

CP 上升沿至输出端新状态稳定建立起来的时间定义为D触发器的传输延迟时间。

t

p

L

H

tpLH

tpLH 是输出Q从低电平到高电平的延迟时间

t

p

H

L

tpHL

tpHL 则是Q从高电平到低电平的延迟时间

平均传输延迟时间

“

t

p

d

=

(

t

p

L

H

+

t

p

H

L

)

/

2

”

“t_{pd}=(t_{pLH} + t_{pHL})/ 2”

“tpd=(tpLH+tpHL)/2” (应用更多)

建立时间 t s u t_{su} tsu

输入信号D的变化会引起触发器内部电路逻辑电平的一系列变化

为保证相关电路建立起稳定的状态,信号D必须提前于时钟信号CP的上升沿(对上升沿触发的触发器而言)就稳定在指定的逻辑电平上

以确保使触发器状态得到正确的转换。该提前时间的最小值即建立时间su。

保持时间 t H t_H tH

信号

D

D

D 在

C

P

CP

CP 上升沿到来之后,仍需保持一定时间来保证D状态可靠地传送到

Q

Q

Q 和

Q

‾

=

0

\overline{Q} = 0

Q=0 ,该时间的最小值称为保持时间

由于技术的进步,已有多种触发器把保持时间几乎降到0

这项特性在高速移位寄存器或计数器中是十分重要的

触发脉冲宽度 t W t_W tW

为保证可靠触发,要求时钟脉冲CP的宽度不小于 t W t_W tW ,以保证内部门电路有足够的时间实现正确的翻转。

最高时钟频率 f c m a x f_{cmax} fcmax

触发器所能响应的时钟脉冲

C

P

CP

CP 的最高频率,

f

c

m

a

x

=

1

/

T

e

m

i

n

f_{cmax} = 1/T_{emin}

fcmax=1/Temin。

C

P

CP

CP 无论在高电平还是在低电平期间

触发器内部要完成一系列动作,都存在一定的时间延迟

所以对于

C

P

CP

CP 最高工作频率有一个限制。

┈┈┈┈▕▔╲┈┈┈┈┈┈┈ ┈┈┈┈▕▔╲┈┈┈┈┈┈┈ ┈┈┈┈▕▔╲┈┈┈┈┈┈┈┈

┈┈┈┈┈▏▕┈┈┈┈┈┈┈ ┈┈┈┈┈▏▕┈┈┈┈┈┈┈ ┈┈┈┈┈▏▕┈┈┈┈┈┈┈ ┈

┈┈┈┈┈▏ ▕▂▂▂▂▂┈┈┈┈┈┈┈▏ ▕▂▂▂▂▂┈┈┈┈┈┈┈▏ ▕▂▂▂▂▂┈┈┈

▂▂▂▂╱┈┈▕▂▂▂▂▏┈ ▂▂▂▂╱┈┈▕▂▂▂▂▏┈ ▂▂▂▂╱┈┈▕▂▂▂▂▏┈┈

▉▉▉┈┈┈┈▕▂▂▂▂▏ ┈ ▉▉▉┈┈┈┈▕▂▂▂▂▏ ┈ ▉▉▉┈┈┈┈▕▂▂▂▂▏ ┈

▉▉▉┈┈┈┈▕▂▂▂▂▏ ┈ ▉▉▉┈┈┈┈▕▂▂▂▂▏ ┈ ▉▉▉┈┈┈┈▕▂▂▂▂▏ ┈

▔▔▔▔╲▂▂▕▂▂▂▂▏┈ ▔▔▔▔╲▂▂▕▂▂▂▂▏┈ ▔▔▔▔╲▂▂▕▂▂▂▂▏┈┈

3089

3089

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?