基本原则(Reg)

组合=

时序<=

1.连续赋值

组合b=a;c=b; === c=b=a === a->b->c导线 / c=b;b=a; === b->c a->b移位器(不推荐!)

时序b<=a;c<=b; === b1=a0;c1=b0; === a->b b->c移位器

2.生效时刻

组合: 当场有效

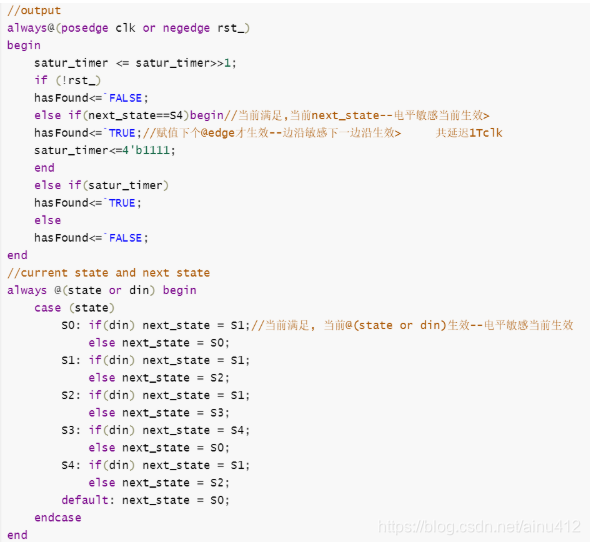

时序:下一时钟沿有效(~@沿计算,@沿赋值)

=阻塞, if条件满足时数据暂存(|1), 待下次敏感表满足(|2)有效

3.覆盖

1)线网用assign =, 后来者覆盖

2)延时

C<= #5 A+B 内定并行不覆盖(并行全输出)<->C= #5 A+B 正规并行覆盖(旧的阻塞占位期间忽视新)

#5 D<=A+B == #5 D=A+B 立即运算覆盖(触发到点时刻最新)

3)多次赋值

y<=a;

y<=b;

以后一个为准

4.本质

非阻塞: 所有的右端表达式RHS1、RHS2…在进程开始时同时计算,计算完毕后 ,等进程结束时同时分别赋给左端变量LHS1、LHS2…;

阻塞赋值语句在每个右端表达式计算完后立即赋给左端变量,即赋值语句LHS1=RHS1执行完后LHS1是立即更新的,且只有LHS1=RHS1执行完后才可执行语句LHS1=RHS2.

4641

4641

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?