目标功能:ZYNQ--PL与PS通过AXIBRAM读写交互实现(含PL读写和PS读写及相关交互控制执行)。具体如下:实现对0XA000 F000为起始地址的读写操作,PL端一直读取0XA000 F000为起始地址的4个32位数据,VITIS中PS端通过AXI4向BRAM写数据,当PS写进BRAM中0XA000 F001的数据为1或2时,PL端实时读到0XA000 F001中数据为1时,LED灭掉,读到为2时LED亮起,同时PL端往BRAM中0XA000 F000地址往后写8个数据(5、6、7、8、9、A、B、C),VITIS中PS端通过AXI4读取BRAM中0XA000 F000为起始地址的16个数据,以此验证PL读写和PS读写及相关交互控制执行。此测试可作为PS应用程序发指令,PL端解析指令并执行相应操作,PL通过BRAM向PS实时发送数据的项目雏形。

实现平台:米联客MLK-CM02-2CG(A)

性能参数:PS DDR4--1GB DDR4(单片512MB*2片),数据带宽2400MHz*32Mbit;PL DDR4无;EMMC无;FLASH无。

原理框图:

1、详细参考《3-1-01米联客2022版Ultrascale+ MPSOC系列FPGA课程基础篇》中10.4 搭建 SOC 系统工程章节,严格按照此章节搭建PS最小系统,其中新手有疑惑的地方如下:

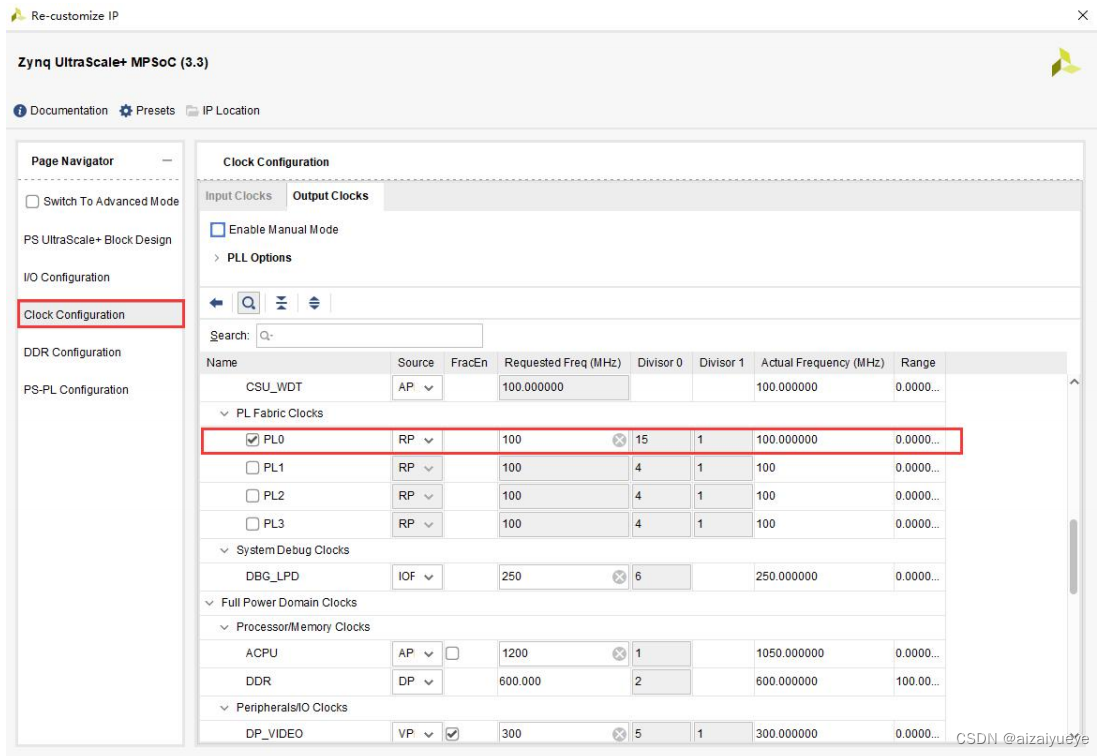

按照教程走到配置时钟这一步时会看不到下面那么多外设的时钟,如下图所示,不要慌,只有再配置完PS-PL configration后才会出现。

按照教程往下配置,可顺利实现PS最小系统的搭建。

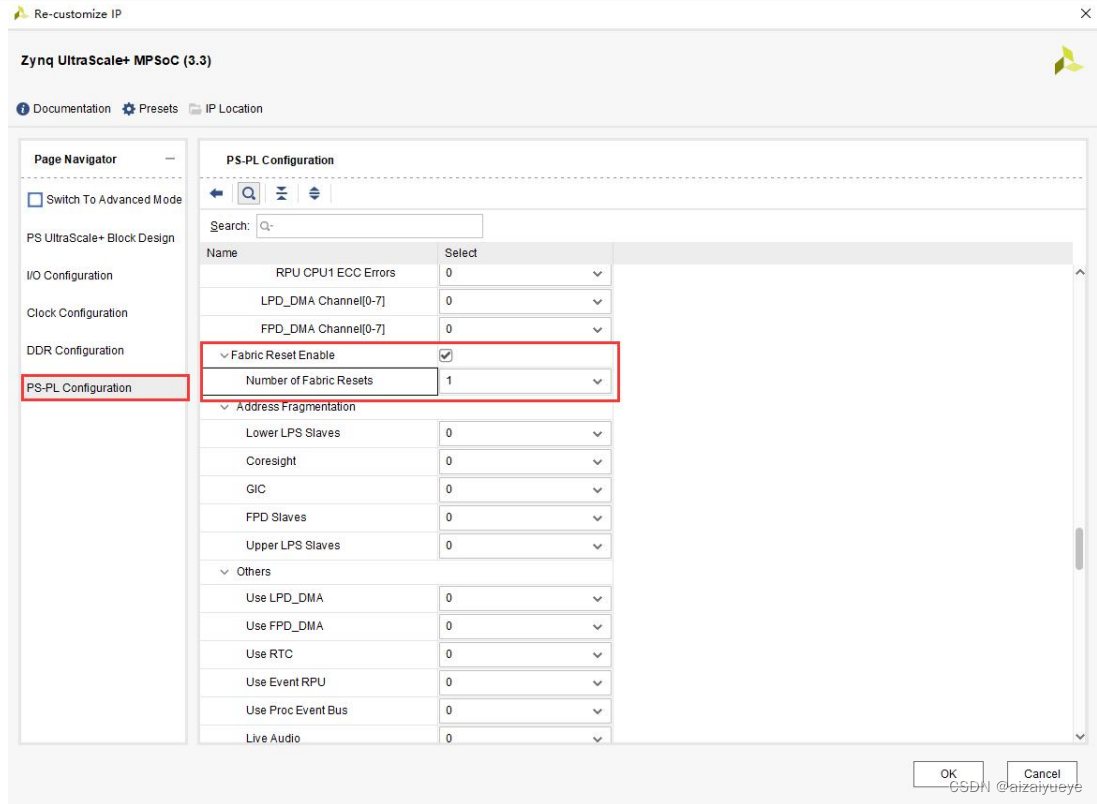

2、此次实现我们的PL端将采用PS给出的时钟pl_clk0和复位pl_rstn信号,注意是内部信号。因此需要在Zynq IP PS 中进行以下部分设置。

(1)PS 复位设置

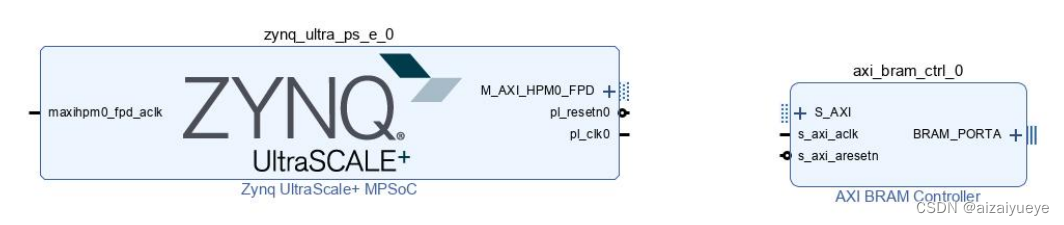

(2)设置 AXI HPM0 FPD 接口设置

(3)设置 PL 的时钟

勾选 FCLK_CLK0,设置为 100,即 PS 的 PLL 提供本系统的时钟 100MHZ。

3、BD文件配置

(1)添加 IP

单击添加 IP 按钮“+ ”,输入如下模块 IP 名字的关键词,并双击添加。

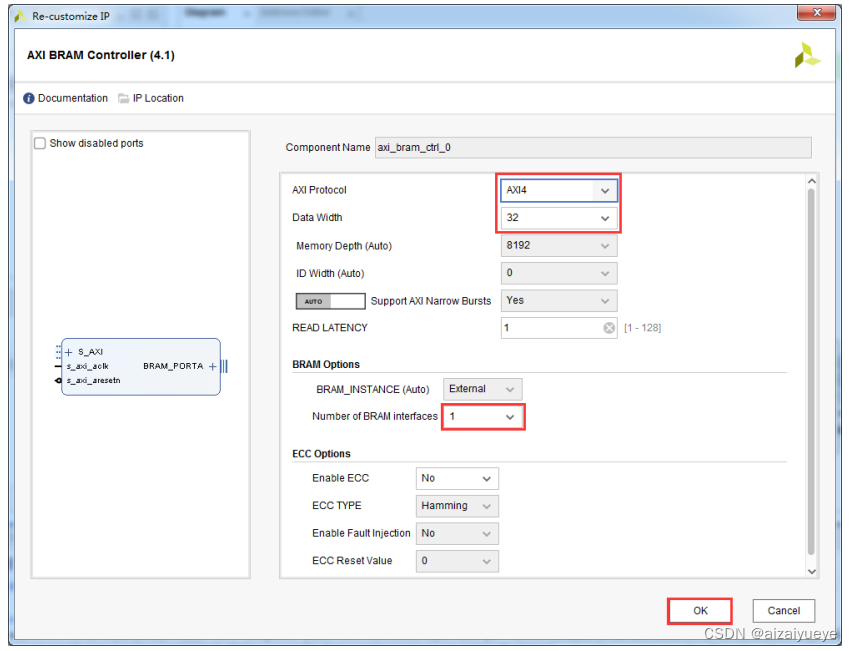

(2)axi_bram_ctrl_0设置

添加完成后,双击 AXI BRAM Controller IP 核,打开其配置界面如下图所示:

上图中,AXI Protocol(AXI 协议)选择AXI4,Data Width(数据位宽)选择32位,由于AXI4总线为字节寻址,因此在映射到BRAM地址时, 需要按4字节寻址。本次项目的BRAM控制器只需要读写BRAM的一个端口,因此将BRAM的总线个数设置为1;ECC选项用于数据错误纠正与检查,这里不使能。需要说明的是,Memory Depth(存储深度)在这里不可以设置,寻址BRAM的存储深度是在Address Editor

本文介绍了ZYNQ FPGA项目中,如何实现PL与PS通过AXIBRAM的读写交互。具体操作包括配置PS最小系统、设置时钟和复位、搭建BRAM控制器与IP核、编写PL端功能模块代码,以及利用ILA进行调试。通过PS写入特定数据,PL端实时响应并执行相应操作,验证了读写交互的正确性。

本文介绍了ZYNQ FPGA项目中,如何实现PL与PS通过AXIBRAM的读写交互。具体操作包括配置PS最小系统、设置时钟和复位、搭建BRAM控制器与IP核、编写PL端功能模块代码,以及利用ILA进行调试。通过PS写入特定数据,PL端实时响应并执行相应操作,验证了读写交互的正确性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

815

815

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?