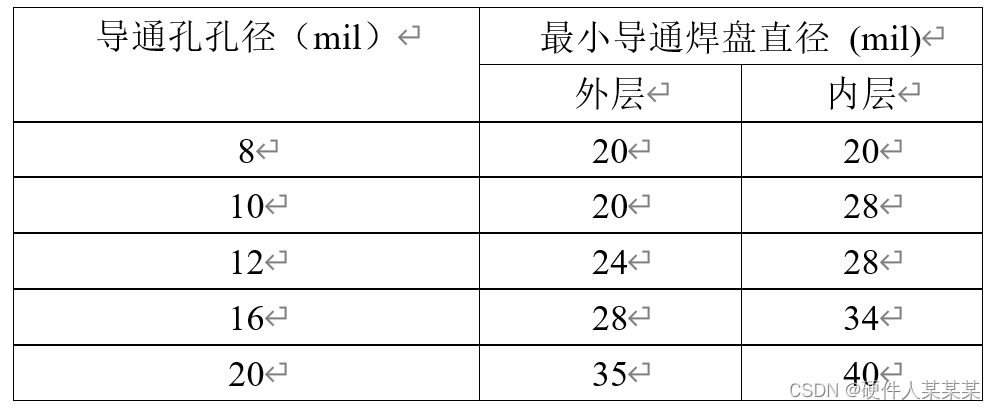

过孔焊盘

导通孔(via)焊盘尺寸

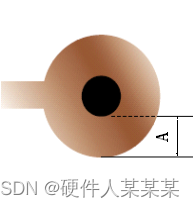

a) 外层焊盘环宽(A)要大于5mil,内层焊盘环宽(A)要大于8mil, 推荐导通孔孔径及焊盘尺寸如下:

b) 推荐反焊盘大小尺寸≥过孔焊盘+20MIL。

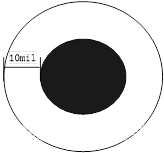

走线与金属化孔间的最小间隙

推荐的走线距金属化孔最小间隙 © 是8mil;

内层走线距金属化孔最小间隙极限值 © 为4mil;

表层走线距金属化孔最小间隙极限值 © 为5mil;

PCB的通流能力

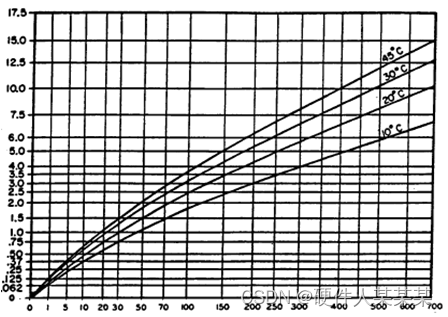

可以用以下的两张图表,计算不同的温升温度,铜箔的通流能力。这里讲的温升温度,指的是设备的工作温度和室温的温度差。在以下条件下,要做降额处理:

a) 考虑到PCB的铜箔厚度的制造公差,走线宽度的制造公差,降额10%。

b) 板厚小于0.8mm,或者铜箔厚度大于108um, 降额15%。

外层通流能力 X:铜箔的截面积 (mil2)Y:电流(安培)

内层通流能力 X:铜箔的截面积(mil)Y:电流(安培)

6877

6877

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?