前言

学习说明此文档为本人的学习笔记,注重实践,关于理论部分会给出相应的学习链接。

学习视频:是根据野火FPGA视频教程——第二十一讲

https://www.bilibili.com/video/BV1nQ4y1Z7zN?p=3

理论学习

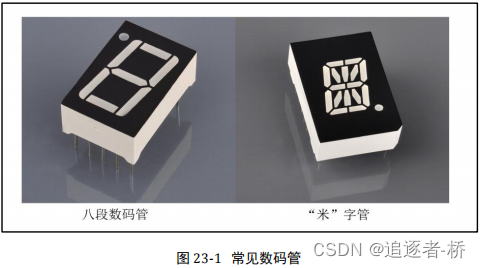

1、数码管简介

最常见的数码管为八段数码管,七段数码管比八段少了一个·,还又米型数码管等。

2、八段数码管

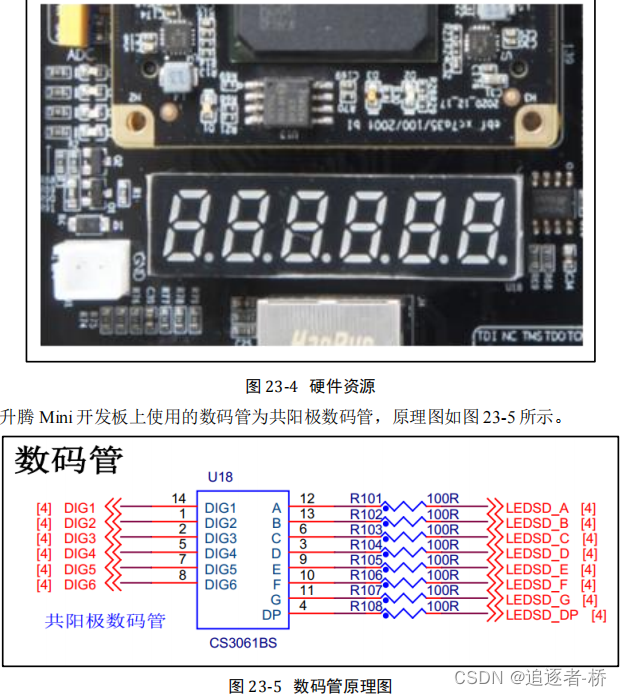

本次实验使用的是共阳极数码管,也就是说给对应段低电平才会被点亮。给不同的段点亮可显示 0~f 的值,如表格 23-1 所示。

![]()

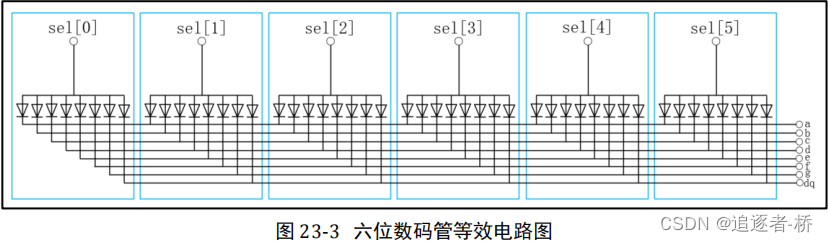

6段8位数码管的连接为:

上图abcdefg和aq同时控制6段数码管,

当sel控制6段数码管同时显示,此时为静态显示。

如果使用 sel控制6段数码管在不同时显示不同的数字,此时为动态显示。

静态显示实战演练

一、设计规划

1.1 实验目标

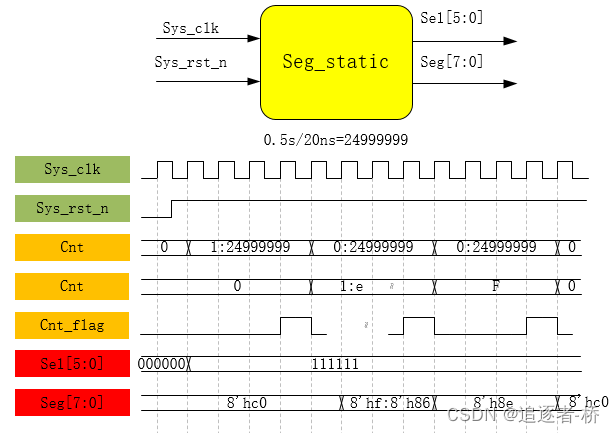

设计6位数码管静态显示:实现6位数码管从000000——FFFFFF循环显示,每个字符显示0.5s后变化。

优点类似于流水灯了,循环显示。

1.2 硬件资源

二、程序设计

2.1 波形图绘制

由于有0.5s的时间变化,因此使用到了计数器。可以使用状态机的思想进行编码,在时间到达后显示下一状态的值。

2.2 代码编写

module seg_static

#(

parameter CNT_MAX = 25'd24999999

)

(

input wire sys_clk,

input wire sys_rst_n,

output reg [5:0] sel,

output reg [7:0] seg

);

reg [24:0] cnt;

reg [3:0] data;

reg cnt_flag;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt <= 1'b0;

else if(cnt == CNT_MAX)

cnt <= 1'b0;

else

cnt <= cnt + 1'b1;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

data <= 1'b0;

else if(cnt_flag == 1'b1 && data == 4'd15)

data <= 1'b0;

else if(cnt == CNT_MAX)

data <= data + 1'b1;

else

data <= data;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_flag <= 1'b0;

else if(cnt == CNT_MAX - 1)

cnt_flag <= 1'b1;

else

cnt_flag <= 1'b0;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

sel[5:0] <= 6'b000000;

else

sel[5:0] <= 6'b111111;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

seg[7:0] = 8'hc;

else case(data)

4'd0 : seg[7:0] <= 8'hc0;

4'd1 : seg[7:0] <= 8'hf9;

4'd2 : seg[7:0] <= 8'ha4;

4'd3 : seg[7:0] <= 8'hb0;

4'd4 : seg[7:0] <= 8'h99;

4'd5 : seg[7:0] <= 8'h92;

4'd6 : seg[7:0] <= 8'h82;

4'd7 : seg[7:0] <= 8'hf8;

4'd8 : seg[7:0] <= 8'h80;

4'd9 : seg[7:0] <= 8'h90;

4'd10: seg[7:0] <= 8'h88;

4'd11: seg[7:0] <= 8'h83;

4'd12: seg[7:0] <= 8'hc6;

4'd13: seg[7:0] <= 8'ha1;

4'd14: seg[7:0] <= 8'h86;

4'd15: seg[7:0] <= 8'h8e;

default : seg[7:0] <= 8'hc;

endcase

endmodule

三、逻辑仿真

3.1 仿真代码

`timescale 1ns / 1ps

//

// Company: 追逐者——桥的小作坊

// Create Date: 2022/05/18 21:20:48

// Design Name: 静态数码管显示

// Module Name: tb_seg_static

//

module tb_seg_static();

reg sys_clk;

reg sys_rst_n;

wire [5:0] sel;

wire [7:0] seg;

initial begin

sys_clk = 1'b1;

sys_rst_n = 1'b0;

#20

sys_rst_n = 1'b1;

end

always #10 sys_clk = ~ sys_clk;

//重新定义参数

defparam seg_static_inst.CNT_MAX = 10;

seg_static seg_static_inst

(

.sys_clk (sys_clk ),

.sys_rst_n(sys_rst_n),

.sel (sel ),

.seg (seg )

);

endmodule

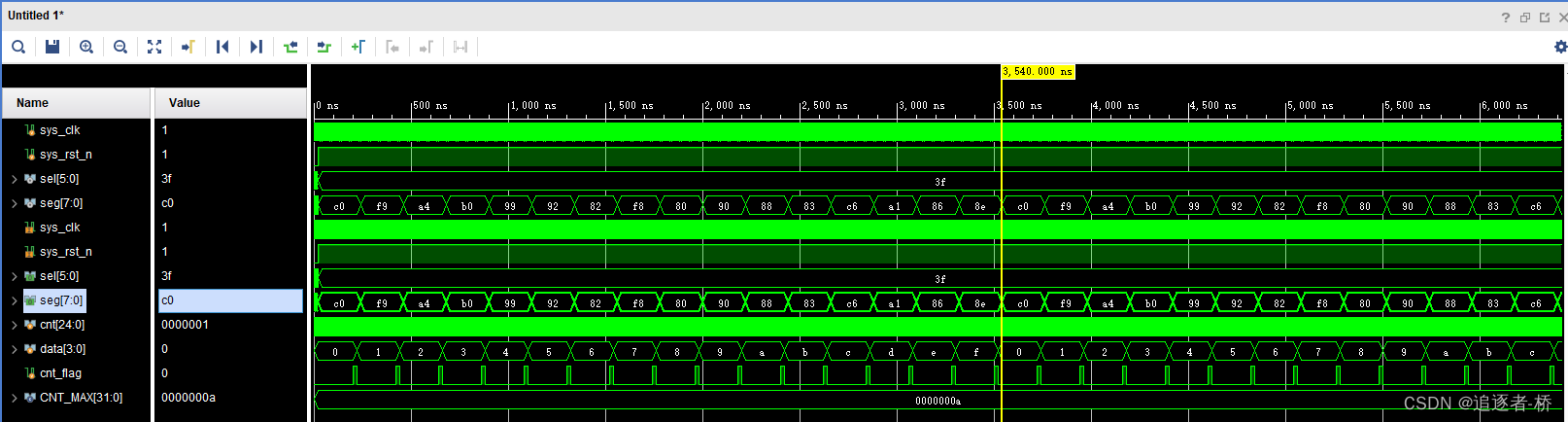

3.2 仿真波形对比

与绘制波形对比可知,与绘制的相同。

四、上板验证

四、上板验证

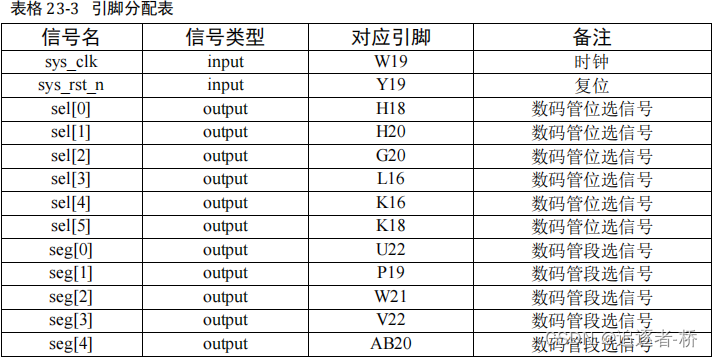

4.1 管脚绑定

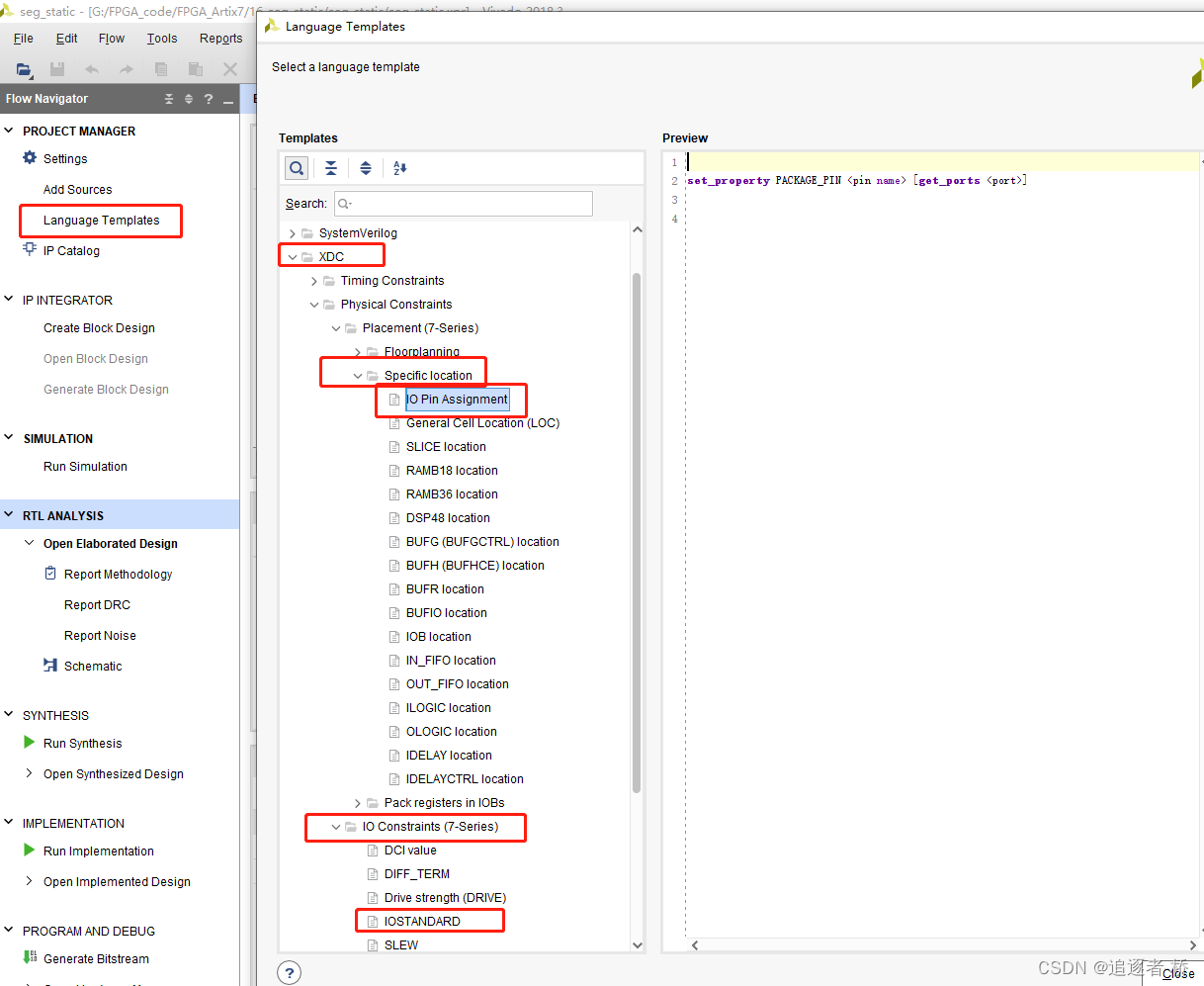

XDC文件的编写:找到约束文件原语

4.2 上板验证

FPGA——静态数码管显示实验

五、总结

和单片机的数码管控制基本类似,就是这里的时间需要自己根据时钟计数器设置,且称为触发条件。

1467

1467

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?