长期以来,双倍数据速率(DDR)内存一直是个人电脑中作为主存的主导地位。最近,它在嵌入式系统中的使用也越来越多。让我们来看看DDR接口的基础知识。

DDR接口需要每个DRAM芯片通过几条数据线将数据传输到内存控制器。这些数据流伴随着strobe信号。由于数据可以从控制器流向DRAM(写入操作)和从DRAM流向控制器(读取操作),这些数据线本质上是双向的。

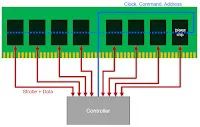

常见的时钟、命令和地址服务于所有DRAM芯片。由于这些控制接口的操作,它们在控制器和DRAM之间是单向的。下图说明了从DDR3标准开始使用的“fly by”拓扑结构。

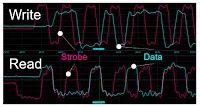

DDR是“双数据速率”内存,因为数据传输的timing:一个字节在时钟的上升沿传输,另一个字节在时钟的下降沿传输。时钟以DDR数据速率的一半运行,并分发到所有内存芯片。

DDR命令总线由几个控制DDR接口操作的信号组成。命令信号只在时钟的上升沿触发。命令可以包括:deselect, no operation, read, write, bank activate, precharge, refresh和mode register set。

地址总线选择DRAM的哪些cell被写入或读取。总线上的值决定了正在写入或读取的bank、行和列。

由于接口的双向性质,数据在内存和控制器之间以burst方式传输。为此,strobe(DQS)信号是一种差分“burst时钟”,仅在读写操作期间发挥作用。读写是dqs和dq之间的时序关系也是不同的。

最后,每个DRAM芯片都有多个并行数据线(DQ0、DQ1等),这些数据从控制器传输到DRAM进行写入操作,反之亦然。数据信号是真正的双倍数据速率信号。

274

274

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?