1 简介

数字信号处理已经发展到复杂的水平,带来了更稳健、噪声不敏感、可靠性、可测试性和更好的生产良率等优势。为了将所有这些优点带入现实世界的应用中,需要将数字域信号转换为现实世界的模拟域表示,并将现实世界的模拟信号转换为数字域表示。

Sigma-Delta 调制器 (SDM) 已成为实现高分辨率数模转换器 (DAC) 的流行方法;该方法使用过采样和噪声整形来抑制信号频带中的量化噪声。 SDM 的主要优点是其固有的线性度和稳健的模拟实现。 SDM 的这些特性使其对许多应用非常有吸引力。

现场可编程门阵列 (FPGA) 设备通常需要一个数据转换器来提供模拟输出数字域表示。随着当今 FPGA 设备密度的进步,可以实现具有越来越高集成度的系统 [2]。

所提出的 SDM 是使用 FPGA 实现的,并给出了结果。

本文首先概述了 DAC 架构,并讨论了内插滤波器的设计。 下一节展示了级联、双量化器和单环路噪声整形架构的设计; 在此之后,仿真和实现结果进行了讨论,最后总结在结论中 。

2 DAC架构

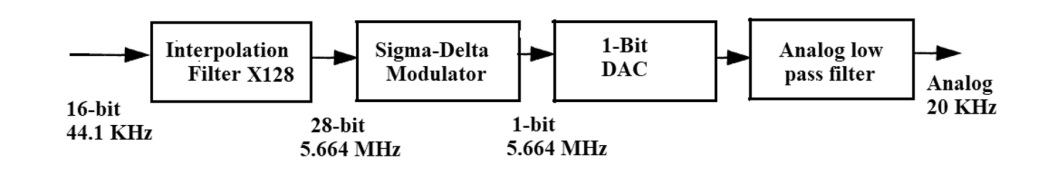

图 1 显示了过采样 DAC 的基本原理图以及在每个阶段选择的字长。它主要由两个模块组成,即

文章介绍了使用FPGA实现的高分辨率Sigma-Delta数模转换器(DAC),通过过采样和噪声整形降低量化噪声。重点讨论了内插滤波器、半带滤波器和CIC滤波器在DAC架构中的作用,以及它们如何影响最终的模拟输出质量。

文章介绍了使用FPGA实现的高分辨率Sigma-Delta数模转换器(DAC),通过过采样和噪声整形降低量化噪声。重点讨论了内插滤波器、半带滤波器和CIC滤波器在DAC架构中的作用,以及它们如何影响最终的模拟输出质量。

订阅专栏 解锁全文

订阅专栏 解锁全文

1212

1212

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?