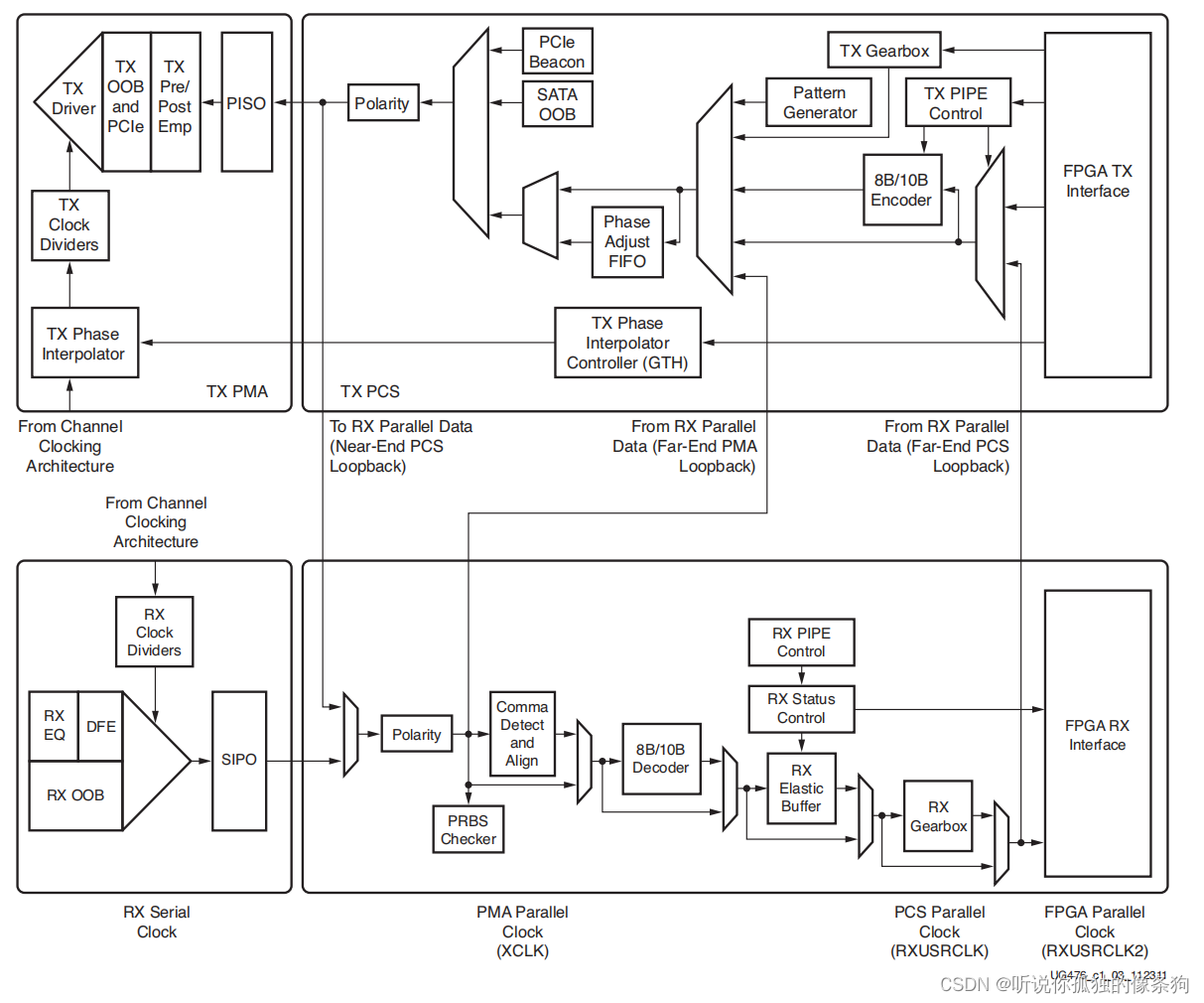

SERDES主要由物理介质相关( PMD)子层、物理媒介附加(PMA)子层和物理编码子层( PCS )所组成。PMD是负责串行信号传输的电气块。PMA负责串化/解串化,PCS负责数据流的编码/解码。在PCS的上面是上层功能。

发送缓存区 Phase Adjust FIFO。TX 数据路径有两个用于 PCS 的内部并行时钟域:PMA 并行时钟域(XCLK)和 PCS 并行时钟域(TXUSRCLK), 如果要传输数据,XCLK 速率必须与 TXUSRCLK 速率匹配,并且必须解决两个时钟域之间的相位差。发送端提供了一个 TX buffer 和一个 TX 相位校准电路,以解决 XCLK 和 TXUSRCLK 域之间的相位差。 推荐默认使用 TX Buffer.使用 TX 相位校准电路去调整 XCLK 和 TXUSRCLK 域之间的相位差,以便将数据从 PCS 传输

到 PISO。最后通过高速 Serdes 进行并串转换(PISO),经预/后加重,输出 TX 驱动程序作为高速串行数据。

8b10b encode: 8b10b编码是一种将8位数据编码为10位数据的技术,用于在高速串行通信中保证数据传输的可靠性和稳定性。 它将8位数据块映射到10位编码块,以便在传输过程中检测和纠正错误。 该编码技术还可以实现数据的时钟恢复和数据的流量控制。更详细可以查找8b10b编码。

Phase Adjust FIFO:相位纠正和跨时钟域处理。

PISO:并行输入串行输出.

Polarity:数据进行极性处理。极性控制功能,可用于实现数据翻转,在PCB设计时RXP和RXN接反 时使用这个功能。

OOB:Out-Of-Band/边带信号;

TX Pre/Post Emp: PMA数据预/后加重,进行驱动,幅度调整。由于传输线具有低通滤波器的性质,在电路板传输的高速信号会出现明显衰减,特别是趋肤效应和电介质损耗的影响。传输线上的信号边沿斜率变缓,码元变宽,幅度下降,抖动增加,导致眼图闭合,误码率上升。预加重电路将信号进行一定量的过驱动,增加信号的高频分量,经传输线后仍能保持标准信号的特征,提升眼图质量,降低误码率。

接收端:RX 接收到的信号会首先经过 RX 均衡器,均衡器的主要作用是用于补偿信号的高频损失, LPM 和 DFE 分别是两种不同模式的均衡器。简而言之,pcb衰减信号,均衡器进行补充。进入均衡器以后进入高速ADC,就外部模拟信号转成数字信号,进入SIPO(串行数据转并行数据),然后进入COMMA Detect and align (K码检测和数据对齐),进入8b/10b decoder (8b/10b)解码,进入

RX Elastic Buffer(接收端缓冲)进行跨时钟域。

169

169

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?