关注、星标公众号,不错过精彩内容

我们生活在模拟信号的世界中,但在数字电子设备中,只有两种状态:开或关。使用这两种状态,设备可以编码,传输和控制大量数据。

从广义上讲,逻辑电平描述信号可以具有的任何特定的离散状态。在数字电子学中,我们通常将研究限于两个逻辑状态:二进制1和二进制0。

一、什么是逻辑电平?

逻辑电平是特定电压或可以存在信号的状态,通常为“0/1” 或 “开/关” 或 “ON/OFF” 或 “LOW / HIGH”等。

数字电子产品依靠二进制逻辑来存储,处理和传输数据或信息,我们通常将数字电路中的两个状态称为“开”或“关”。

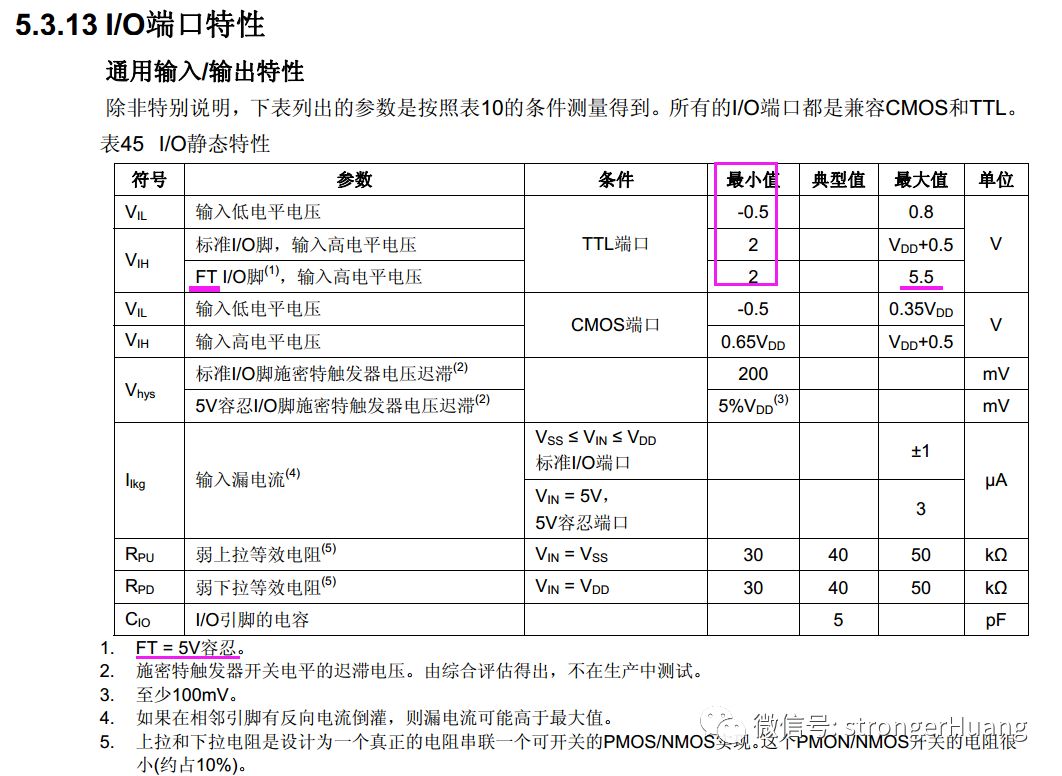

信号的强度通常由其电压电平来描述,如何定义逻辑0(低)或逻辑1(高)?芯片制造商通常会在其规格中对其进行定义,最常见的标准是TTL或晶体管逻辑。

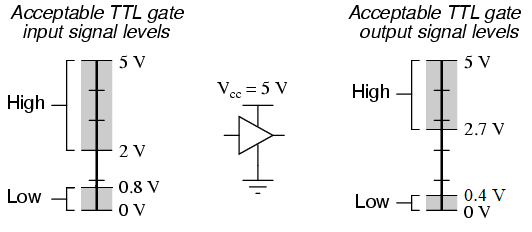

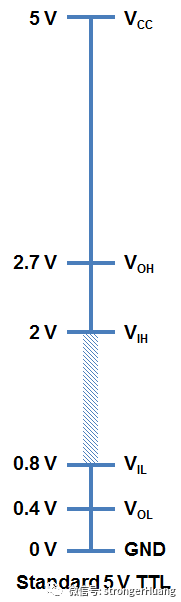

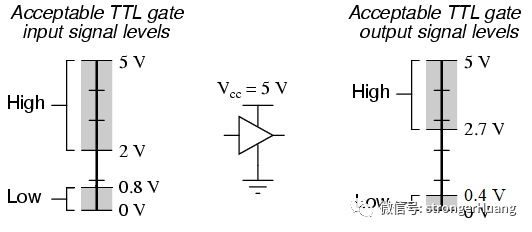

VOH:TTL设备将为HIGH信号提供的最小输出电压电平。

VIH:最小输入电压电平被视为高电平。

VOL:设备将为LOW信号提供的最大输出电压电平。

VIL:最大输入电压电平仍被视为LOW。

你会发现,最小输出HIGH电压(VOH)为2.7V。基本上,这意味着驱动HIGH的设备的输出电压将始终至少为2.7V。最小输入HIGH电压(V IH)为2 V,或者基本上任何至少2 V的电压都将作为逻辑1(HIGH)读入TTL设备。

你还会发现,一个设备的输出与另一设备的输入之间有0.7 V的缓冲,有时称为噪声余量。

最大输出低电压(VOL)为0.4V,这意味着试图发出逻辑0的设备将始终低于0.4V。

最大输入低电压(VIL)为0.8V。因此,任何读入器件时,低于0.8 V的输入信号仍将被视为逻辑0(LOW)。

如果电压在0.8 V和2 V之间,会发生什么?

答案:该电压范围是不确定的,无效状态,通常称为浮动状态。如果设备上的输出引脚在该范围内“浮动”,则无法确定信号的结果。它可能在HIGH和LOW之间任意跳动。

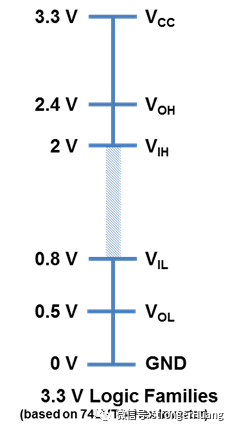

三、3.3 V CMOS逻辑电平

随着技术的进步,逻辑电压越来越低,3.3V,1.8V,甚至1.2V。

目前市面上大部分MCU的电压都是3.3V,拿STM32来说,基准电压都是3.3V(当然,支持5V输入)。

之前写过一篇《

目前常见的逻辑电平5V和3.3V居多,但如果使用两种电平信号进行通信,有些芯片能兼容,就不需要转换。

但有些芯片不兼容,比如:3.3V器件,如果超过3.6V就会永久损坏,此时就需要转换。

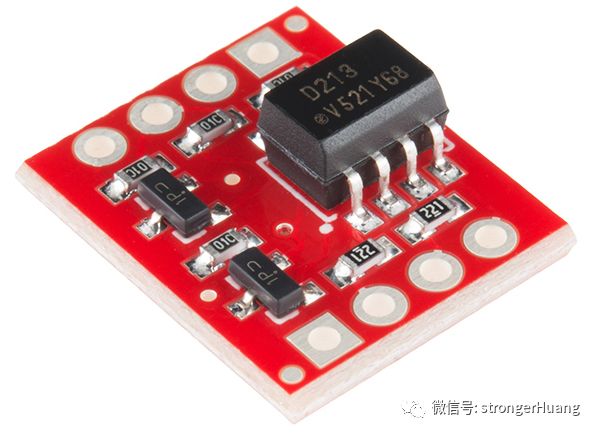

5V 与 3.3V 之间转换的方式有很多种:三极管电路、光耦电路、集成IC转换等。

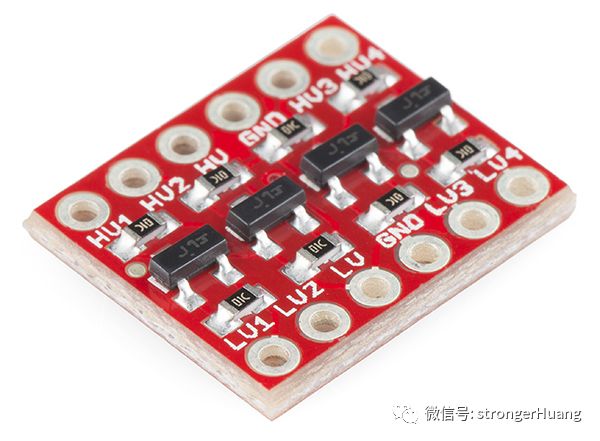

1.三极管

2.光耦

3.集成IC转换

往期好文合集

长按识别图中二维码关注

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?