Moore:

题目要求:

用moore型状态机验证1101序列。

题目描述:

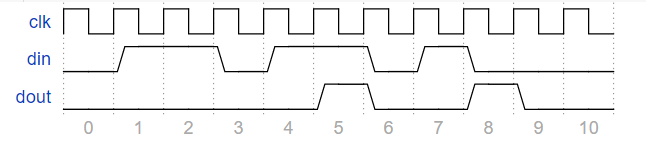

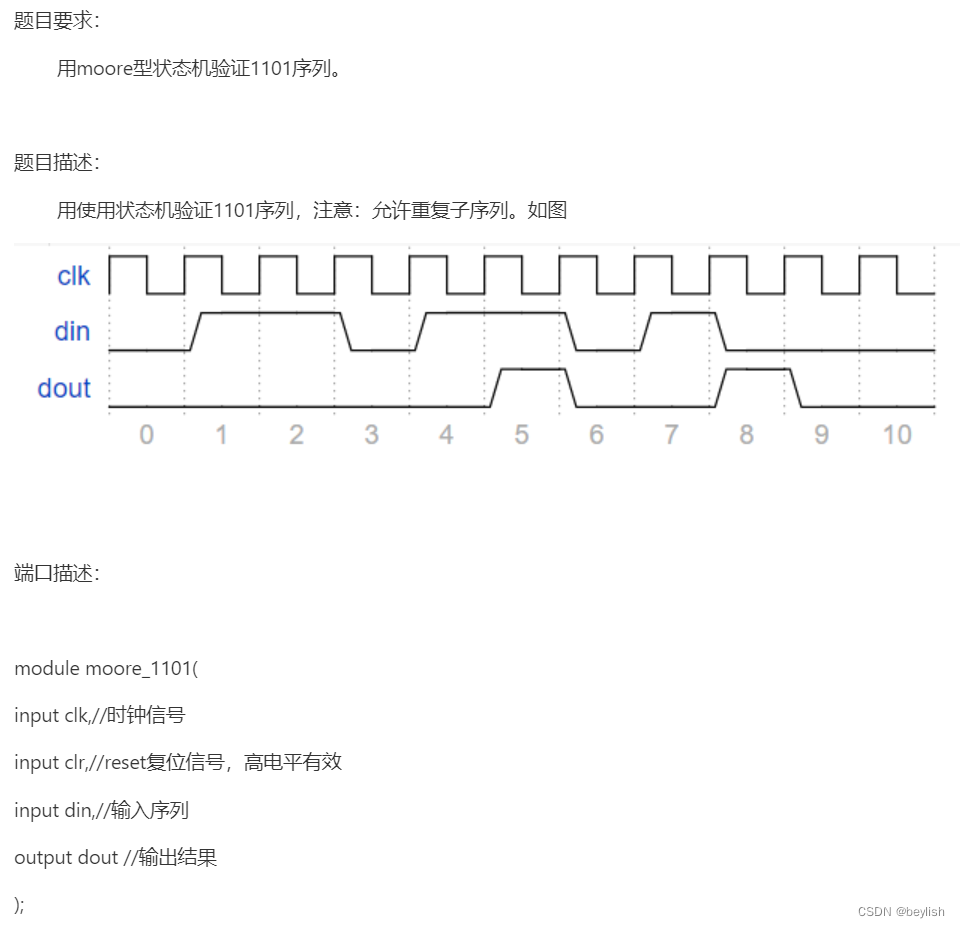

用使用状态机验证1101序列,注意:允许重复子序列。如图

端口描述:

module moore_1101(

input clk,//时钟信号

input clr,//reset复位信号,高电平有效

input din,//输入序列

output dout //输出结果

);

答案:

module moore_1101(

input clk,//时钟信号

input clr,//reset复位信号,高电平有效

input din,//输入序列

output reg dout //输出结果

);

reg[1:0]s=2'b00;

always@ (posedge clk or posedge clr)

begin

if(clr)

begin

s<=2'b00;

dout<=0;

end

else

begin

case(s)

2'b00:begin s<=din?2'b01:2'b00;dout<=0;end

2'b01:begin s<=din?2'b10:2'b00;dout<=0;end

2'b10:begin s<=din?2'b01:2'b11;dout<=0;end

2'b11:begin s<=din?2'b01:2'b00;dout<=din?1'b1:1'b0;end

endcase

end

end

endmodule

Mealy:

题目要求:

用mealy型状态机验证1101序列

题目描述:

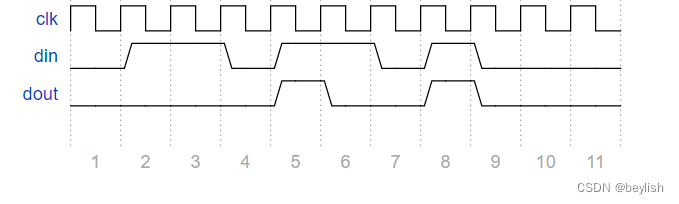

使用状态机验证1101序列,注意:允许重复子序列

端口描述:

module mealy_1101( input clk, input clr, input din, output dout);

信号说明:

-

clk为时钟信号 -

clr为reset信号,高电平有效,异步复位 -

din为输入序列 -

dout为结果输出

答案:

module mealy_1101(

input clk,

input clr,

input din,

output reg dout);

parameter S0=3'b000;

parameter S1=3'b001;

parameter S2=3'b010;

parameter S3=3'b011;

reg [2:0] current_state;

reg [2:0] next_state;

always@ (posedge clk) begin

if(clr)current_state<=S0;

else current_state<=next_state;

end

always@ (*)begin

case(current_state)

S0:next_state<=din?S1:S0;

S1:next_state<=din?S2:S0;

S2:next_state<=din?S2:S3;

S3:next_state<=din?S1:S0;

default:next_state<=S0;

endcase

end

always@ (*)begin

if(clr) dout<=1'b0;

else if((current_state==S3)&&(din==1))dout<=1'b1;

else dout<=1'b0;

end

endmodule

本文详细介绍了如何用Moore和Mealy型状态机设计来验证1101序列,包括状态转移逻辑和输出响应规则。

本文详细介绍了如何用Moore和Mealy型状态机设计来验证1101序列,包括状态转移逻辑和输出响应规则。

1943

1943

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?