使用Moore状态机和Mealy状态机设计序列检测器 II

- 问题:分别使用Moore状态机和Mealy状态机设计序列检测器。该序列检测器将检测序列“101001”,当检测到该序列时,状态机的输出为1

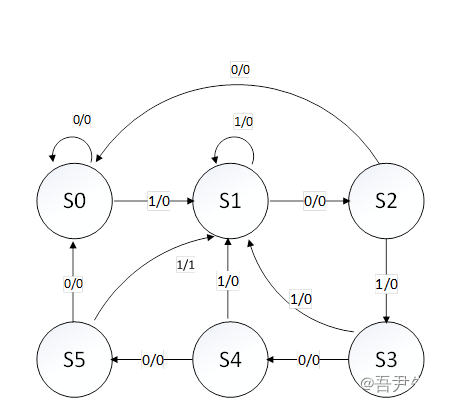

1.使用visio软件绘制状态转移图(采用Mealy状态机)

2.设计核心源代码(采用Mealy状态机)

这段Verilog代码实现了一个简单的有限状态机(FSM),用于根据输入信号data_in和当前状态c_state来更新下一个状态n_state,并在特定条件下生成输出信号data_out。下面是状态机的状态转移和输出逻辑的描述,使用序号表示各个状态:

S0(初始状态):如果输入data_in为1,则转移到状态2;如果为0,则保持在状态1。

S1:如果输入data_in为0,则转移到状态3;如果为1,则保持在状态2。

S2:如果输入data_in为1,则转移到状态4;如果为0,则回到状态1。

S3:如果输入data_in为0,则转移到状态5;如果为1,则跳转到状态2。

S4:如果输入data_in为0,则保持在状态6;如果为1,则输出高电平并保持在状态2。

S5:如果输入data_in为1,则保持在状态2;如果为0,则回到状态1。

状态机的输出data_out逻辑如下:

1、当前状态为状态6且输入data_in为1时,输出data_out为高电平(1’b1)。

2、在其他情况下,输出data_out为低电平(0)。

请注意,状态机的状态编号在代码中是连续的,但在描述中我使用了序号来表示状态,以符合您的要求。在实际的代码中,状态应该使用唯一的标识符,例如S0、S1等,以避免混淆。如果需要将状态编号改为从1开始的序号,可以在代码中相应地修改状态的标识符。

always@( * )

begin

if( !rst_n )

n_state = 0 ;

else begin

case( c_state )

S0 : if( data_in == 1)

n_state = S1 ;

else

n_state = S0 ;

S1 : if( data_in == 0)

n_state = S2 ;

else

n_state = S1 ;

S2 : if( data_in == 1)

n_state = S3 ;

else

n_state = S0 ;

S3 : if( data_in == 0)

n_state = S4 ;

else

n_state = S1 ;

S4 : if( data_in == 0)

n_state = S5 ;

else

n_state = S1 ;

S5 : if( data_in == 1)

n_state = S1 ;

else

n_state = S0 ;

default : n_state = S0 ;

endcase

end

end

assign data_out = ( c_state == S5 && data_in == 1 ) ? 1'b1 : 0 ;

3. 测试核心源代码(采用Mealy状态机)

代码完成了以下功能:

1、初始化输入信号:在仿真开始时,将时钟信号 clk 初始化为0,复位信号 rst_n 初始化为0,数据输入 data_in 初始化为0。

2、全局复位:在仿真开始后100纳秒(#100),将 rst_n 置为1,表示全局复位结束。

3、输入激励:在复位结束后,通过一系列 #20 延迟(每个延迟20纳秒),交替给 data_in 赋值1和0,模拟数据输入信号的变化。这样的序列可以测试电路对快速变化输入的响应。

4、钟信号切换:在另一个 always 块中,使用 #10 延迟来不断翻转 clk 的状态,生成周期性的时钟信号。由于初始值为0,所以时钟周期为20纳秒,即50MHz的频率。

5、结束仿真:在输入了一系列的 data_in 信号变化后,使用 #40 延迟40纳秒,然后通过 $finish 命令结束仿真。

这段代码是一个典型的Verilog测试平台,可以用来测试电路在特定输入序列下的行为。通过观察输出波形,可以验证电路的功能是否符合预期。代码中的 initial 块用于仿真开始时的初始化和测试激励的施加,而 always 块用于生成周期性的时钟信号。

```cpp

initial begin

// Initialize Inputs

clk = 0;

rst_n = 0;

data_in = 0;

#100 rst_n = 1;

// Wait 100 ns for global reset to finish

#20 data_in = 1 ; // Add stimulus here

#20 data_in = 0 ;

#20 data_in = 1 ;

#20 data_in = 0 ;

#20 data_in = 0 ;

#20 data_in = 1 ;

#20 data_in = 1 ;

#20 data_in = 0 ;

#20 data_in = 1 ;

#20 data_in = 0 ;

#20 data_in = 0 ;

#20 data_in = 1 ;

#20 data_in = 0 ;

#20 data_in = 1 ;

#20 data_in = 0 ;

#20 data_in = 0 ;

#20 data_in = 1 ;

#20 data_in = 1 ;

#20 data_in = 0 ;

#20 data_in = 1 ;

#20 data_in = 0 ;

#20 data_in = 0 ;

#20 data_in = 1 ;

#20 data_in = 1 ;

#20 data_in = 0 ;

#20 data_in = 1 ;

#20 data_in = 0 ;

#20 data_in = 0 ;

#20 data_in = 1 ;

#20 data_in = 0 ;

#20 data_in = 1 ;

#20 data_in = 0 ;

#20 data_in = 0 ;

#20 data_in = 1 ;

#20 data_in = 1 ;

#20 data_in = 0 ;

#20 data_in = 1 ;

#20 data_in = 0 ;

#20 data_in = 0 ;

#20 data_in = 1 ;

#20 data_in = 0 ;

#20 data_in = 1 ;

#20 data_in = 0 ;

#20 data_in = 0 ;

#20 data_in = 1 ;

#20 data_in = 1 ;

#20 data_in = 0 ;

#20 data_in = 1 ;

#20 data_in = 0 ;

#20 data_in = 0 ;

#20 data_in = 1 ;

#20 data_in = 0 ;

#20 data_in = 1 ;

#20 data_in = 0 ;

#20 data_in = 0 ;

#20 data_in = 1 ;

#40

$finish ;

end

always #10 clk = ~clk ;

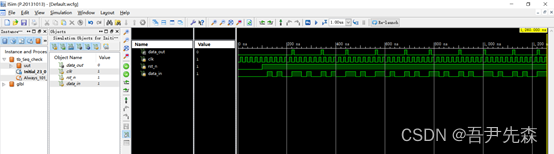

4 功能仿真波形图

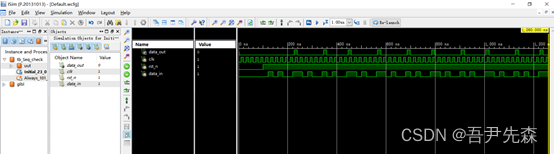

5.时序仿真波形图

6.总结

Mealy型的输出跟当前的状态以及当前的输入是有关,所以可以在当前输入有变化时候,直接作用于状态机的输出;而Moore型与当前输入无关,当前输入变化的时候需要等到时钟的同步才能作用于状态机的输出,因此 Moore型状态机比Mealy状态机延迟一个Clk,这是Mealy状态机和Moore状态机的区别,

本文采用了Mealy型的状态机去设计序列检测器,采用Moorly型状态机的设计在后文

《使用Moore状态机和Mealy状态机设计序列检测器 I 》

注:本文的源码以及状态转移图的Visio原图在下面资源中可直接下载

FPGA设计之 使用Mealy状态机 设计序列检测器“101001”

3548

3548

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?