AMBA AHB用于高性能、高时钟频率的系统模块;AMBA APB则用于低功耗外设

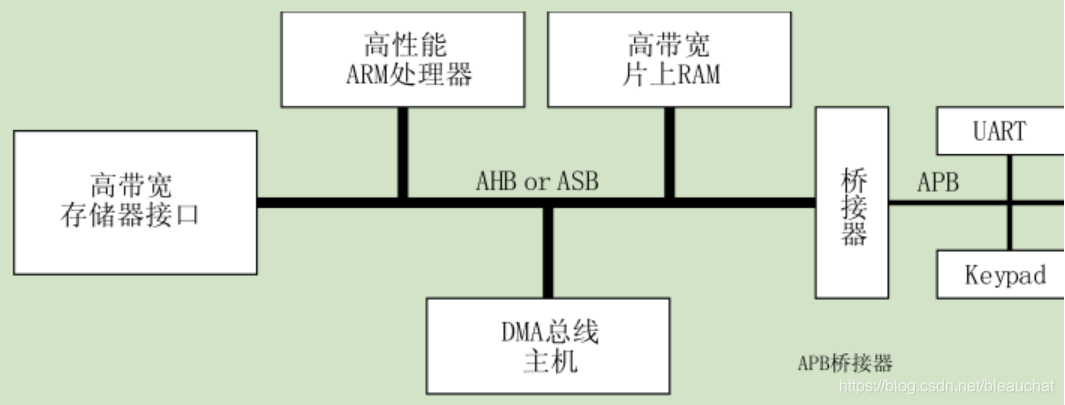

一般的系统会选择AHB/ASB+APB的总线架构,下图是一个典型的AMBA系统 :

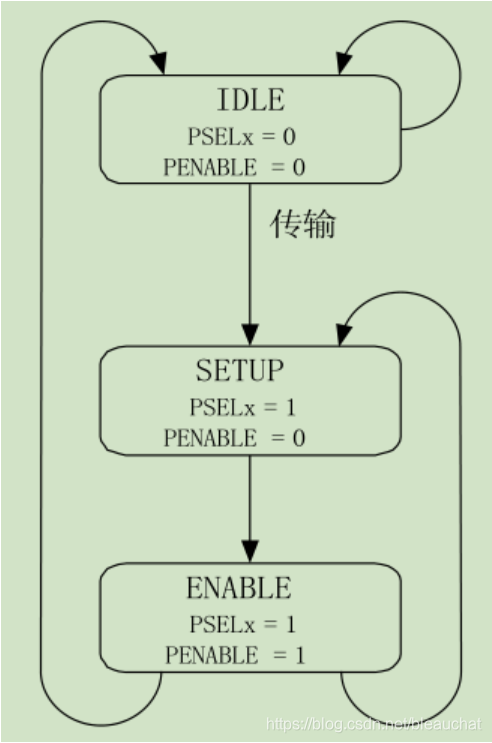

用下图所示状态图可以表示APB总线传输过程中的状态转换关系:

状态说明:

IDLE :空闲状态,总线大部分时间处于此状态;

SETUP :对应外设的psel信号被断言,表明对应外设即将有传输要求,总线进入SETUP状态。总线在SETUP状态保持一个周期,并总是在下一个时钟上升沿进入ENABLE状态;

ENABLE :penable信号被断言,地址、写、选择信号在SETUP进入ENABLE过程中保持不变。ENABLE状态持续一个周期,如果之后没有进一步的传输要求,总线返回到IDLE。如果紧跟另一个传输,则进入SETUP状态,进行第2次传输;

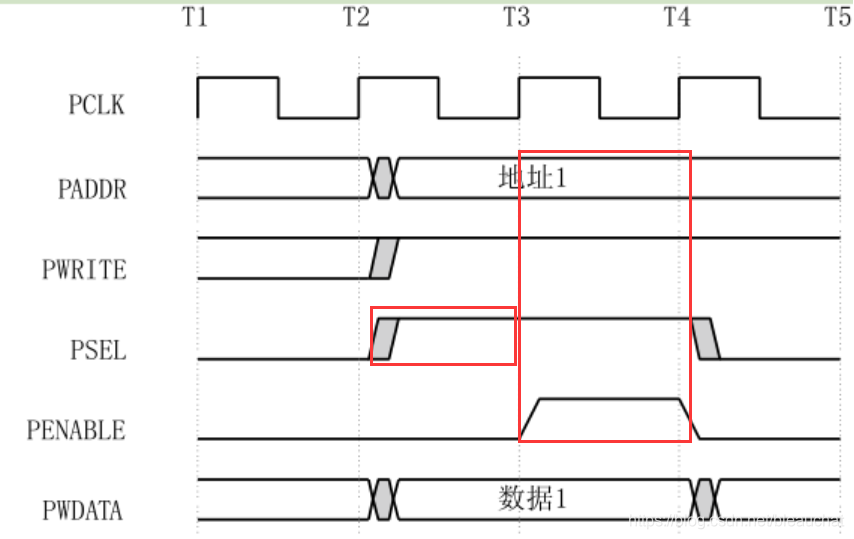

写传输

P代表APB总线定义的信号,主要包括PCLK、PADDR、PWRITE、PWDATA、PSEL、PENABLE等;

PWRITE=1表示写传输;

如图所示,一次传输过程中,psel保持两个周期不变,且在此期间,paddr、pwrite也保持不变,penable在psel有效的第2个周期有效。为了降低功耗,地址信号和写信号将在传输后不再改变,直到发生下一次传输。协议仅要求使能信号有个规则的跳变,背靠背传输情况下,选择和写信号可能有小跳变。

写逻辑推荐写法:

assign wr = psel & pwrite & (penable);

always @(posedge pclk or negege present)

begin

if(!presetn)

begin

REG_A <= 32’h0;

end

else if(wr & paddr = REG_A_ID)

begin

REG_A <= pwdata;

End

end读传输

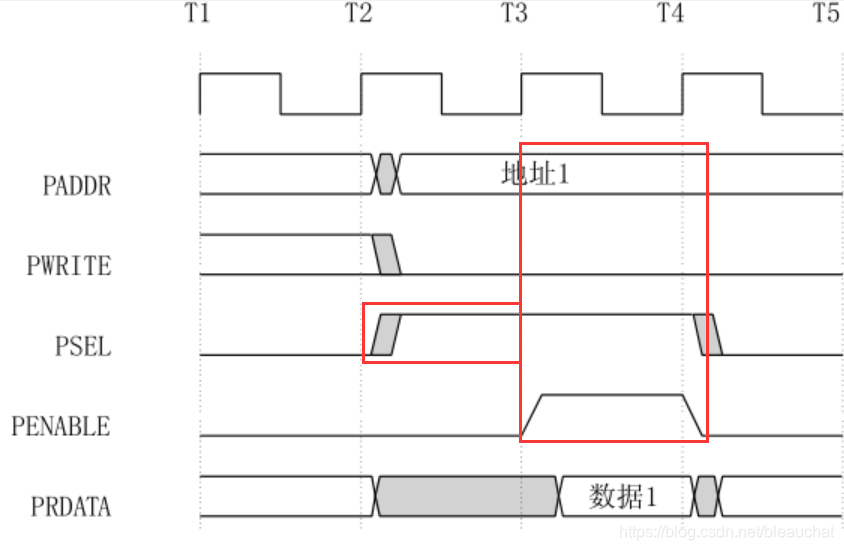

PWRITE=0表示读传输;

读传输时各信号的时序和写时一样,在读传输中,从机必须在ENABLE周期提供数据,数据在ENABLE末尾的时钟上升沿被采样;

assign rd = psel & (~pwrite) & (~penable) ;

always @(*)

begin

if(rd) //setup

begin

case(paddr)

REG_A_ID : prdatanxt = REG_A;

REG_B_ID : prdatanxt = REG_B;

……

default : prdatanxt = 32’h0;

endcase

end

else

begin

prdatanxt = 32’h0;

end

end

always @(posedge pclk or negege present)

begin

if(!presetn)

begin

prdata <= 32’h0;

end

else begin

prdata <=prdatanxt;

End

end

326

326

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?