四种基本的逻辑值

- 0:逻辑0或“假”

- 1:逻辑1或“真”

- x:未知

- z:高阻

三类常量

-

整型数:简单的十进制格式,基数格式(5’O37,4’B1x_01)

格式:

<size><’base><number>示例:

4’b1101 // this is a 4-bit binary number equal to 13 10’h2e7 // this is a 10-bit wide number specified in hex -

实数:十进制计数法,科学计数法

-

字符串:字符串是双引号的字符序列,字符串不能分成多行书写

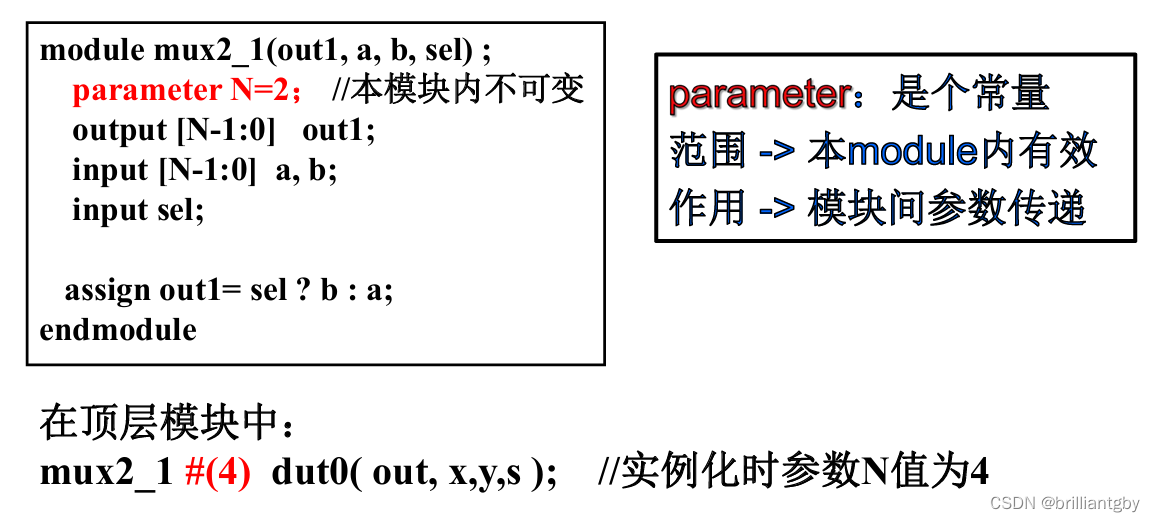

参数parameter

有时候希望模块成为一般化的模块,即希望端口位数可选。 parameter可实现此功能,在调用模块时可改变该参数的值。

数据类型

-

线网类型(wire)。net type表示Verilog结构化元件间的物理连线。它的值由驱动元件的值决定;如果没有驱动元件连接到线网,线网的缺省值为z。

信号类型默认为线网类型,wire可以在声明输入输出时省略。

-

寄存器类型(reg)。register type表示一个抽象的数据存储单元,它只能在always语句和initial语句中被赋值,并且它的值从一个赋值到另一个赋值被保存下来。寄存器 类型的变量具有x的缺省值。

Nets数据类型:表示元件之间的结构化连接。

Register数据类型:在程序块中作变量用,对信号赋值需要用该数据类型,赋值时用关键字initial或always开始。

1796

1796

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?