“

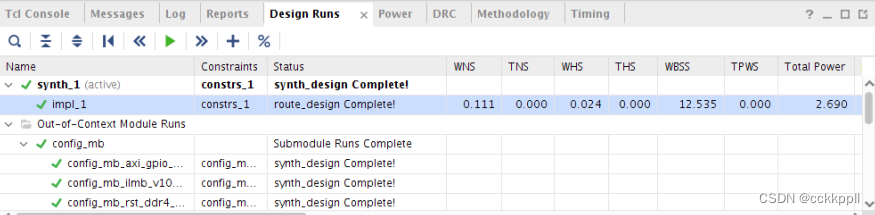

Design Runs

”窗口

“

Design Runs

”

(

设计运行

)窗口显示当前运行状态。详细内容可参考

UG893

。

显示运行状态:

“

running

”

(

正在运行

)

、“

finished cleanly

”

(

无错完成

)

或“

finished with errors”

(

已完成但有错误

)

。

“

Design Runs

”窗口列显示如下内容

:

• 运行名称

• 目标器件

• 与运行关联的约束集

• 运行策略

• 运行的最后完成步骤的状态

• 运行进度

• 运行的开始时间

• 执行过程中运行的耗用时间或已完成的运行的最终运行时间

• 运行的时序评分

:

WNS

、

TNS

、

WHS

、

THS

、

WBSS

和

TPWS

• 未能成功布线的信号线数量

• 设计

LUT

、

FF

、块

RAM

、

DSP

以及

(

如果适用

)

UltraRAM

的使用率。

• 总功耗估算

• 运行策略简介

• 方法论检查违例

• 可用的

QoR

建议

• 设计运行的增量模式

“

Design Runs

”窗口里面显示的内容就是整个工程的运行状态,如果有什么错误、警告、严重警告等等,都能从其中找到源头。

1794

1794

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?