生成的时钟

定时约束向导建议在的输出上创建一个生成的时钟顺序单元,当它直接或通过驱动其他顺序单元的时钟引脚时一些互连逻辑。与PLL或MMCM不同,用户逻辑不能将主时钟,因此向导仅提供指定除法系数的选项,如中所示如下图所示:

当几个主时钟到达生成的时钟源点时,向导将创建所有对应生成的时钟,使用唯一的名称和对单个主控器的明确引用时钟。上图说明了两个时钟(clk3和clk4)到达顺序单元FDIV_reg。因此,生成的两个时钟约束(FDIV和FDIV_1)是建议。

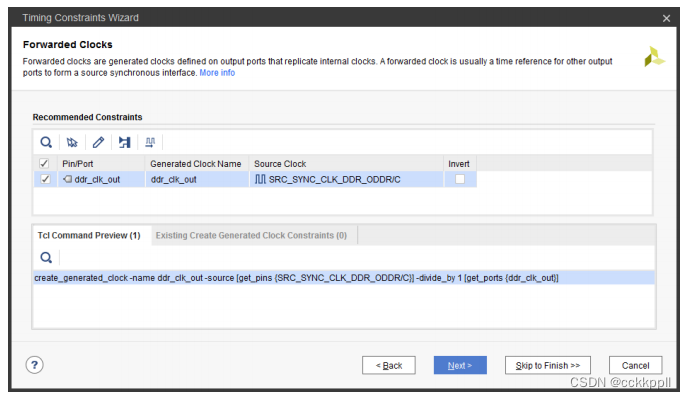

正向时钟

定时约束向导建议在以下输出端口上生成时钟约束由具有恒定输入的双数据速率寄存器驱动。基于输入常数连接,生成的时钟相位被调整为正(0度相移)或反相(180度相移)。约束中使用的主时钟是到达双倍数据速率寄存器的时钟引脚。请参阅的源时钟列下图中的推荐约束条件表:

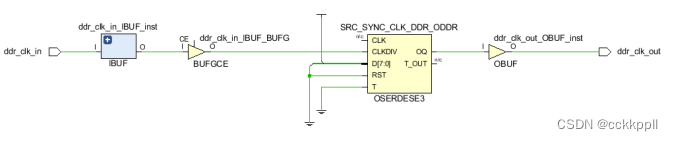

对于7系列设备系列,向导识别的拓扑如下所示图。主时钟或输出缓冲器的性质没有限制。

对于UltraScale设备系列,ODDR和ODDRE1基元会自动重定目标到属性为ODDR_MODE=TRUE的OSERESE3。向导识别拓扑如下图所示,其中OSERESE3/D[0]连接到1,OSERESE3D[4]连接到0(无相移)。

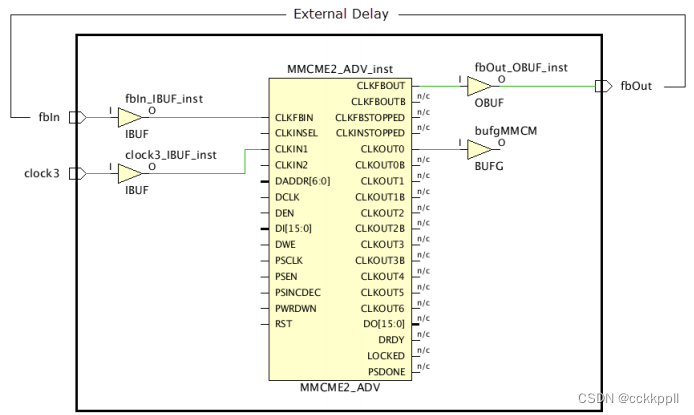

外部反馈延迟

定时约束向导分析MMCM和PLL的反馈回路连接设计中存在的单元格。当CLKFBIN和CLKFBOUT引脚通过IO缓冲器和MMCM或PLL属性COMPENSATION=EXTERNAL。下图说明了建议的外部延迟限制。

下图说明了具有外部反馈路径电路的典型MMCM。

在当前的Vivado Design Suite版本中,时间限制向导不建议当在反馈路径中存在诸如ODDR之类的顺序单元时,其用于生成转发时钟。在这种情况下,必须创建外部延迟手动约束或退出向导后使用“定时约束”窗口。

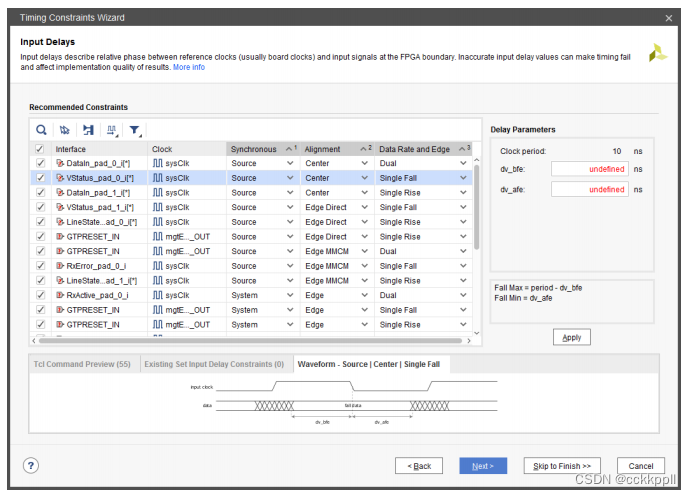

输入延迟

定时约束向导分析来自输入端口的所有路径,以确定其目标时钟内部的设计及其活动边缘。根据这些信息,向导建议基于可用XDC模板的基本系统同步输入延迟约束在Vivado IDE中(有关模板,请参阅XDC模板)。与选定的相关联的波形当您选择“推荐的约束”表中的约束条目。下图显示了向导提出的几个输入约束的示例

对于每个约束,可以编辑三个特征以指定适当的与板上的实际接口时序相对应的波形:

•同步:描述时钟数据关系的性质。

•系统(用于系统同步接口):当数据启动和由间隔1个周期或½个周期的不同时钟边沿捕获。

•Source(用于Source Synchronous接口):在启动数据和由相同的时钟边沿捕获。

•对齐:描述相对于活动时钟边缘的数据转换对齐。

•仅适用于系统同步接口:

•边缘:当时钟和数据同时转换时使用此设置。

•仅适用于源同步接口:

•中心:当时钟在数据有效的中间转换时使用此设置窗

•Edge Direct:在数据开始时时钟转换时使用此设置有效窗口。

•边缘MMCM:当数据有效结束时时钟转换时使用此设置窗

•数据速率和边沿:描述受模板约束的活动时钟边沿。这个向导建议的默认值基于捕获的活动时钟边沿顺序单元格。

•单次上升:在只有上升时钟沿启动数据的情况下使用此设置在FPGA之外。

•单次下降:此设置用于只有下降时钟沿启动数据的情况在FPGA之外。

•双重:在上升和下降时钟边沿都启动数据的情况下使用此设置在FPGA之外。推荐的时钟通常是与输入路径顺序单元相关的板时钟。当输入路径内部时钟是MMCM或PLL生成的时钟时驱动MMCM或PLL被用作输入约束参考时钟。唯一的例外当内部时钟波形和板时钟波形不相同时存在,例如以下场景:

•不同的周期场景:输入约束引用具有相同的虚拟时钟波形作为内部时钟,从而以1个周期的路径执行设置分析要求虚拟时钟是自动创建的。

•正相移时钟场景:向导使用虚拟时钟作为参考时钟。这个虚拟时钟以与板时钟相同的波形自动创建。

此外该向导还指定虚拟时钟和之间的多周期路径约束内部时钟,将默认分析调整为1个周期+用于设置的相移量。虚拟时钟和多周期路径约束的组合提供了更简单的Vivado Design Suite计时器处理的限制,并且只能影响参考虚拟时钟。注意,对于负相移,虚拟时钟和多周期路径约束为不需要,因为默认设置路径要求是1个周期减去相移。向导不允许您更改为约束选择的参考时钟。要做因此,您必须手动编辑XDC文件,或者在退出后使用“定时约束”窗口。

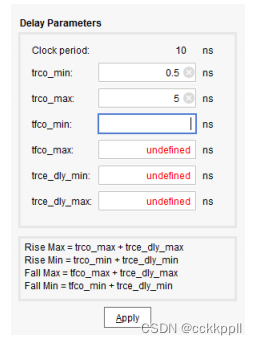

选择正确的模板后,在“延迟参数”中输入延迟参数值面板,然后单击“应用”以验证条目。输入延迟方程显示在延迟参数字段下方和一些模板波形。下图显示DDR的延迟参数面板系统同步接口模板。

要加速延迟参数输入任务,可以使用选择和编辑几个约束同时使用相同的时钟和相同的模板。在完成并应用约束后,您可以查看它们相应的TclTcl命令预览选项卡中的语法,也可以单击“下一步”继续下一步。

3987

3987

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?