本视频学习自正点原子ZYNQ领航者FPGA视频 Xilinx-P22

1.MMCM/PLL IP核简介。

锁相环作为一种反馈控制电路,其特点是利用外部输入的参考信号控制环路内部震荡信号的频率和相位。因为锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

7系列的FPGA使用了专用的全局(Global)和区域(Regional)时钟资源来管理和设计不同的时钟需求。

全局时钟:整个FPGA内部都可以用,而且延时低。

区域时钟:仅在某个模块内部用。

Clock Management Tiles(CMT)提供了时钟合成(Clock frequency synthesis),倾斜矫正(deskew),过滤抖动(jitter filtering)功能。

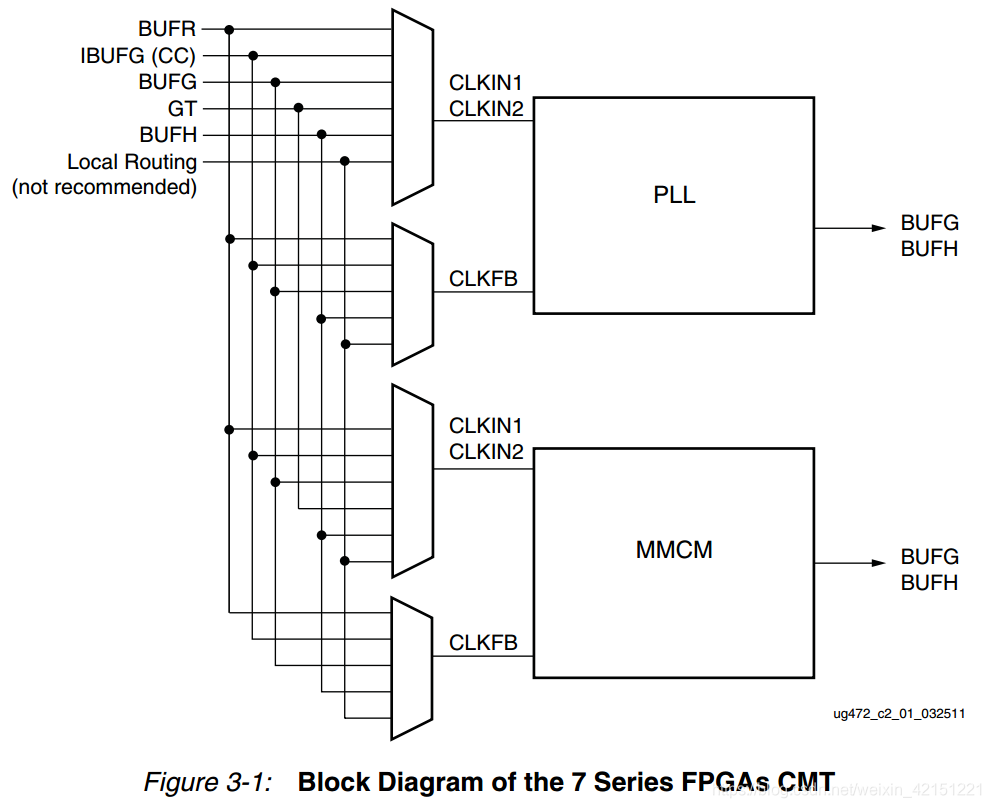

Xilinx 7 系列器件中具有时钟管理单元CMT 时钟资源,xc7z020 芯片内部有4 个CMT,xc7z010 芯片内部有2 个CMT,为设备提供强大的系统时钟管理以及高速I/O 通信的能力。时钟管理单元CMT 的总体框图如下图所示。

可以看到1个CMT里有一个MMCM和一个PLL。其中MMCM 的功能是PLL 的超集,其具有比PLL 更强大的相移功能。MMCM 主要用于驱动器件逻辑(CLB、DSP、RAM 等)的时钟。PLL 主要用于为内存接口生成所需的时钟信号,但也具有与器件逻辑的连接,因此如果需要额外的功能,它们可以用作额外的时钟资源。

本文详细介绍了Xilinx 7系列FPGA中的时钟管理资源,包括MMCM和PLL的原理及在Zynq平台的应用。通过Vivado的Clocking Wizard IP核,演示了如何配置和生成时钟,包括50MHz输入时钟生成100MHz、100MHz_180deg、50MHz和25MHz的输出时钟。通过代码实例和仿真验证了锁相环的正确工作。

本文详细介绍了Xilinx 7系列FPGA中的时钟管理资源,包括MMCM和PLL的原理及在Zynq平台的应用。通过Vivado的Clocking Wizard IP核,演示了如何配置和生成时钟,包括50MHz输入时钟生成100MHz、100MHz_180deg、50MHz和25MHz的输出时钟。通过代码实例和仿真验证了锁相环的正确工作。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

636

636

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?