vivado一般是与SDK同时使用的,像zynq系列,通过SDK烧写固化代码很方便,但是有的时候比如本人目前使用的是XC7K325T FPGA进行的开发,不会用到SDK软件,所以烧写固化代码想通过vivado直接操作。

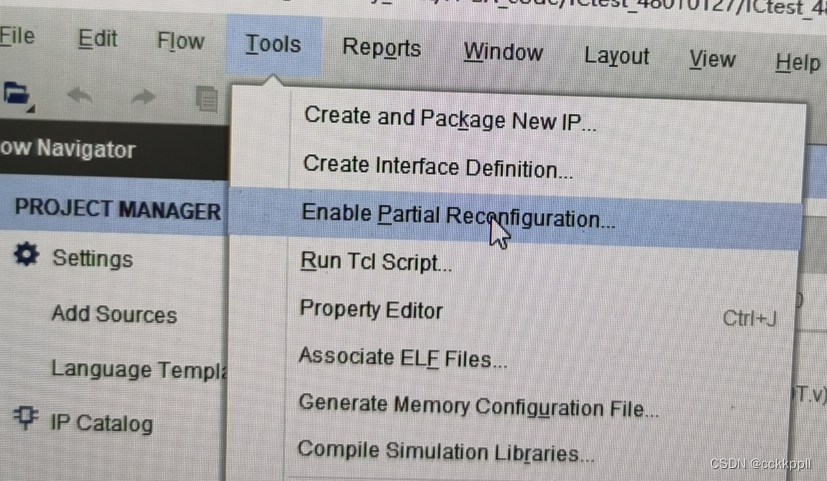

1、按照网上百度的方法进行设置,如下

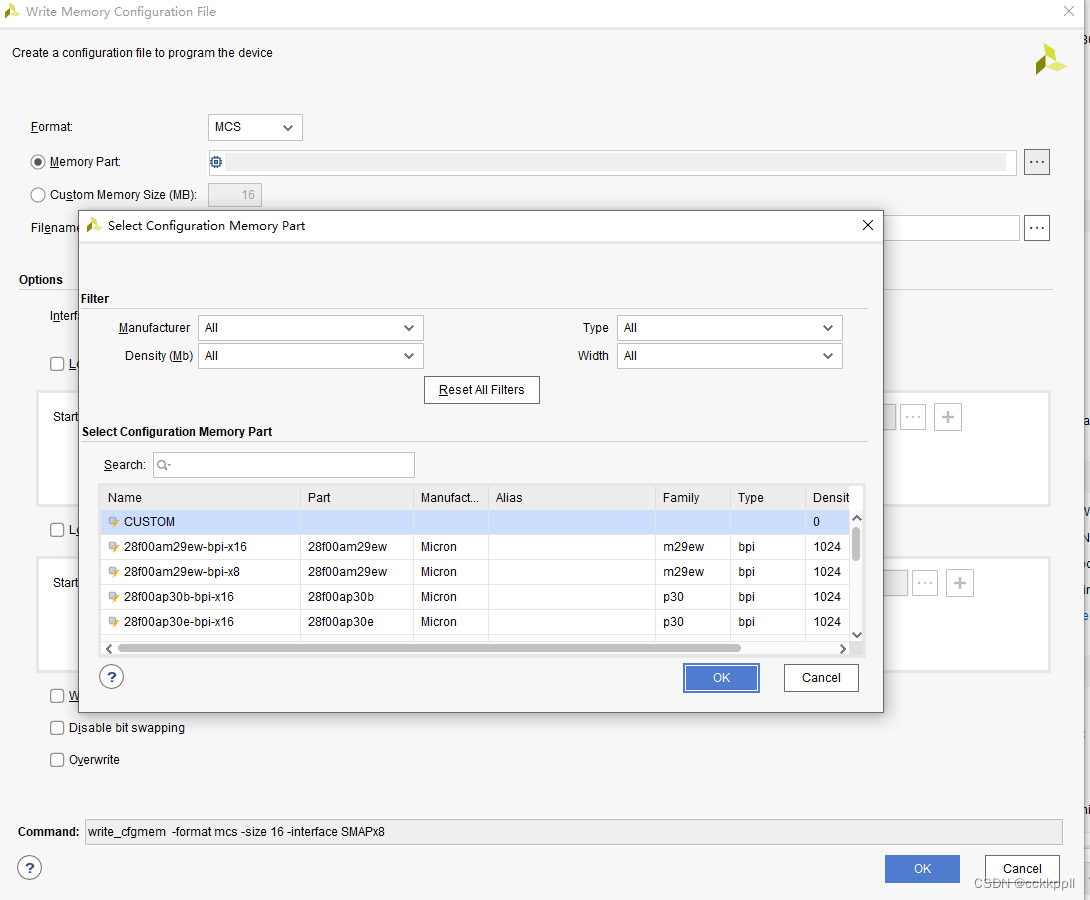

遇到的第一个问题就是在vivado2018.3的flash型号列表中没有本人使用的flash,怎么办呢,添加flash,添加方法网上有很多,就是在vivado 2018.3的安装目录下找到...\vivado20183\Vivado\2018.3\data\xicom![]()

找到这个文件后打开,里面就能看到每个FPGA系列支持的flash型号,如下

这里面是对flash进行的一个比较详细的描述,CFGMEM_ID是序号;NAME为型号,COMPATIBLE_DEVICES

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?