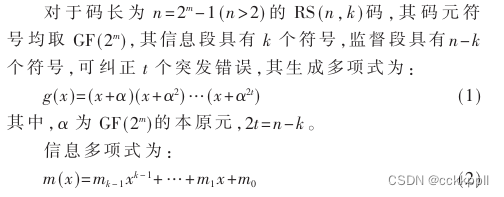

RS编码,即Reed-solomon codes,是一类纠错能力很强的特殊的非二进制BCH码(BCH码是一种有限域中的线性分组码,具有纠正多个随机错误的能力)。对于任选正整数S可构造一个相应的码长为n=qS-1的 q进制BCH码,而q作为某个素数的幂。当S=1,q>2时所建立的码长n=q-1的q进制BCH码,称它为RS码。当q=2m(m>1),其码元符号取自于F(2m)的二进制RS码可用来纠正突发差错,它是最常用的RS码。

RS码的表示方式为(n,k),其中k为信息的长度,n是RS编码后的长度,n>k,一共有n-k个校验信息,并且n比k越大,RS码的纠错效果越好,但是会降低信息传输的效率。一般都要进行取舍,现在常用的(n,k)有(204,188)、(207,187)、(255,139)、、(255,123)、(127,122)、(126,112)、、(194,178)等等,这些都是有标准的,也可以自定义,根据需要自定义合理亦可。

RS编码适用于短码,一般编码后长度不会大于255,即一般信息长度小于255bit。对于更长的信息传输的纠错编码最好选择其他编码方式。

本文介绍了RS编码,一种纠错能力强的非二进制BCH码,尤其在伽罗华域中的应用。详细讲述了其编码方式(如(204,188)等常用组合),并重点阐述了如何在FPGA中用Verilog实现RS编码,包括Vivado提供的RSIP核的使用方法。

本文介绍了RS编码,一种纠错能力强的非二进制BCH码,尤其在伽罗华域中的应用。详细讲述了其编码方式(如(204,188)等常用组合),并重点阐述了如何在FPGA中用Verilog实现RS编码,包括Vivado提供的RSIP核的使用方法。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1452

1452

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?