描述

PKGPIN_NIBBLE是PKGPIN_BYTEGROUP的一部分。参见PKGPIN_BYTEGROUP,

第122页了解该对象的描述。

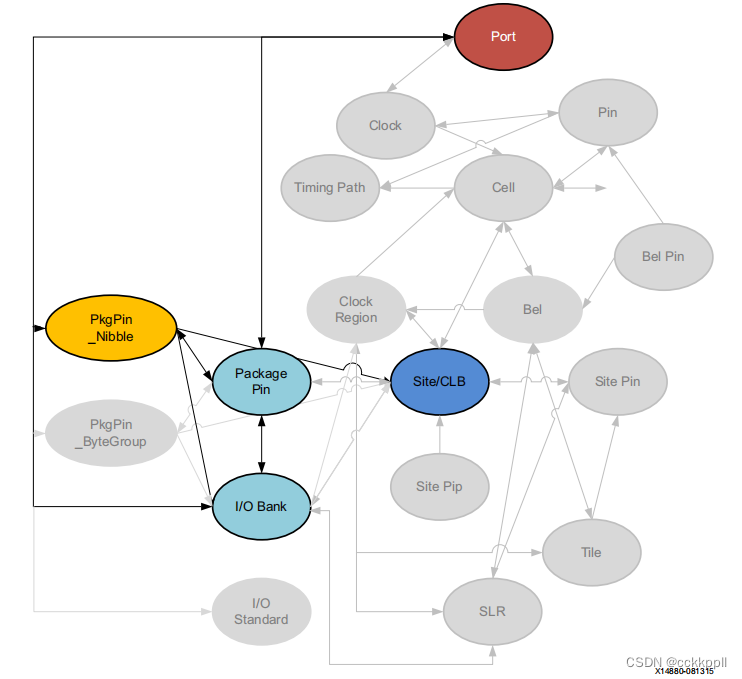

相关对象

PKGPIN_BYTEGROUP和PKGPIN_NIBBLE与IO_BANK、PACKAGE_PIN和

PORT,如前所述。此外,每个PKGPIN_NIBBLE都与

Xilinx设备。您可以使用Tcl查询关联对象的PKGPIN_NIBBLE

命令如下:

get_pkgpin_nibbles-of[get_iobanks 45]

您还可以获得分配给特定pkgpin_nibbles的package_pin对象的列表:

get_package_pins-共[get_pkgpin_nibbles BANK45_BYTE2_L]

属性

pkgpin_nibble对象上的属性如下所示,其中包含示例值:

Property Type Read-only Value

CLASS string true pkgpin_nibble

IOBANK int true 45

NAME string true BANK45_BYTE2_L

PKGPIN_BYTEGROUP string true BANK45_BYTE2

TYPE string true L

The properties of pkgpin_nibble objects can be listed with the following command:

report_property -all [lindex [get_pkgpin_nibbles] 0]

PORT

描述

端口是一种特殊类型的分层引脚,在

分层设计的顶层,或分层单元中的内部连接点,或

块模块,用于将内部逻辑连接到分层单元上的引脚。端口可以是

标量,包含单个连接,或者可以是对多个信号进行分组的总线端口

在一起

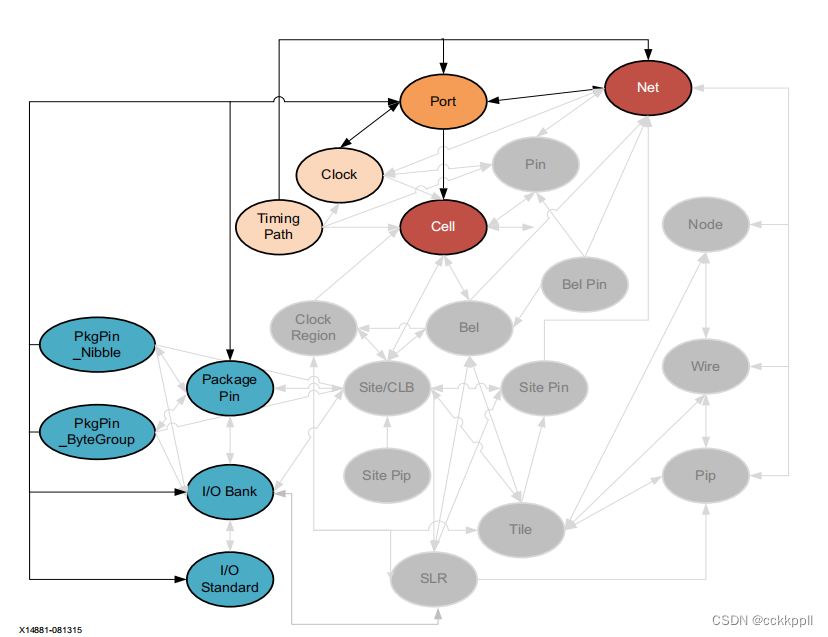

相关对象

设计顶层的端口通过

设备包的PACKAGE_PIN,到裸片上的IO_BANK,分配

IOSTANDARDs。

端口还可以将时钟定义从系统或板带到设计中,并且应该

使用set_input_delay或

set_output_delay约束。请参阅Vivado Design Suite用户指南:使用

限制条件(UG903)[参考文献19],了解有关这些限制条件的更多信息。

您可以查询分配给特定package_pins、IO_banks、IO_Standards、sites的端口,

使用Tcl命令的小区、网络、时钟、timing_path或drc_conflications,如下所示:

get_ports-of[get_clocks]

在设计内部,端口通过网络连接到单元,以构建层次结构

网表。您可以查询与端口相关联的对象,如net、timing_path、site、,

io_bank、io_standard、package_pin、pkgpin_bytegroup、pkgpin _nibble,使用以下内容

命令形式:

get_package_pins-of[all_inputs]

属性

在端口对象上找到的属性如下,其中包含示例值:

端口是一种特殊类型的分层引脚,在

分层设计的顶层,或分层单元中的内部连接点,或

块模块,用于将内部逻辑连接到分层单元上的引脚。端口可以是

标量,包含单个连接,或者可以是对多个信号进行分组的总线端口

在一起

相关对象

设计顶层的端口通过

设备包的PACKAGE_PIN,到裸片上的IO_BANK,分配

IOSTANDARDs。

端口还可以将时钟定义从系统或板带到设计中,并且应该

使用set_input_delay或

set_output_delay约束。请参阅Vivado Design Suite用户指南:使用

限制条件(UG903)[参考文献19],了解有关这些限制条件的更多信息。

您可以查询分配给特定package_pins、IO_banks、IO_Standards、sites的端口,

使用Tcl命令的小区、网络、时钟、timing_path或drc_conflications,如下所示:

get_ports-of[get_clocks]

在设计内部,端口通过网络连接到单元,以构建层次结构

网表。您可以查询与端口相关联的对象,如net、timing_path、site、,

io_bank、io_standard、package_pin、pkgpin_bytegroup、pkgpin _nibble,使用以下内容

命令形式:

get_package_pins-of[all_inputs]

属性

在端口对象上找到的属性如下,其中包含示例值:

Property Type Read-only Visible Value

BOARD_PART_PIN string false true

BOARD_PIN string false false

BUFFER_TYPE enum false true

BUS_DIRECTION enum true true

BUS_NAME string true true

BUS_START int true true

BUS_STOP int true true

BUS_WIDTH int true true

CLASS string true true port

CLOCK_BUFFER_TYPE enum false true

DIFFTERMTYPE bool false false 0

DIFF_PAIR_PORT string true true

DIFF_PAIR_TYPE enum true true

DIFF_TERM bool false true 0

DIRECTION enum false true IN

DQS_BIAS enum false true

DRIVE enum false true 12

DRIVE_STRENGTH enum false false 12

ESSENTIAL_CLASSIFICATION_VALUE int false true

HD.ASSIGNED_PPLOCS string* true true

HD.CLK_SRC string false true

HD.LOC_FIXED bool false false 0

HD.PARTPIN_LOCS string* false true

HD.PARTPIN_RANGE string* false true

HD.PARTPIN_TIEOFF bool false true

HOLD_SLACK double true true needs timing update***

IBUF_LOW_PWR bool false true 0

INTERFACE string false true

INTERMTYPE enum false false NONE

IN_TERM enum false true NONE

IOB enum false true

IOBANK int true true 33

IOSTANDARD enum false true LVCMOS18

IOSTD enum false false LVCMOS18

IO_BUFFER_TYPE enum false true

IS_BEL_FIXED bool false false 1

IS_FIXED bool false false 1

IS_GT_TERM bool true true 0

IS_LOC_FIXED bool false true 1

IS_REUSED bool true true

KEEP string false true

KEEPER bool false false 0

LOAD double false true

LOC site false true IOB_X1Y43

LOGIC_VALUE string true true unknown

NAME string false true reset

OFFCHIP_TERM string false true NONE

OUT_TERM enum false true

PACKAGE_PIN package_pin false true W9

PIN_TYPE enum true false

PIO_DIRECTION enum false true

PULLDOWN bool false false 0

PULLTYPE string false true

PULLUP bool false false 0

SETUP_SLACK double true true needs timing update***

SITE site false false IOB_X1Y43

SLEW enum false true

SLEWTYPE enum false false

SLEW_ADV enum false false

UNCONNECTED bool true true 0

USE_INTERNAL_VREF enum false true

VCCAUX_IO enum false true

XLNX_LINE_COL int false false

XLNX_LINE_FILE long false false

X_INTERFACE_INFO string false true

The properties of ports can be listed with the following command:

report_property -all [lindex [get_ports] 0]

7494

7494

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?