一、高速信号简介

常见的高速信号有几种:ECL电平、LVDS电平、CML电平

其中ECL电平根据供电的不同还分为:

ECL――负电源供电(一般为-5.2v)

PECL――正5V供电

LVPECL――正3v3供电,还有一种2.5V供电

一般情况下,常见的高速信号都是差分信号,因为差分信号的抗干扰能力比较强,并且自身产生的干扰比较小,能够传输比较高的速率。

二、几种常见的高速信号

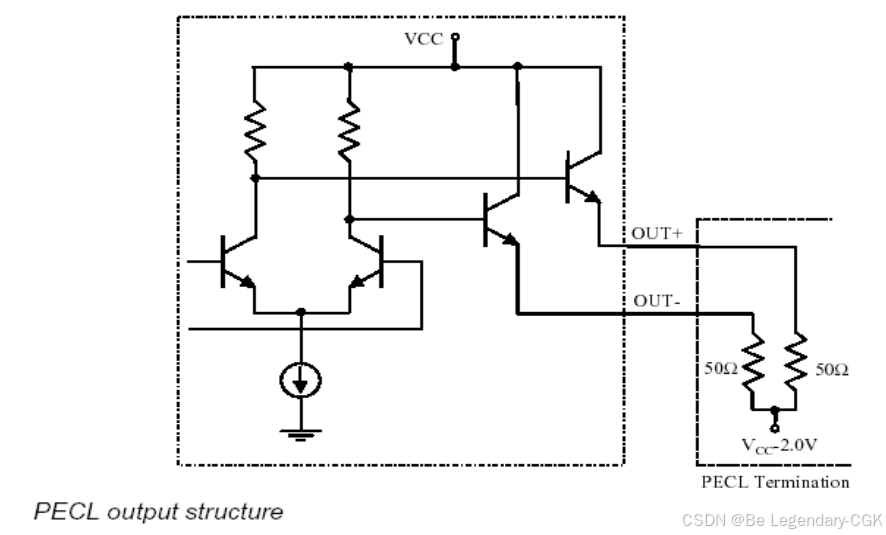

1. PECL电平

从发展的历史来说,ECL信号最开始是采用-5.2V供电的(为何采用负电源供电下面会详细说明),但是负电源供电始终存在不便,后来随着工艺水平的提升,逐渐被PECL电平(5V供电)所替代,后来随着主流芯片的低电源供电逐渐普及,LVPECL也就顺理成章地替代了PECL电平。

PECL信号的输出门特点:

PECL信号的输出门特点:

- 输出门阻抗很小,一般只有4~5欧姆左右:

- 输出的驱动能力很强;直流电流能达到14mA;

- 同时由于输出门阻抗很小,与PCB板上的特征阻抗Z0(一般差分100欧姆),相差甚远当终端不是完全匹配的时候,信号传到终端后必然有一定的反射波,而反射波传会到源端后,也不能在源端被完全匹配,这样必然发送二次反射。正因为存在这样的二次反射,导致了PECL信号不能传输特别高的信号。一般155M、622M的信号还都在使用PECL/LVPECL信号,到了2.5G以上的信号就不用这种信号了。

- PECL信号的回流是依靠高电平平面(即VCC)回流的,而不是低电平平面回流。所以,为了尽可能的避免信号被干扰,要求电源平面干扰比较小。也就是说,如果电源平面干扰很大,很可能会干扰PECL信号的信号质量。这就是ECL信号出现之初为何选用负电源供电的根本原因。一般情况下,我们认为GND平面是比较干净的平面。因为我们可以通过良好的接地来实现GND的平整(即干扰很小)。

- 从这个角度来说,PECL信号和LVPECL信号都是容易受到电源(VCC)干扰的,所以必须注意保证电源平面的噪声不能太大。

- 对于输出门来说,P/N二个管脚不管输出是高还是低,输出的电流总和是一定的(即恒流输出)。恒流输出的特性应该说是所有的差分高速信号的共同特点(LVDS/CML电平也是如此)。这样的输出对电源的干扰很小,因为不存在电流的忽大忽小的变化,这样对电源的干扰自然就比较小。而普通的数字电路,如TTL/CMOS电路,很大的一个弊病就是干扰比较大,这个干扰大的根源之一就是对电源电流的需求忽大忽小,从而导致供电平面的凹陷。

- PECL的直流电流能达到14mA,而交流电流的幅度大约为8mA(800mV/100ohm),也就是说PECL的输出门无论是输出高电平还是低电平,都有直流电流流过,换一句话说PECL的输出门(三极管)始终工作在放大区,没有进入饱和区和截至区,这样门的切换速度就可以做得比较快,也就是输出的频率能达到比较高的原因之一。

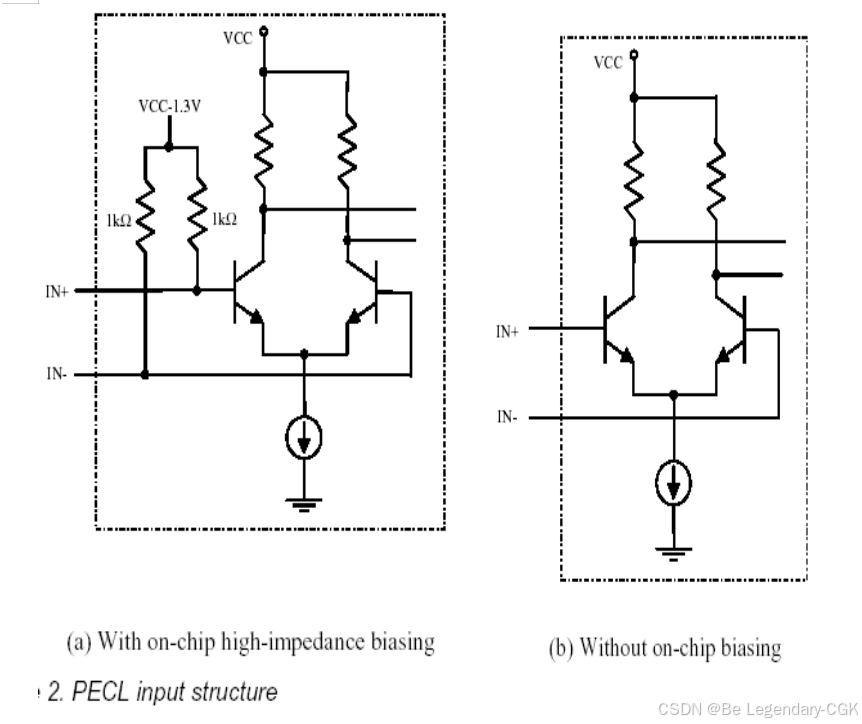

下面是PECL电平的输入门结构:

其中分为二种:一种是有输入直流偏置的,一种是没有输入直流偏置,需要外接直流偏置的。

一般情况下,ECL/PECL/LVPECL信号的匹配电阻(差分100欧姆)都是需要外加的,芯片内部不集成这个电阻。大家可以看到,VCC-1.3V为输入门的中间电平(即输入信号的共模电压),对于LVPECL来说大约为2V,对于PECL来说为3.7V。也就是说,我们要判断一个PECL/LVPECL电平输入能否被正常接收,不仅要看交流幅度能否满足输入管脚灵敏度的要求,而且要判断直流幅度是否在正常范围之内(即在VCC-1.3V左右,不能偏得太大,否则输入门将不能正常接收)。在这一点上与LVDS有很大的差别,务必引起注意。

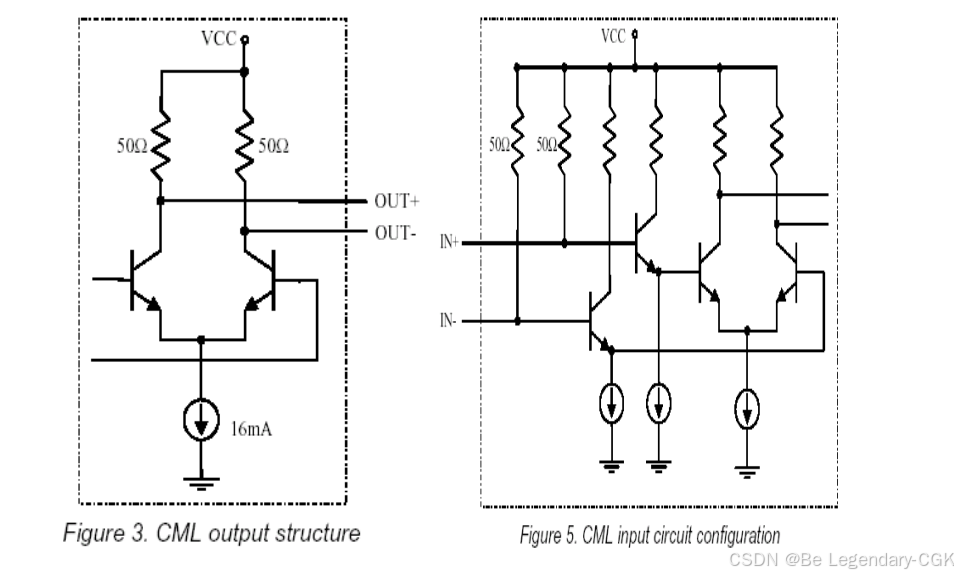

2. CML电平

CML电平是一种比较简洁的电平,它内置匹配电阻(输入输出都有50欧姆的电阻),这样用户使用的是否特别简单,不需要象ECL电平一样加一堆的偏置电阻和匹配电阻。

CML电平的输出门和输入门:由于输出门也有50欧姆的匹配电阻,使得二次反射信号也能被这个电阻匹配掉,这样就避免了多次反射导致的信号劣化(振铃现象)。在这一点,与ECL电平相比有很大的改进,所以CML电平所能支持的速率比较高,

一般情况下,2.5G/10G这样的高速信号都是采用CML电平来传输,不再采用LVPECL信号。

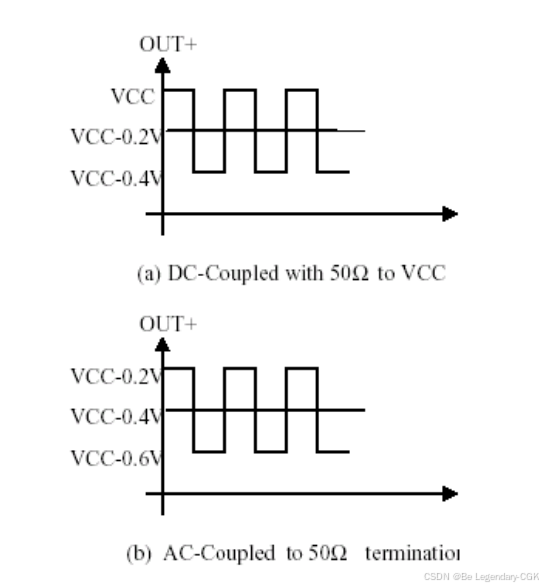

从光口的抖动指标来看,CML电平具有抖动指标小的特性。对比3种电平抖动方面的性能:CML最优、ECL次之、LVDS比较差。这就是一般情况下LVDS信号很少做为光接口驱动信号的原因之一(当然,输出信号幅度比较小、电流驱动能力比较弱应该也是原因之一吧。)同样的,CML电平也是采用恒流驱动方式。CML电平的输出AC摆幅能达到800mV一般情况下,CML电平可以是直流耦合方式对接,也可以是交流耦合方式对接。

3. LVDS电平

LVDS电平与PECL和CML电平来说有几个比较显著的特点:

- LVDS电平的驱动电流很小才4mA,所以功耗特别小,输出摆幅为400mV。当系统种有很多这种信号的时候(如TDCS6440G芯片有64对的622M 的LVDS收发),它的功耗优势就能体现出来。在我们设计系统的过程中,芯片的功耗和系统的散热一直是重点考虑的问题。

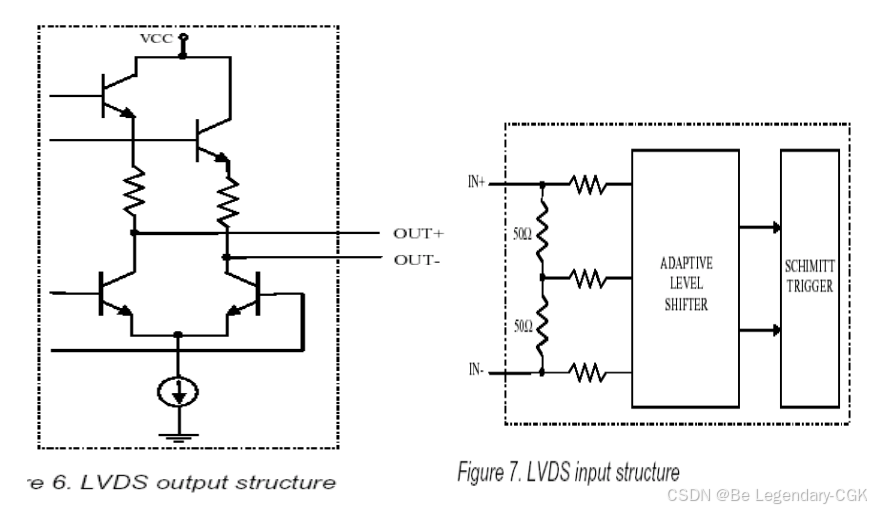

- LVDS的输入门与其他输入门有一个显著的特点,前面有一个类似于直流电平漂移适配电路(ADAPTIVE LEVEL SHIFTER),这个电路能够适应直流电平(common-mode voltage)的变化的,使得输入直流电平变化范围可以很宽(0.2V~2.2V)。也正因为这样,LVDS比其他信号有更强的共模抗干扰能力。因为LVDS的差分线一般情况下离得比较近,一旦有干扰,P、N二个信号会同时受到干扰,这样导致P/N同时上升或者下降,而LVDS通过这个均衡电路就能很好地适应这种干扰,从而提高共模抗干扰能力。

- LVDS电平可以做成支持热插拔,从而支持做为背板驱动,而PECL/LVPECL和CML电平一般情况下不支持热插拔,不能用在背板驱动。从电路的结构上我们也可以看到LVDS的输出门结合了PECL电平和CML电平的特点,并且通过串阻的限流,可以限制浪涌电流的产生,避免门的损坏,CML电平也能做成支持热插拔,但是普通的CML电平不一定能支持热插拔。

这一点与PECL电平有显著的差别,PECL信号是要求直流电平在VCC-1.3V左右,偏差不能太大,否则就不能正常接收。另外,LVDS输入门内部集成了100欧姆的匹配电路,所以芯片外部就不需要加匹配电阻了,大大简化了设计的难度。如果在BGA下需要加一堆的匹配电阻的话,其设计难度确实不是一般的大。LVDS还能容忍收发器之间的GND电平差达到±1V左右。这个特性使得LVDS在用于二个不同系统之间的互连的时候就显得特别方便,它可以不要求二个系统的GND平面完全等电势。例如,主框与从框之间可以通过LVDS信号互连起来。

514

514

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?