一、准备工作

1、新建文件夹

在新建大文件夹里面再新建三个文件夹,分别放pcb设计文件,pcb设计用到的封装文件,原理图文件。如下:

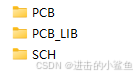

2、打开PCB Edieor 17.4新建工程

放在PCB文件夹中,并命名。

3、准备好器件的封装和网表

3.1器件封装

器件封装的获取有三种方式:

1、自己根据数据手册画。

2、从别的已有的PCB工程中提取。

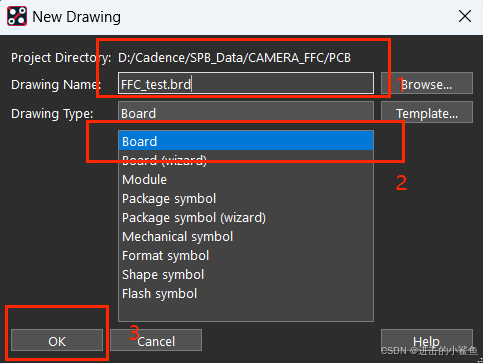

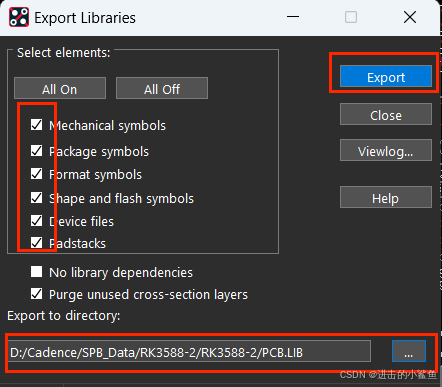

file->export->libiaries

选择导出目标文件夹->全导出

3、从网站上下载。

3.2网表

从原理图中导出。

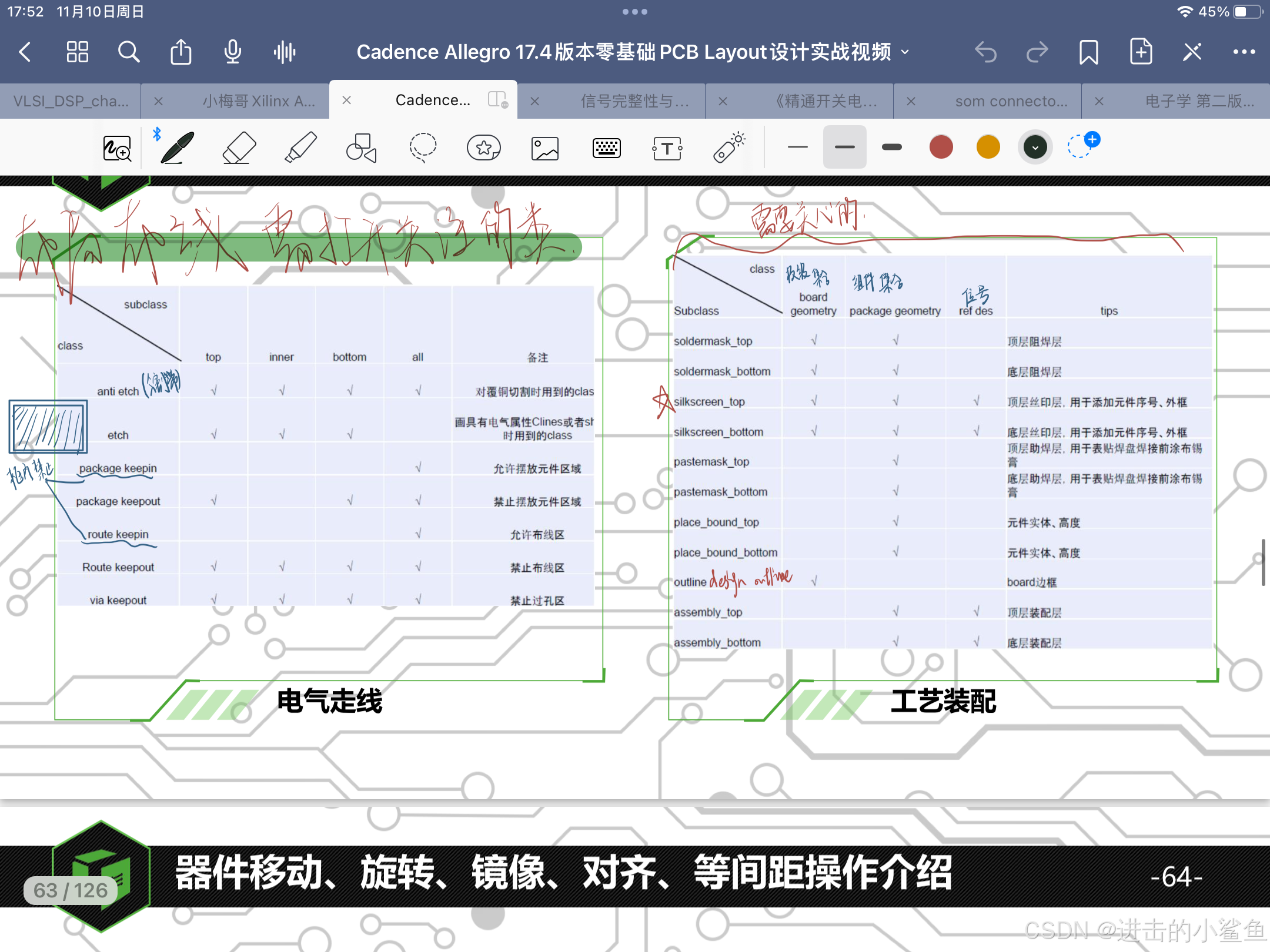

3.3板框

3.3.1、板框结构复杂,一般是从结构工程师那获得.dxf文件。

3.3.2、结构简单可以自己在pcb中自己画。

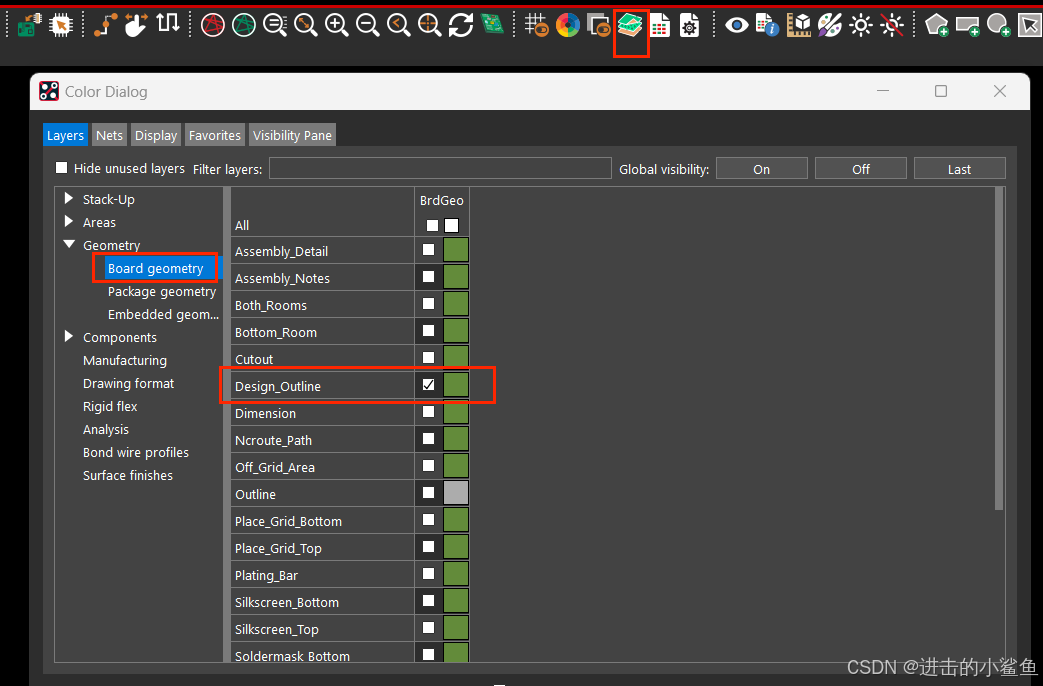

板框放在Design_Outline层

二、导入

1、.dra和.bsm

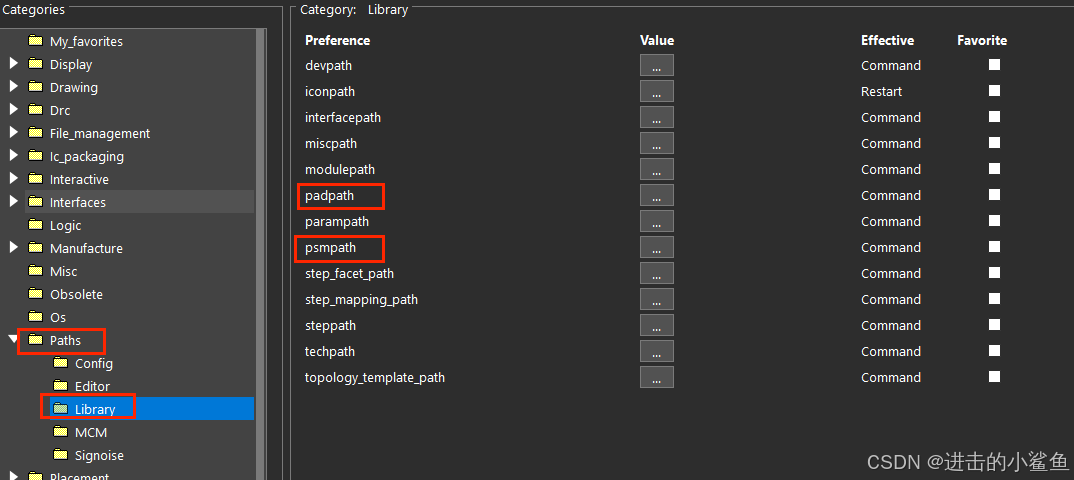

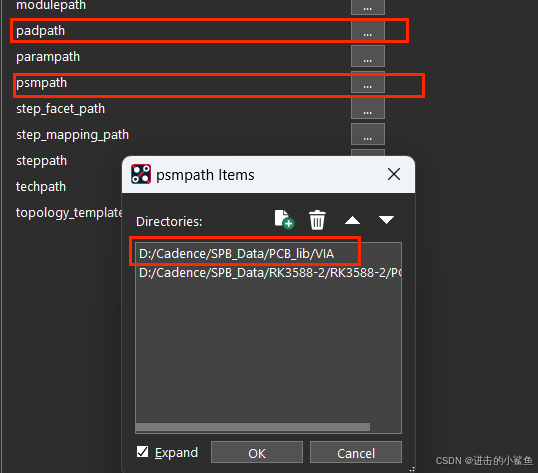

setup->user preference->path->library

在padpath和psmpath都添加封装文件路径。

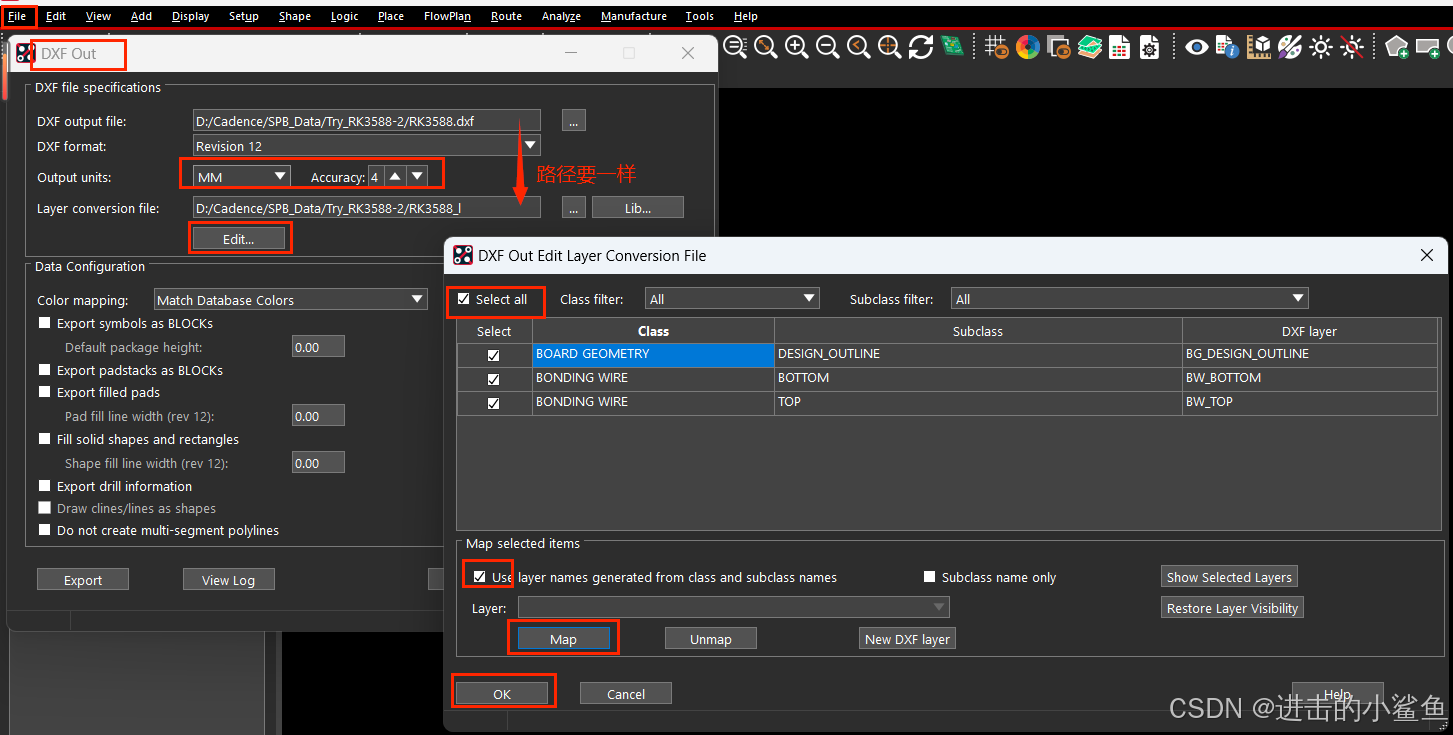

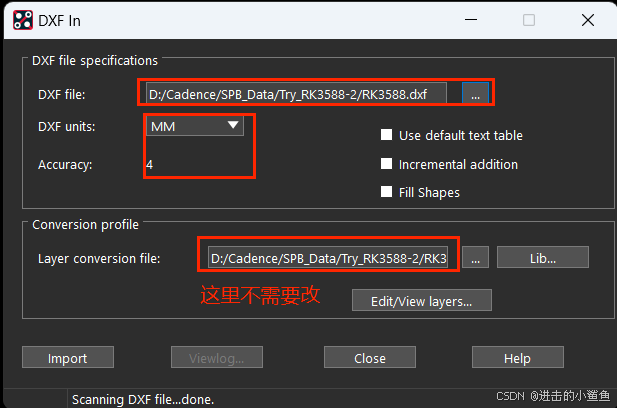

2、板框.dxf

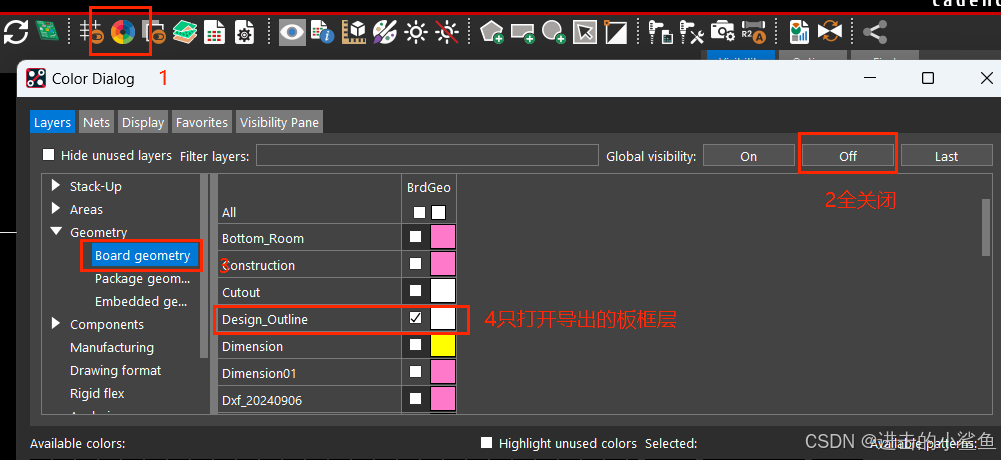

导出板框文件

导入板框:

3、过孔文件

从B站up主那获取后可以一直使用。

和.dra和.bsm一样在padpath和psmpath都添加路径。

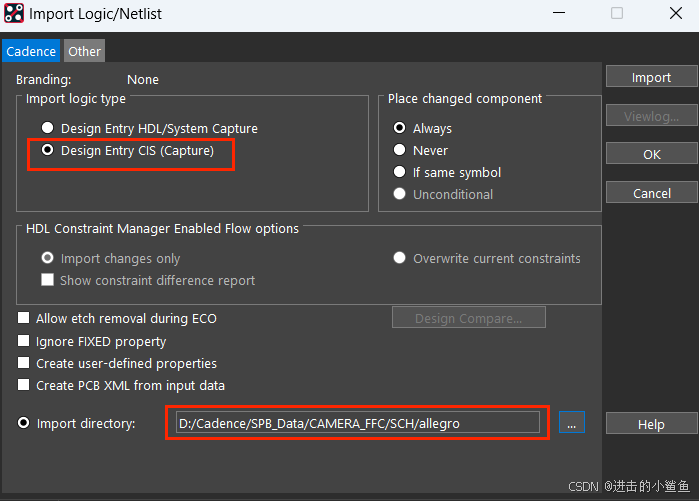

4、网表文件

若导入网表出现类似下面的报错:

ERROR(SPMHNI-164): Problems with device '1*2P_2P54_PZ254V-11-02P'. JEDEC_TYPE property '插件2P54' is illegal: 'Package name has invalid characters or is too long.'.

是因为原理图器件封装中汉字是非法字符。

5、颜色导入

我使用的是一博一次PCB文件用的颜色搭配。

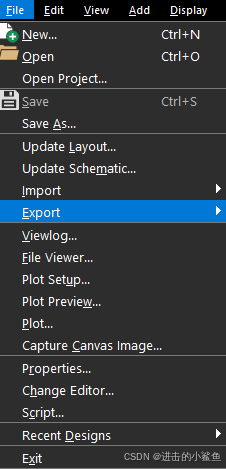

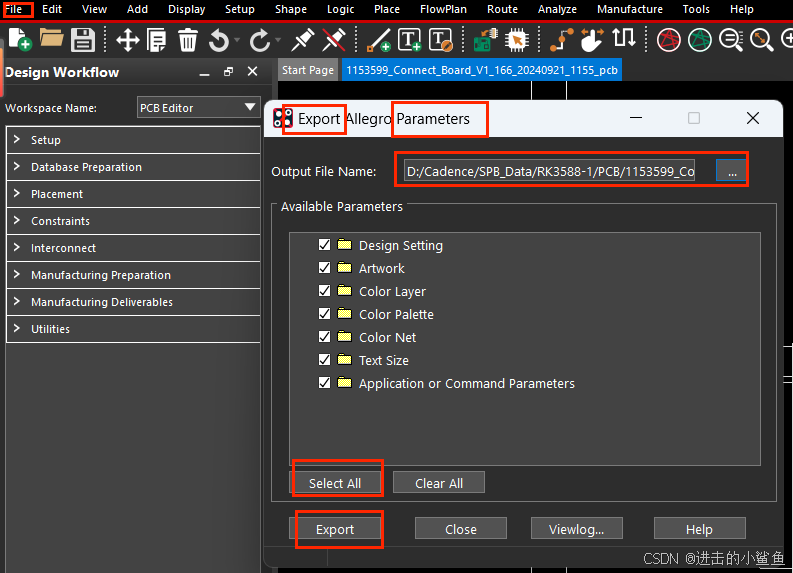

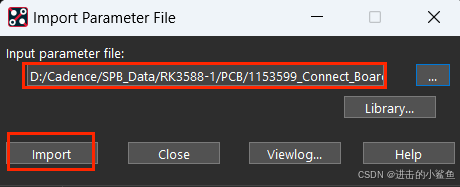

1、先从含有想要颜色搭配的PCB工程中Export.

2、再在新PCB工程中Import

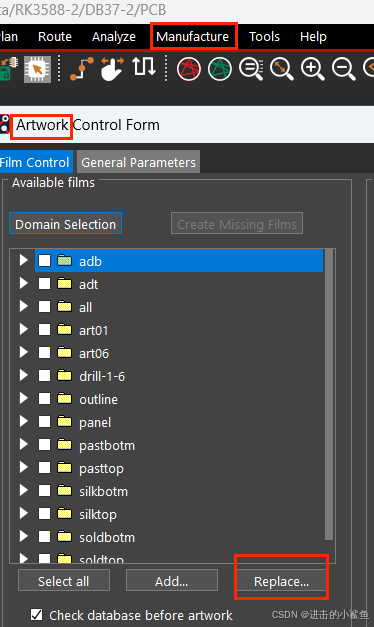

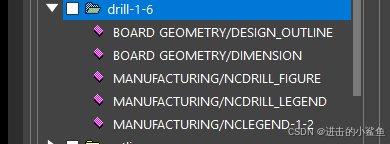

6、光绘层叠

光绘层叠可以在自己的第一个工程中设置好,导出,存放在文件夹中,下次直接导入新的工程中。

钻孔文件每次都要重新生成,替换下。

三、布局

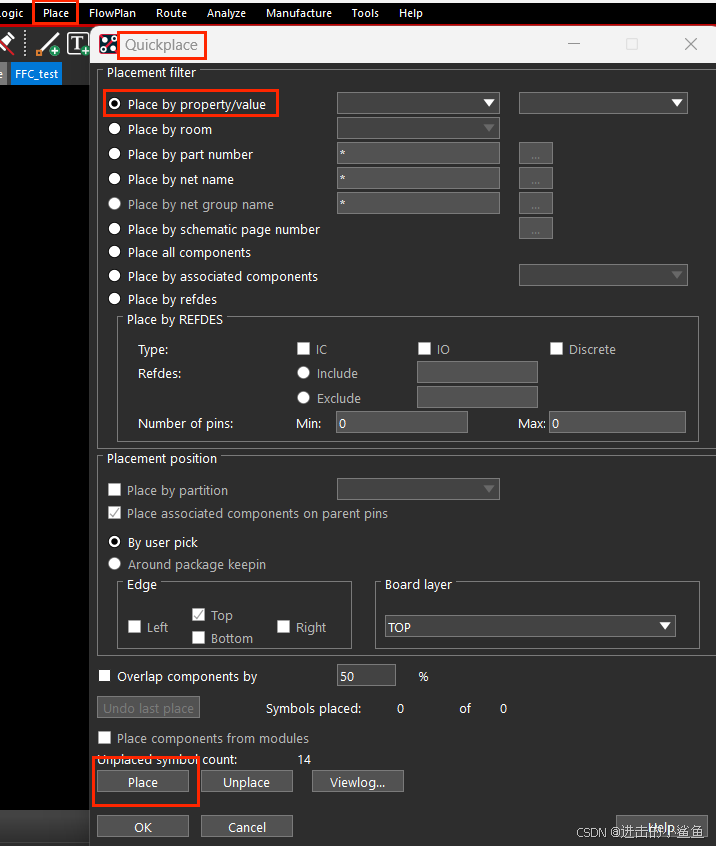

1、快速放置器件

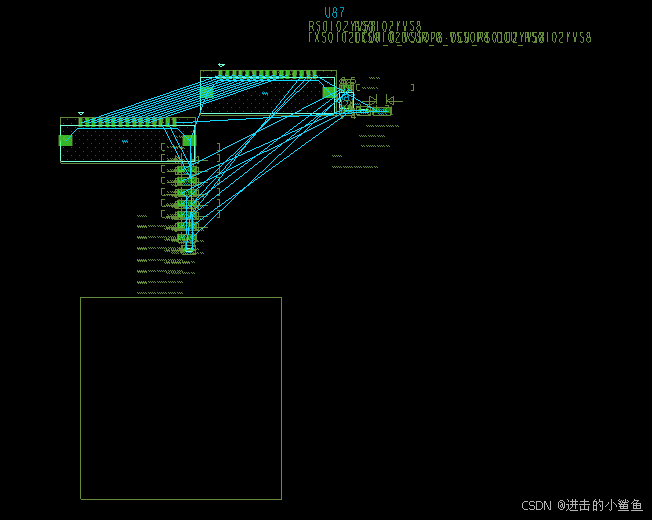

放置完如下图:

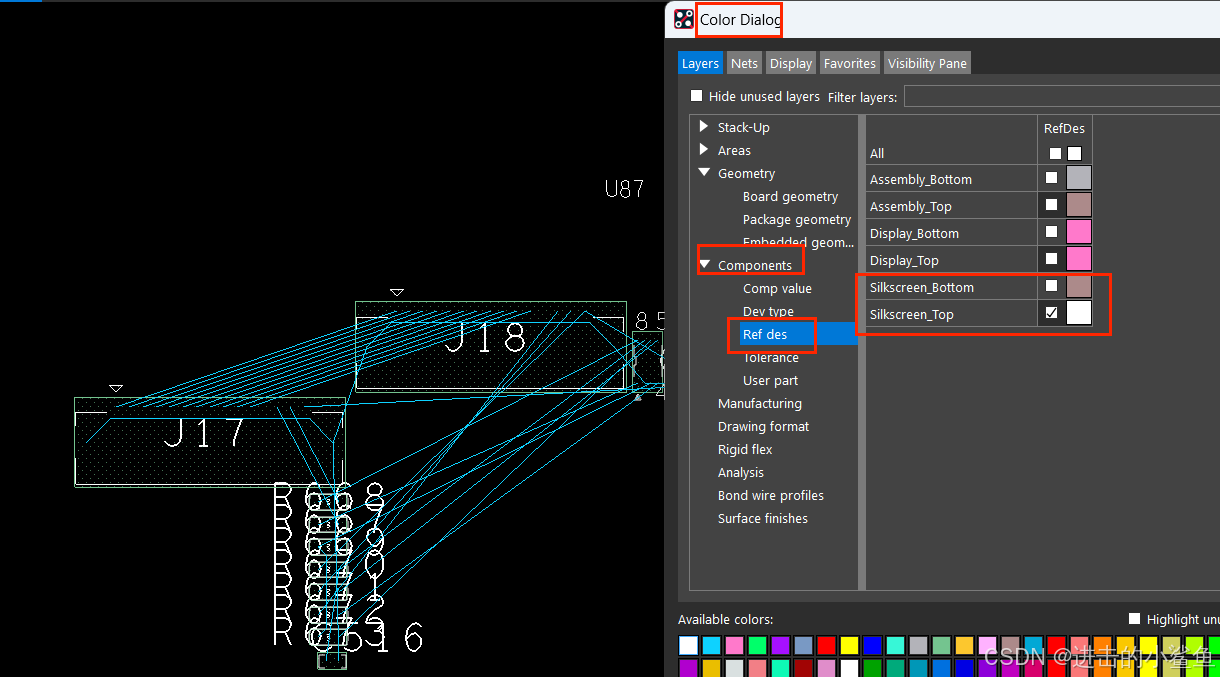

2、选择性展示

如上图,封装的所有信息都展示出来,显得杂乱。

选择性展示操作如下:

1、显示器件位号:

2、元器件引脚号所在层Package Geometry-Pin_Number,打开即可显示引脚号。

3、打开需要关心的类。

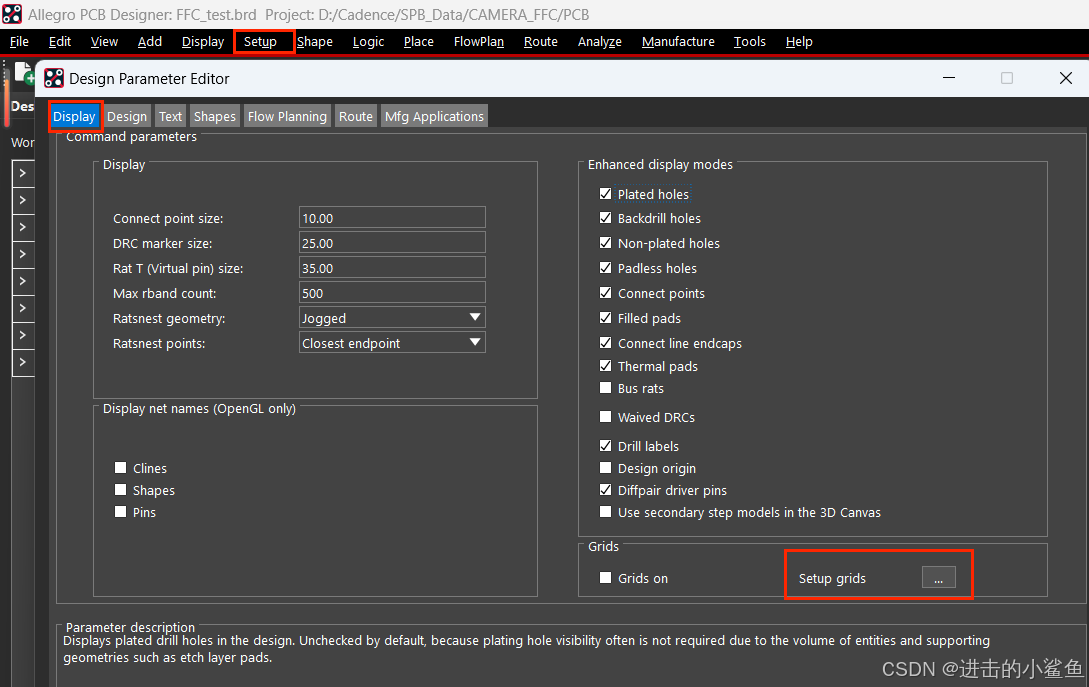

3、修改格点密度、板框大小

修改格点密度:Setup->Design Parameter

修改板框大小:

四、布线

1、布线前操作

1.1、差分对添加与计算

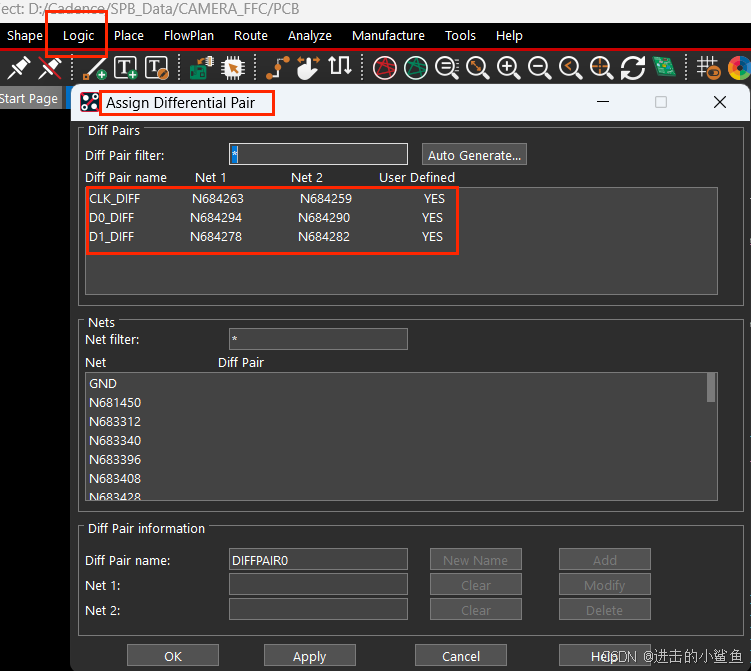

1.1.1、差分对添加

1、手动添加

2、规则管理器添加

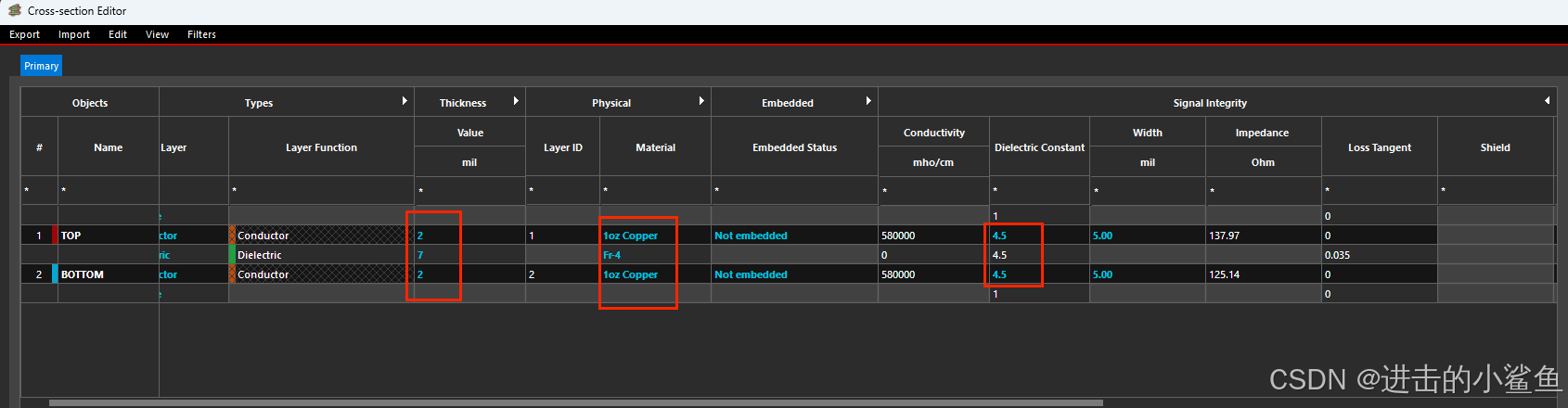

1.1.2、计算线宽与线距

根据确定的阻抗,不同的叠层会得到不同的线宽、线距。

设计好叠层,包括层厚,材料,电导率。调整单端线的粗细,来改变阻抗。越粗阻抗越低。

调整差分线的粗细和间隔。越粗,间隔越小,阻抗越低。

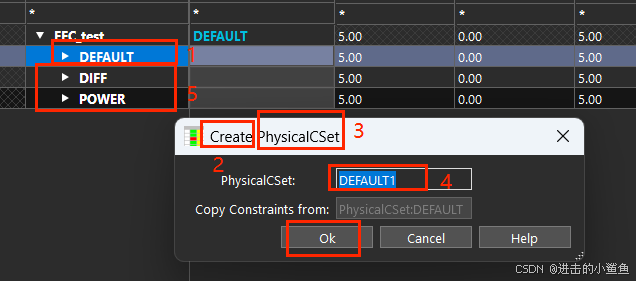

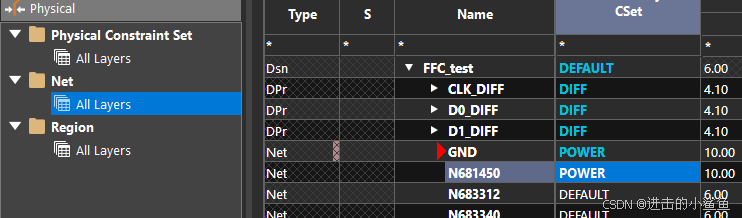

1.2、线宽、线距规则添加

1.2.1、线宽

1、规则添加:

差分线、电源线的线宽单独设置。

2、规则驱动

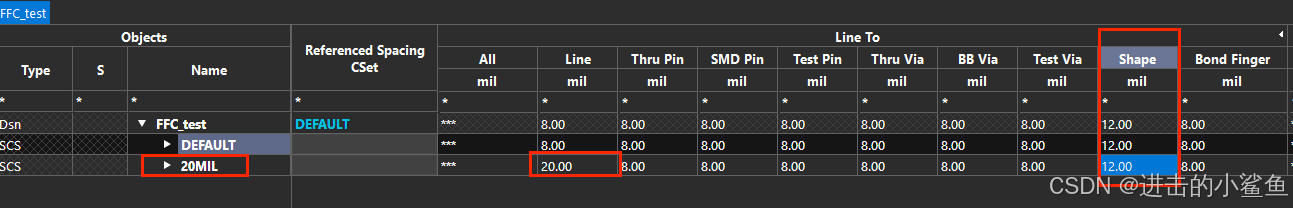

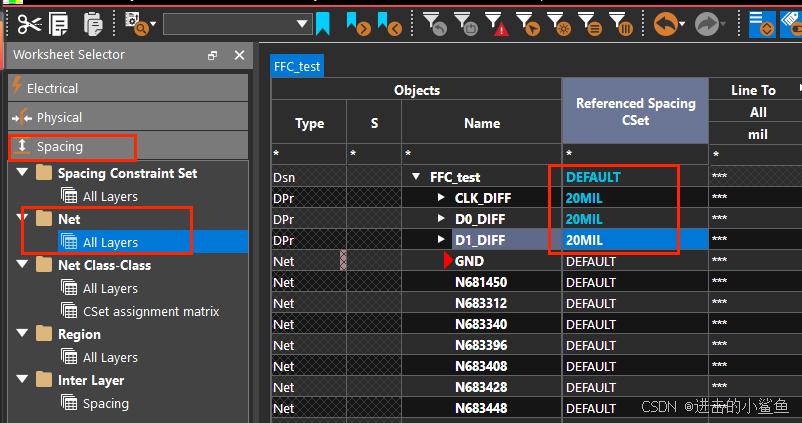

1.2.2、线距

1、规则添加

2、规则驱动

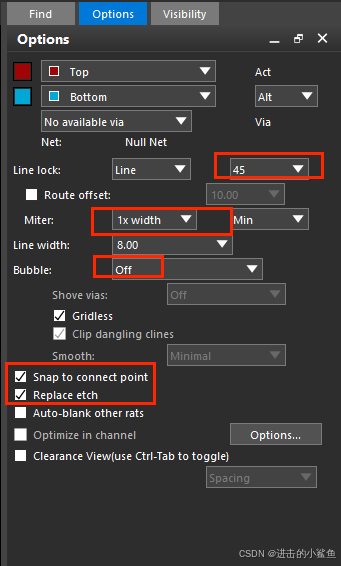

2、布线操作

2.1、走线

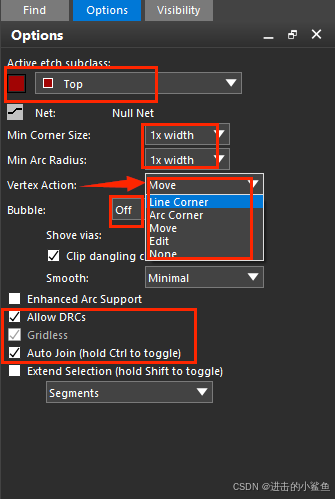

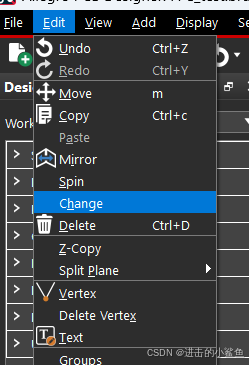

按照下图设置:

Snap to connect point:自动捕捉走线的连接点,一般是勾选此选项;

Replace etch:去除环路走线,当走线形成环路、多余的线路时候,系统就会自动去除另一条线路,一般是勾选此选项的;

2.2、修线

2.2.1、推挤线和过孔

Active etch subclass:当前需要修线的层;

Vertex Action:推挤走线时,端点所做的处理,有以下几个选项;Line corner:推挤走线的拐角;

Arc corner:推挤圆弧的拐角;

Move:推挤整条线;

None:不推挤拐角;

2.2.2、批量修改线宽

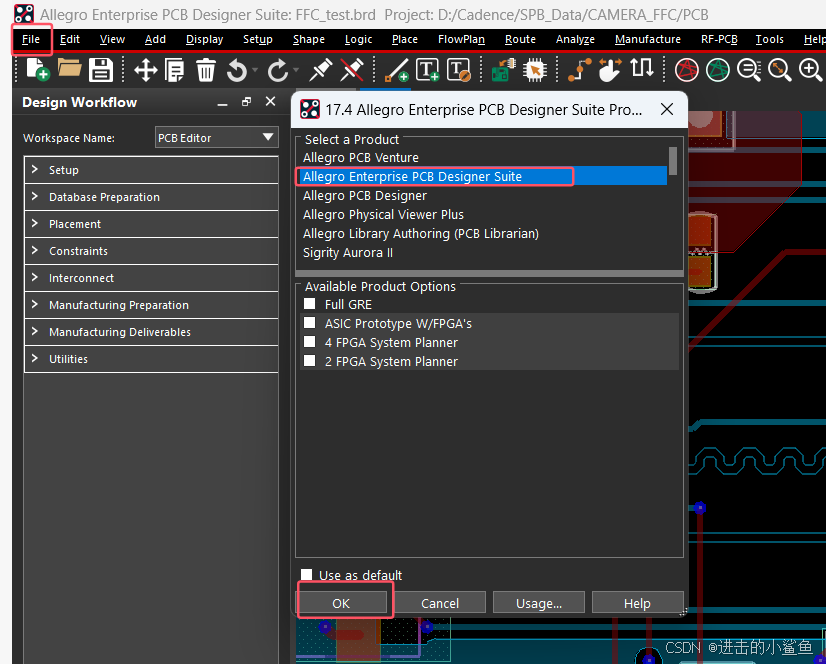

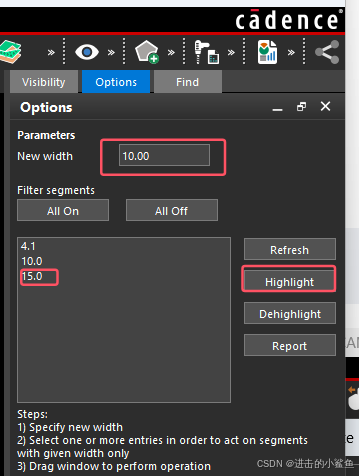

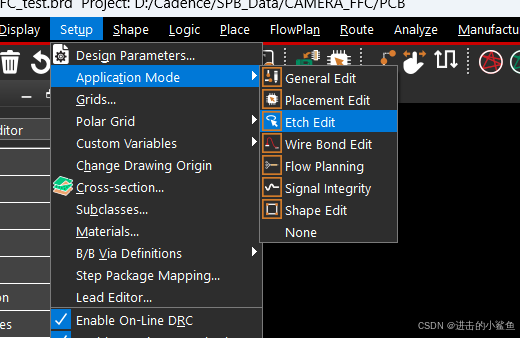

allegro自带的命令:“tbx changewidth” 就可以修改。不过Allegro pcb要换高级的工具,如下:

file->change editor->选择高级工具->ok

设置新的线宽->选中需要修改的旧的线宽->可以选中高亮->框选或点击原理图中需要修改的线->done

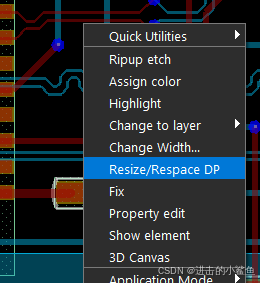

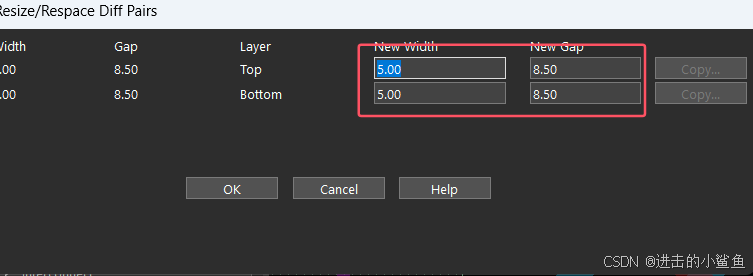

修改差分线的线宽和线距

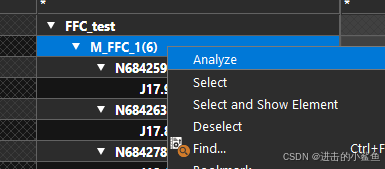

Find 只选中Net>放在需要修改的差分线上>右击

2.3、等长规则添加

先连线,再设置等长规则。

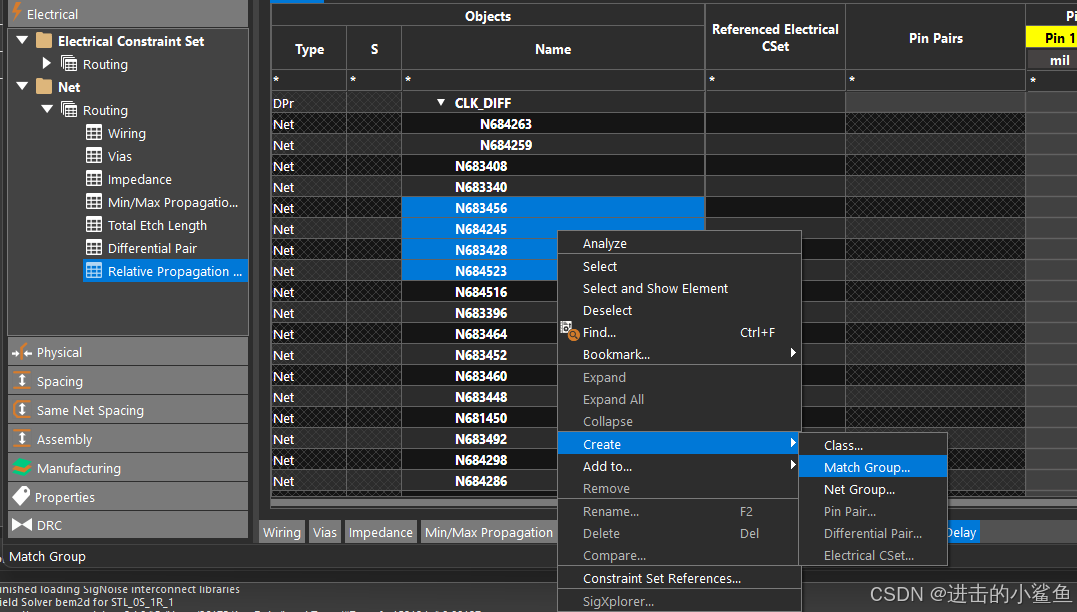

2.3.1、选择需要等长的线,右键,选择Match Group.如下图:

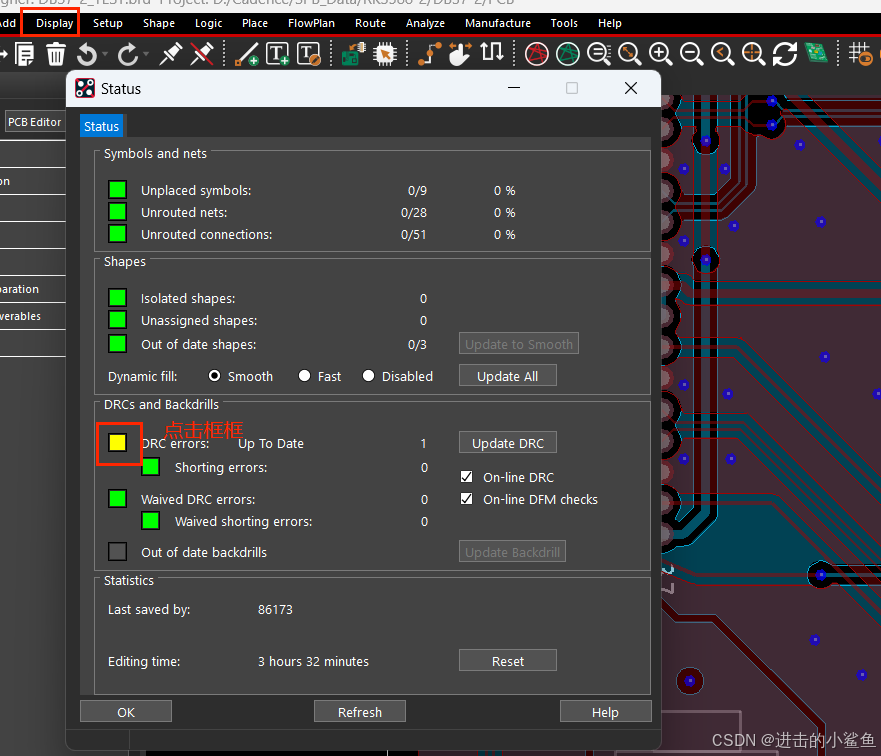

2.3.2、如果出现下面黄色块,有两个原因:

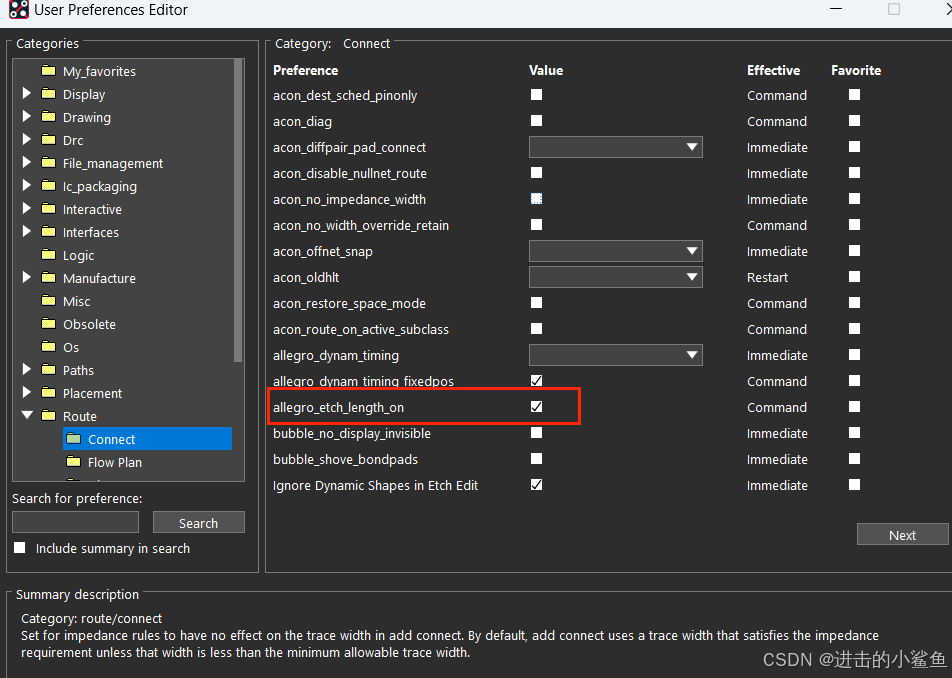

1、有线还未连通。

2、两个位置需要打钩。如下图:

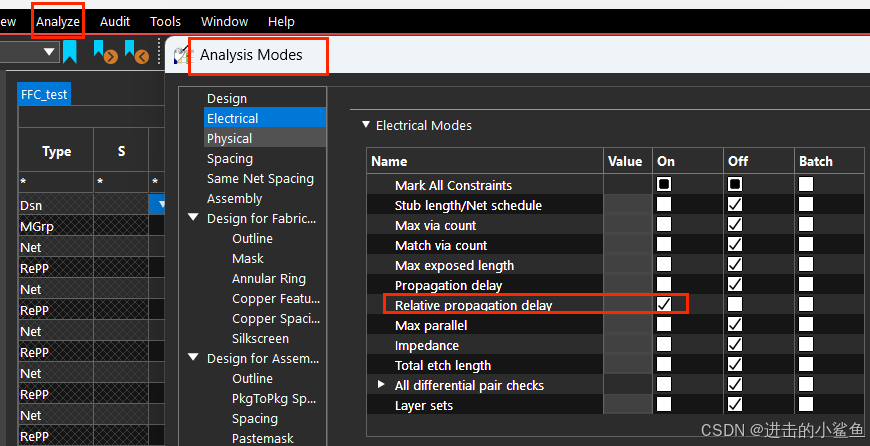

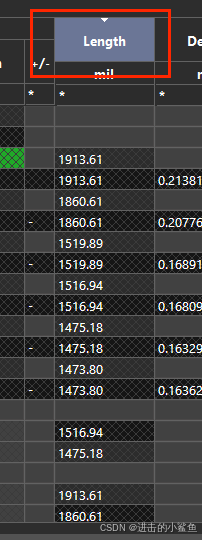

2.3.3、没显示长度

右键,Analyze。再点Length排序。

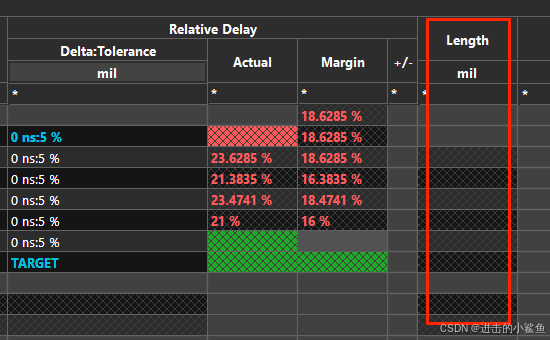

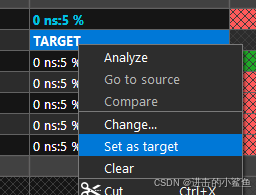

2.3.4、选择同一Match中最长的线最为基准。

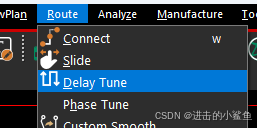

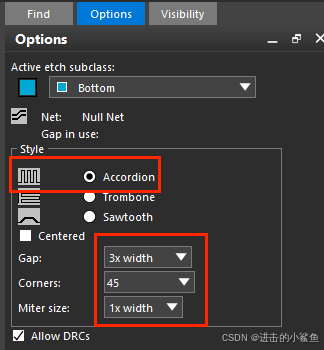

2.3.5、开始蛇形等长

回到主界面

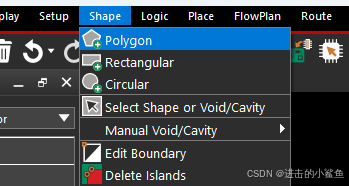

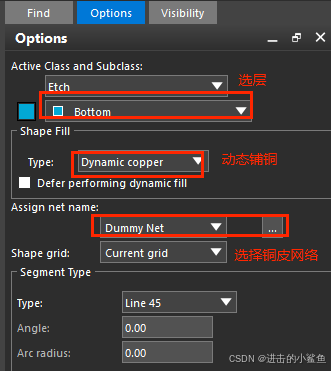

2.4、铺铜

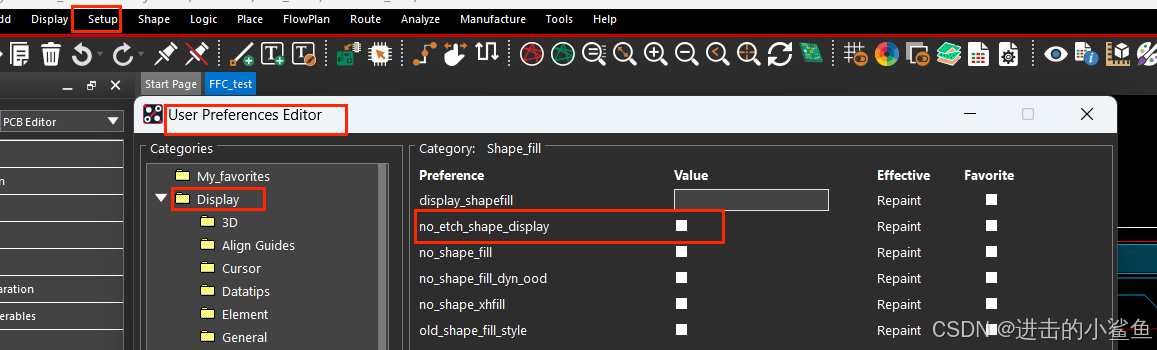

隐藏铺铜

2.5、自动布线

Allegro自动布线只可以作为参考

五、后续检查调整

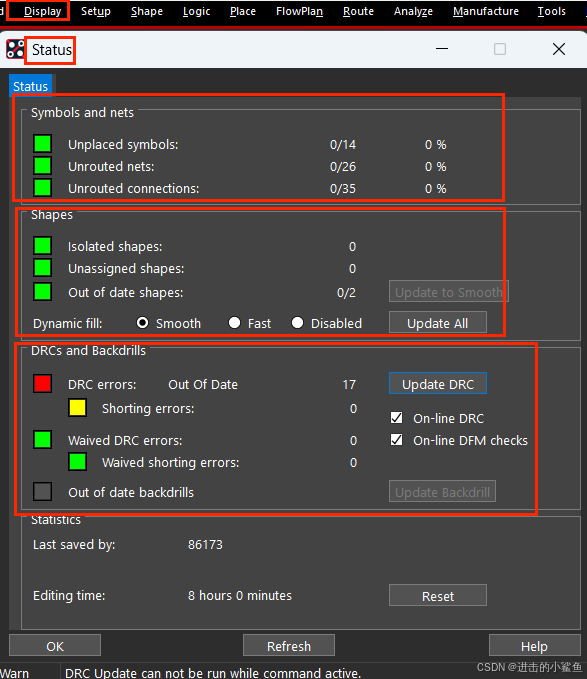

1、状态检查

DRC红色不行

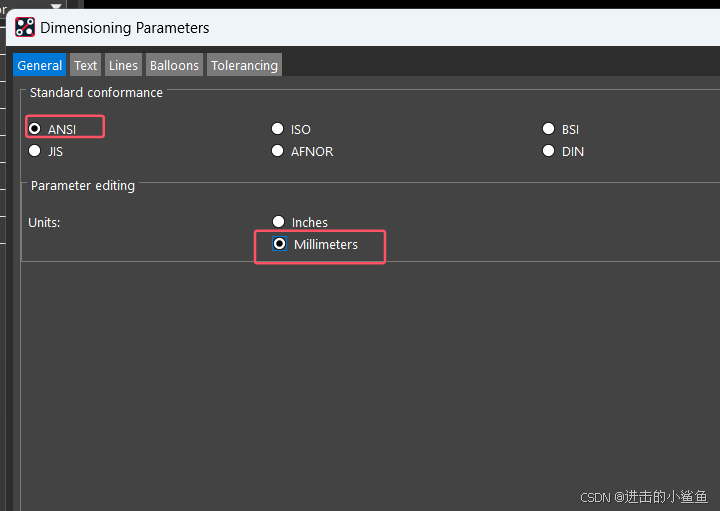

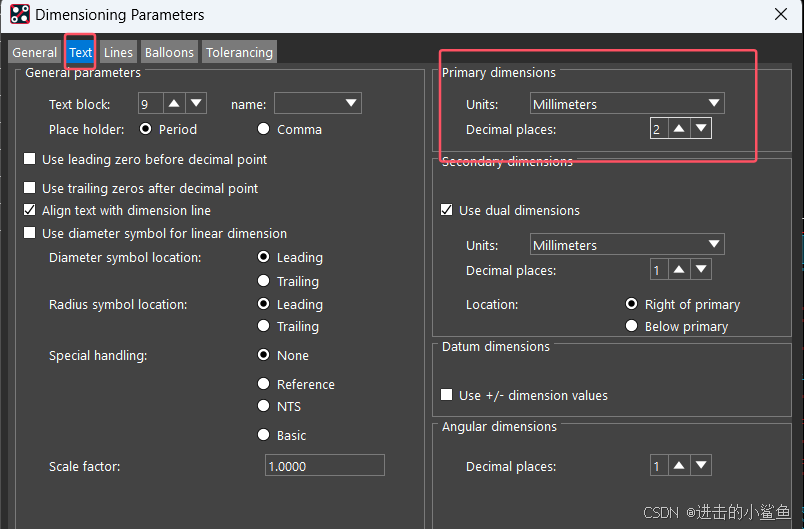

2、尺寸标注

标注设置如下两幅图

Manufacture->Dimension-Environment->parameters

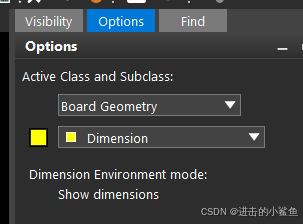

注意标注的层

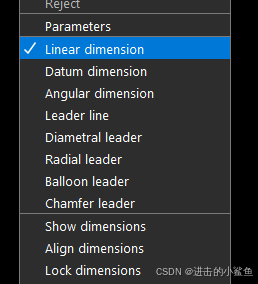

右键->下图是直线标注

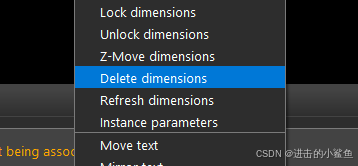

删除标注

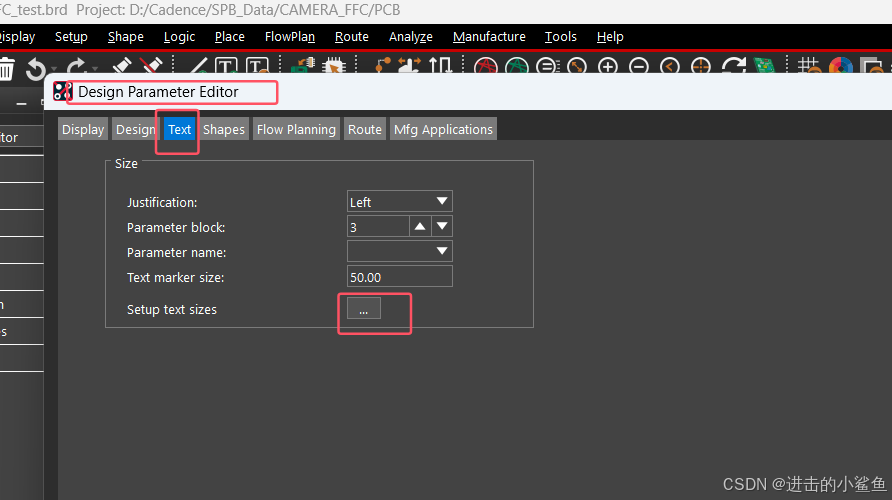

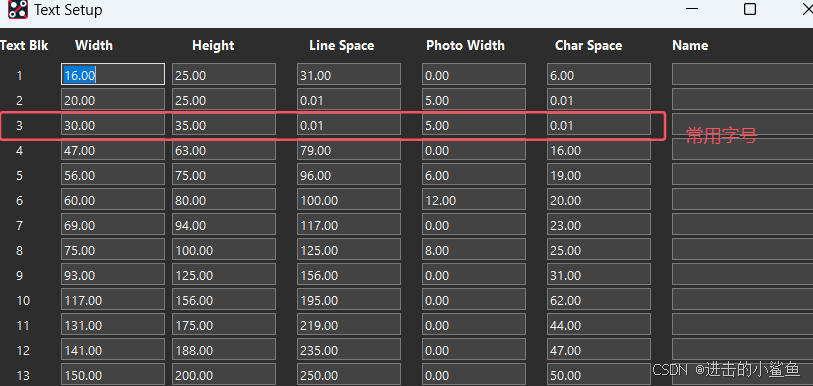

3、字符调整

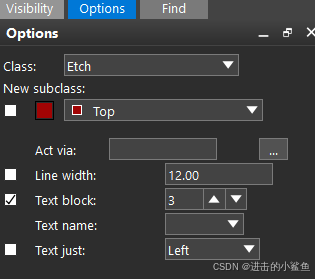

设置一个常用字符

按照下面修改后,框选需要修改的字符。

六、文件导出

可以点击下方链接进入单独的导出PCB所需文件的笔记

Allegro PCB17.4所需导出文件的详细说明

七、出现的问题

1、allegro pcb右侧option视框没了

“view”–“windows”,勾选“options”即可。

2、allegro pcb差分线为什么不能同时走

点击连线命令->放在差分的焊盘上->右键->关闭Single Trace Mode

3、差分线距的含义

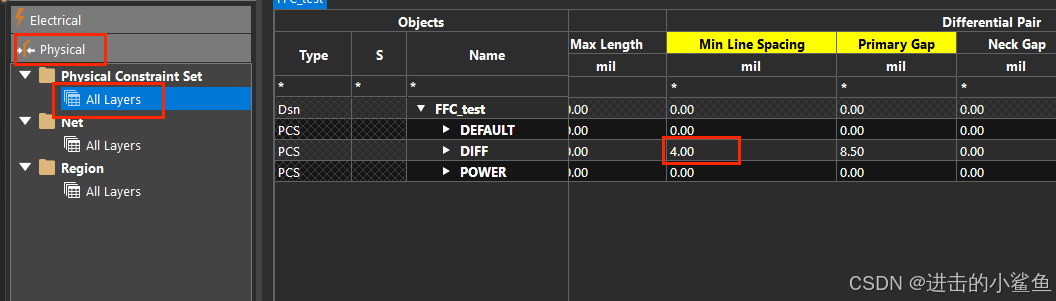

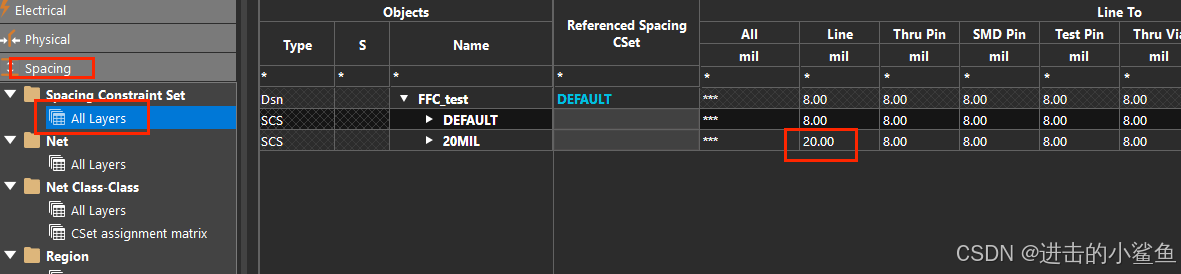

规则添加中,下图中8.5是同一对差分线中线到线的距离。

Min Line Space不能设置为零,因为为0时,差分对走线,线距是8.5mil,但是会因小于20mil报错。

下图中20mil,是差分线对到差分线对的距离。

4、低版本Allegro看不了高版本的

通过下面步骤可从17.4降低到17.2

5、报错

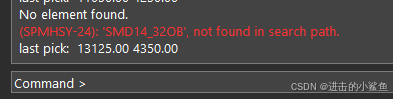

5.1、放置器件缺少焊盘文件

Cannot load symbol 'TDFN_3X3_8L' because WARNING(SPMHUT-127): Could not find padstack SMD94_63.

是因为缺少焊盘文件

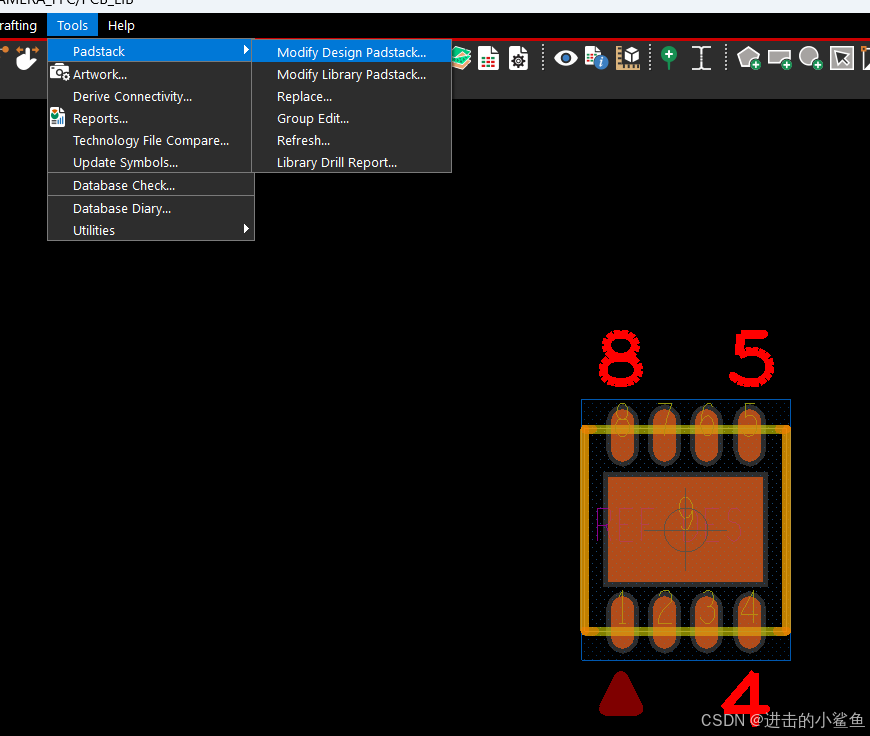

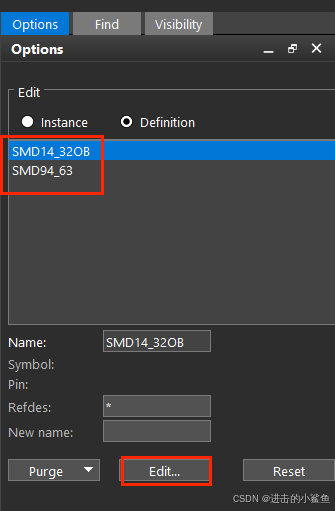

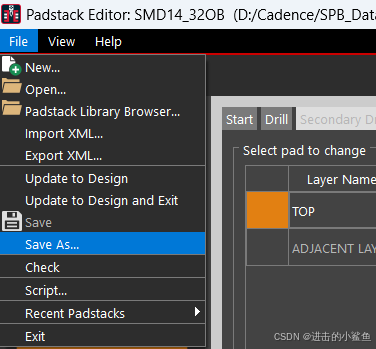

打开器件封装.dra文件,根据下图选择

点击Edit,进入焊盘编辑器,另存为新的焊盘文件。

5.2、导入网表提示封装有非法字符

#1 ERROR(SPMHNI-176): Device library error detected.

ERROR(SPMHNI-164): Problems with device 'CX8836_QFN24L-4*4_CX8836'. JEDEC_TYPE property 'QFN24L-4*4' is illegal: 'Package name has invalid characters or is too long.'.

ERROR(SPMHNI-170): Device 'CX8836_QFN24L-4*4_CX8836' has library errors. Unable to transfer to Allegro.

#2 ERROR(SPMHNI-176): Device library error detected.

ERROR(SPMHNI-164): Problems with device 'CX3075B_1_DNF5*6-8_CX3075B'. JEDEC_TYPE property 'DNF5*6-8' is illegal: 'Package name has invalid characters or is too long.'.

ERROR(SPMHNI-170): Device 'CX3075B_1_DNF5*6-8_CX3075B' has library errors. Unable to transfer to Allegro.

#3 ERROR(SPMHNI-176): Device library error detected.

ERROR(SPMHNI-164): Problems with device 'CX3075B_1_DFN5*6-8_CX3075B'. JEDEC_TYPE property 'DFN5*6-8' is illegal: 'Package name has invalid characters or is too long.'.

ERROR(SPMHNI-170): Device 'CX3075B_1_DFN5*6-8_CX3075B' has library errors. Unable to transfer to Allegro.

#4 ERROR(SPMHNI-176): Device library error detected.

ERROR(SPMHNI-164): Problems with device 'CX3075B_DFN5*6-8_CX3075B'. JEDEC_TYPE property 'DFN5*6-8' is illegal: 'Package name has invalid characters or is too long.'.

ERROR(SPMHNI-170): Device 'CX3075B_DFN5*6-8_CX3075B' has library errors. Unable to transfer to Allegro.

原理图封装中不能有空格 * /

和一些中文字符 如;:“” {} 【】,。

6、错误定位

6.1、报错 dynamic shapes are out of date or enpty

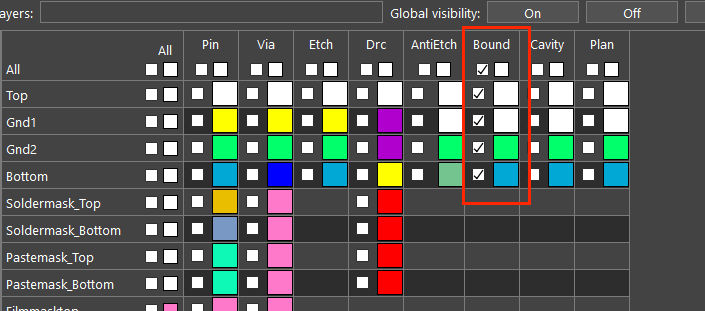

只打开Bound,点击框框定位,删除边线。

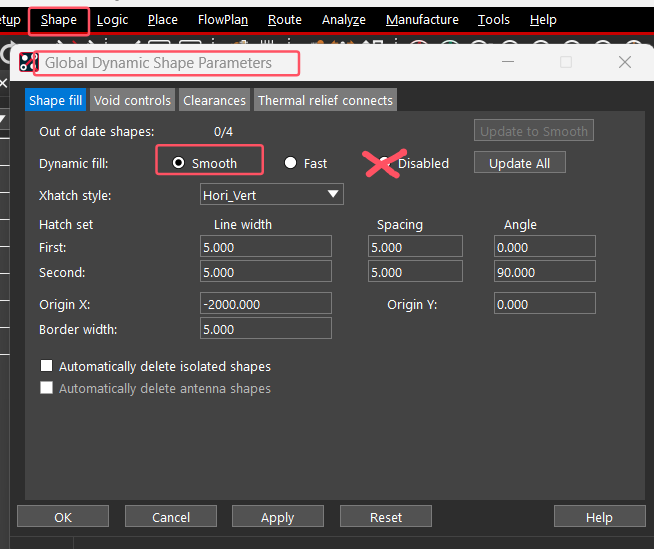

7、切割/挖空铜皮工具功能异常

选中工具想要切割/挖空铜皮的时候,发现挖空不了,但是当你再次编辑该铜皮的时候发现你刚刚用工具框出的框框还显示在这里。这多半是因为覆铜参数设置不对。

八、效果展示

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?