一、原理图设计全加器

1.1 半加器设计

说明:1 位全加器可以用两个半加器及一个或门连接而成, 因此需要先完成半加器的设计。

①新建工程

-

【File】→【New Project Wizard…】

-

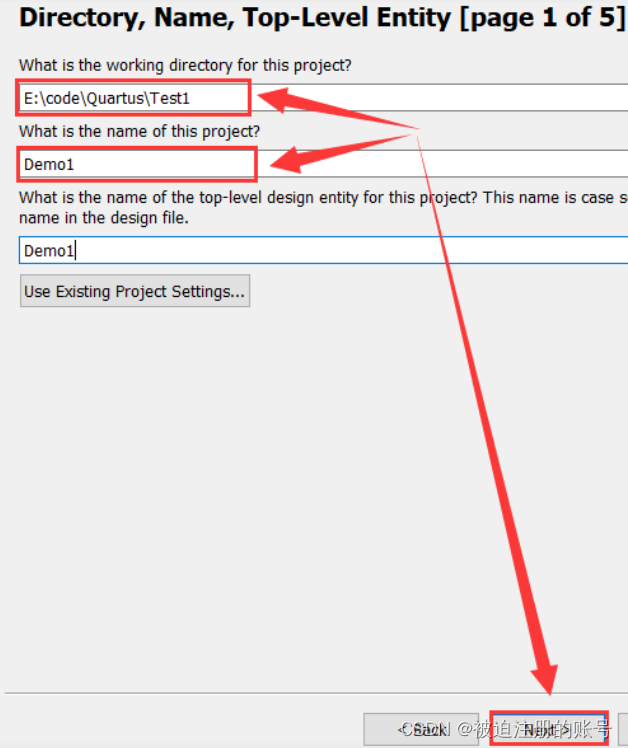

点击【Next】后进入如下界面:选择保存路径及工程名,然后点击【Next】

点击【Next】后进入如下界面:选择【Cyclone IV E】,勾选第二个,选择【EP4CE115F29C7】系列,然后点击【Next】。

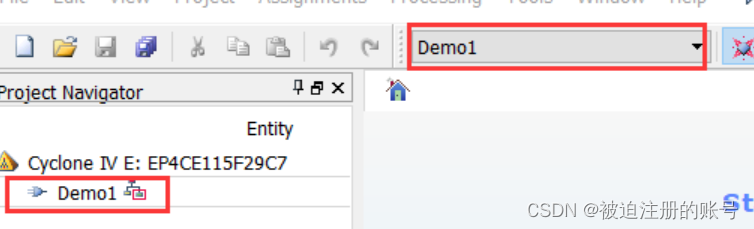

点击【Next】【Finish】后即可完成创建。

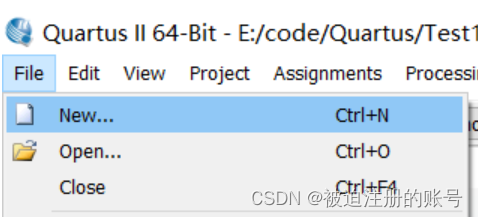

②新建原理图文件

【File】→【New…】。

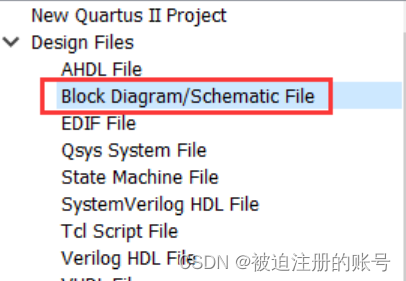

选择【Block Diagram/Schematic File】后点击【OK】

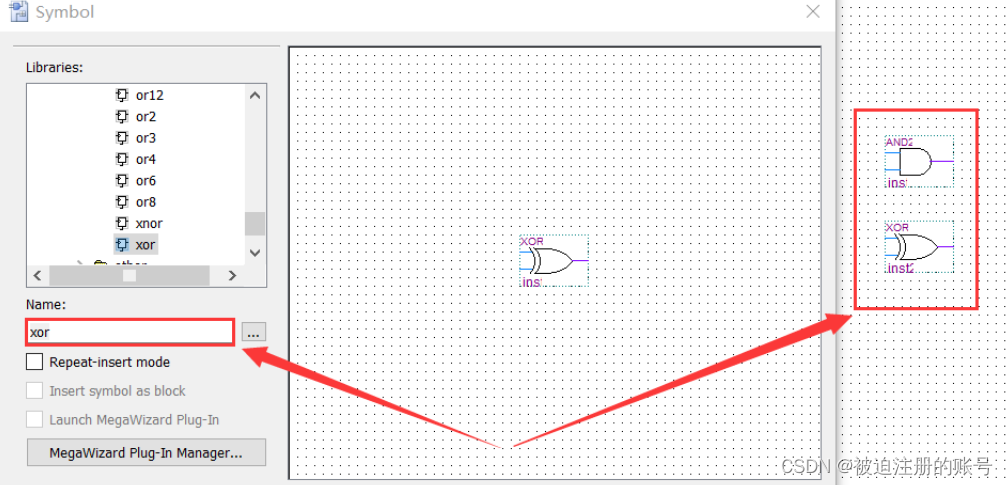

摆放元件:点击插头图样或者双击原理图空白处,调出新窗口

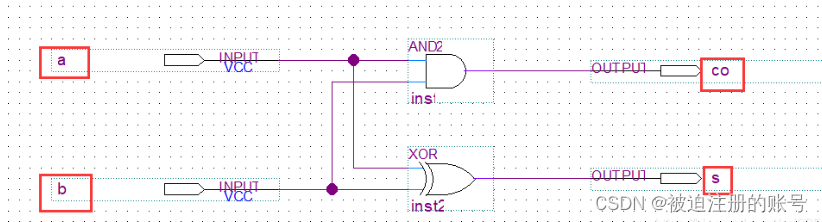

在元件搜索框内输入 and2 和 xor 并摆放到图上

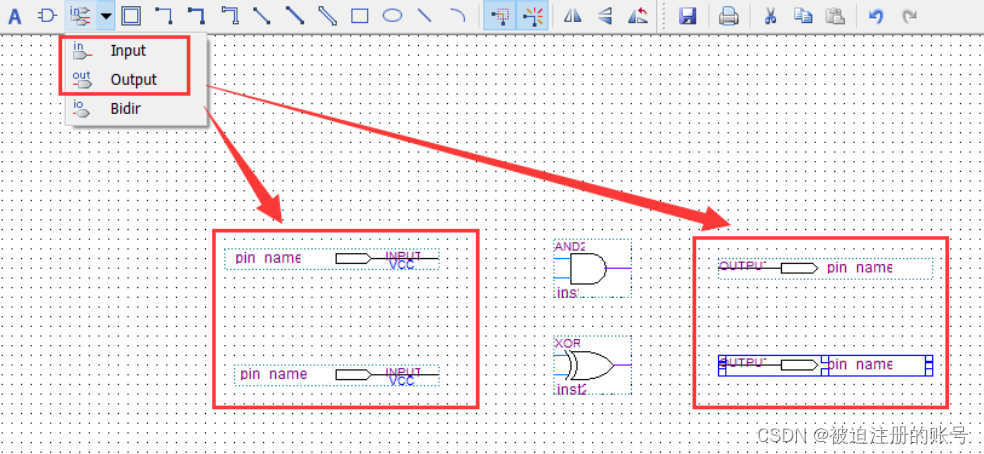

分别摆放两个输入和输出

双击【pin name】修改管脚名,然后用鼠标连接管脚

点击保存按钮,然后点击【保存】

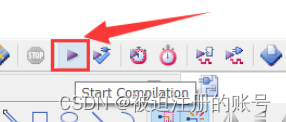

点击【编译按钮】(无错误即可,忽略警告)

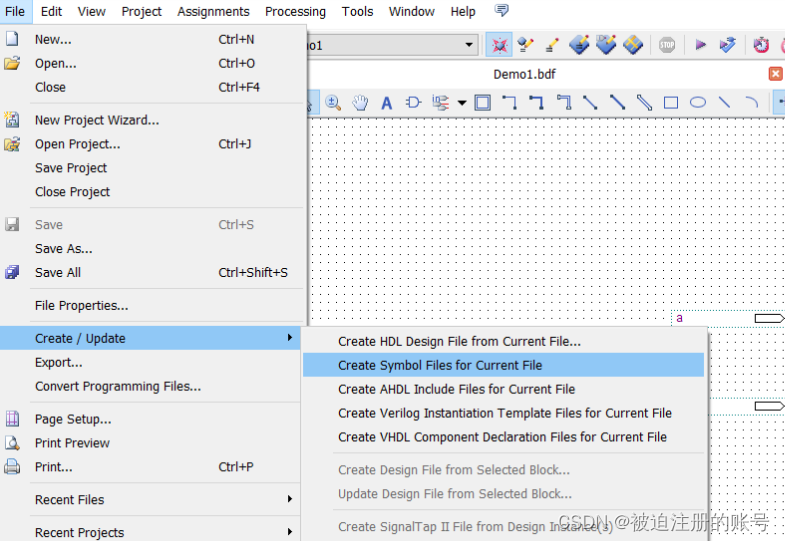

③将设计项目设置成可调用的元件

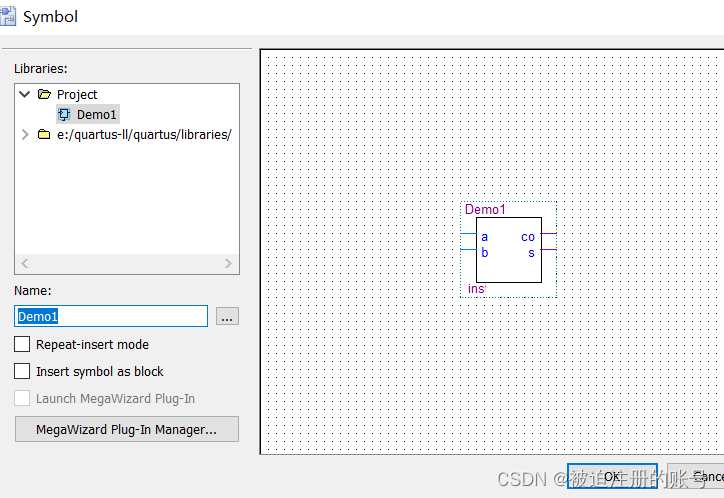

在打开半加器原理图文件【Demo1.bdf】的情况下,选择菜中【File】→【Create/Update】→【Create Symbol Files for Current File】项,即可将当前文件【Demo1. bdf】变成一个元件符号存盘,以待在高层次设计中调用。

接着保存.bsf文件

弹出的窗口点ok

使用完全相同的方法也可以将 VHDL 文本文件变成原理图中的一个元件符号,实现 VHDL 文本设计与原理图的混合输入设计方法。 转换中需要注意以下两点:

1.转换好的元件必须存在当前工程的路径文件夹中;

2.该方法只能针对被打开的当前文件。

④半加器仿真

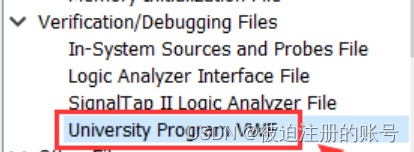

新建波形文件:【File】→【New…】。

选择【University Program VWF】,点击【OK】

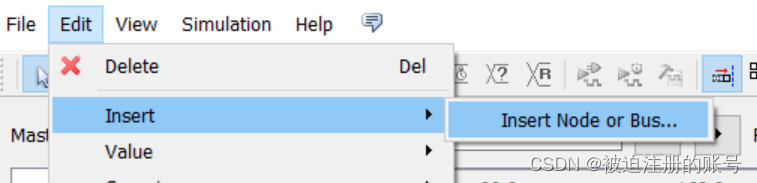

【Edit】→【Insert】→【Insert Node or Bus…】

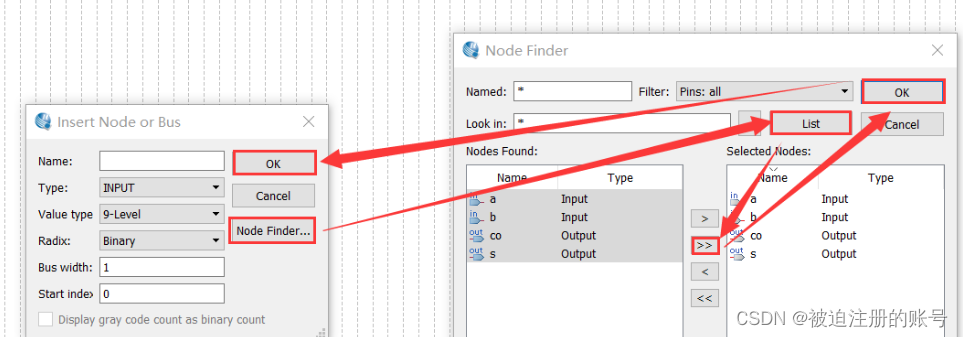

点击【Node Finder】→【List】→【>>】→【OK】→【OK】

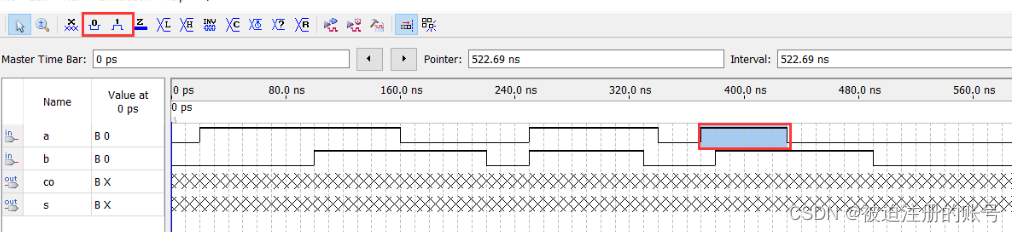

选中要改变电平的区域,然后点击左上方的 “0” “1” 图样即可

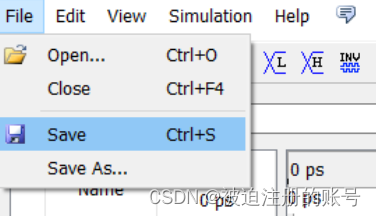

保存 .vwf 文件

直接用默认的文件名和位置即可,否则编译时可能会报错

编译

![]()

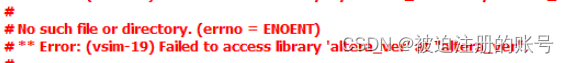

若安装quartus时没有modelsim可能会出现以下错误

解决方法:

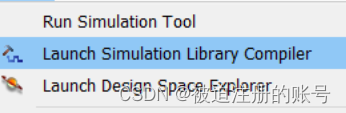

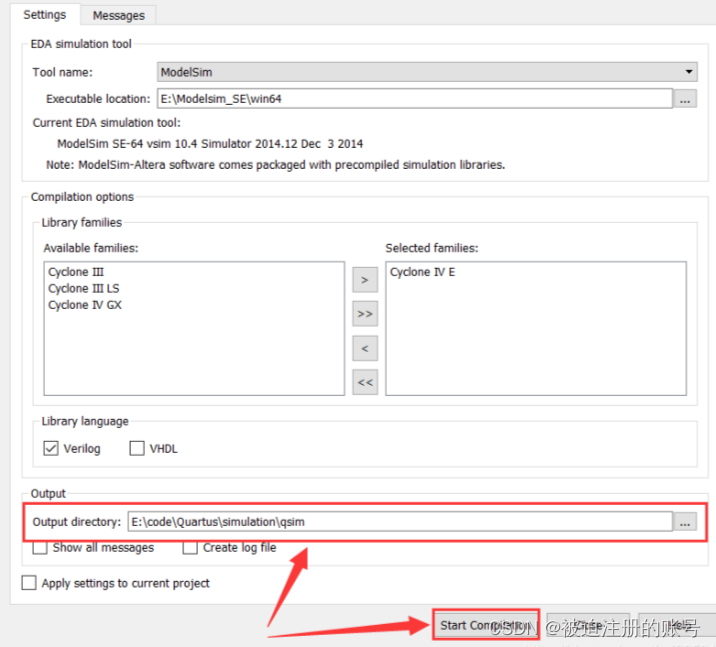

点击【Tools】→【Lauch Simulation Library Compiler】

选择工程目录下的 ...\simulation\qsim 文件夹,然后点击【Start Compilation】

无错误,然后点击ok,【Close】关闭窗口

再次编译即可

若quartus安装时已经自带了modelsim模块,则不会出现上面的错误,出错可以尝试删除vwf文件重新生成按照默认文件名位置保存

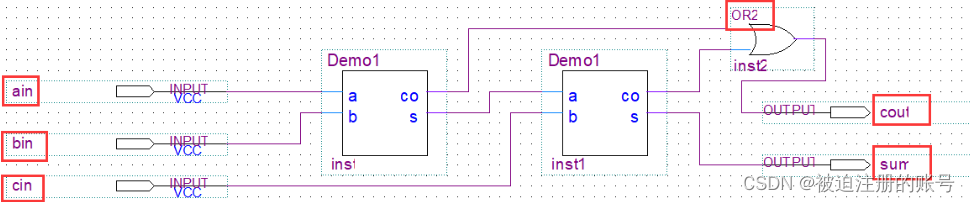

1.2 全加器设计3

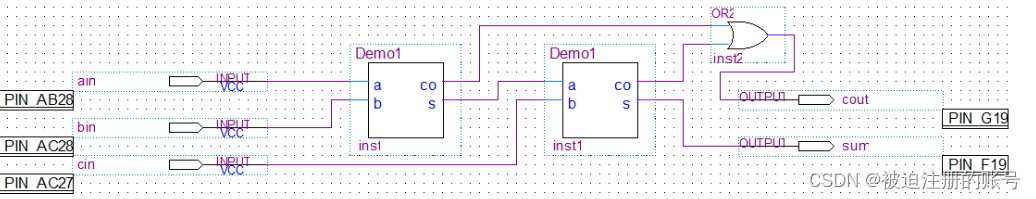

①新建原理图

新建一个原理图文件,方法同上。 添加上面创建的半加器,命名

编辑原理图如下:

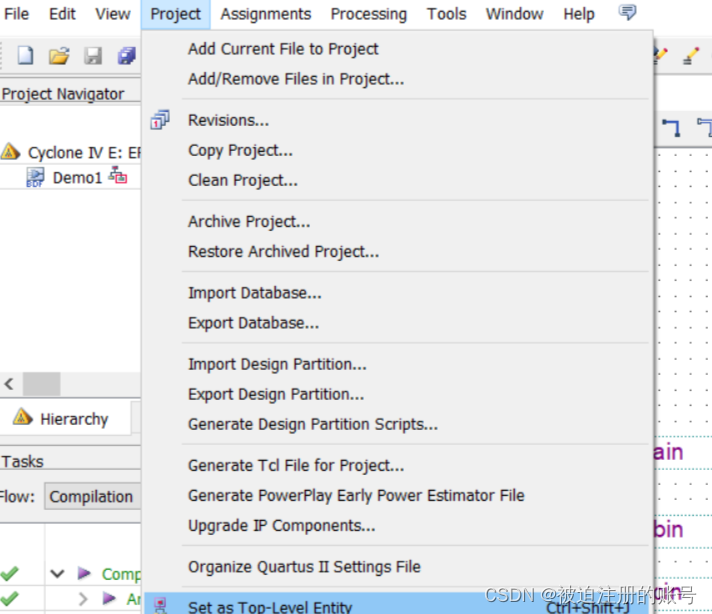

保存文件。 ②将设计项目设置成顶层文件并编译仿真

③全加器仿真

二、Verilog实现全加器

1位全加器

①创建 Verilog 文件

【File】→【New…】

选择【Verilog HDL File】,点击【OK】

输入代码

module Verilog1(

//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

input ain,bin,cin,

//输出信号,cout表示向高位的进位,sum表示本位的相加和

output reg cout,sum

);

reg s1,s2,s3;

always @(ain or bin or cin) begin

sum=(ain^bin)^cin;//本位和输出表达式

s1=ain&cin;

s2=bin&cin;

s3=ain&bin;

cout=(s1|s2)|s3;//高位进位输出表达式

end

endmodule

然后保存文件。

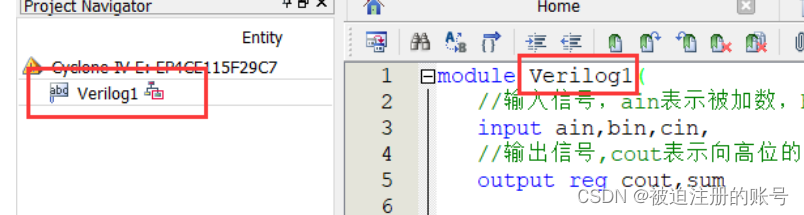

说明:需要将第一行的 Verilog1 更改为自己的 Verilog 文件名才行,否则会报错

将 Verilog 文件设置为顶部文件,否则编译不到

编译 Verilog 文件

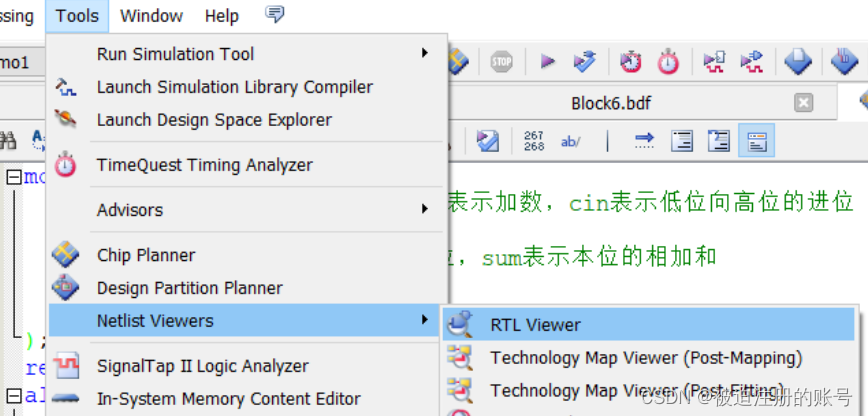

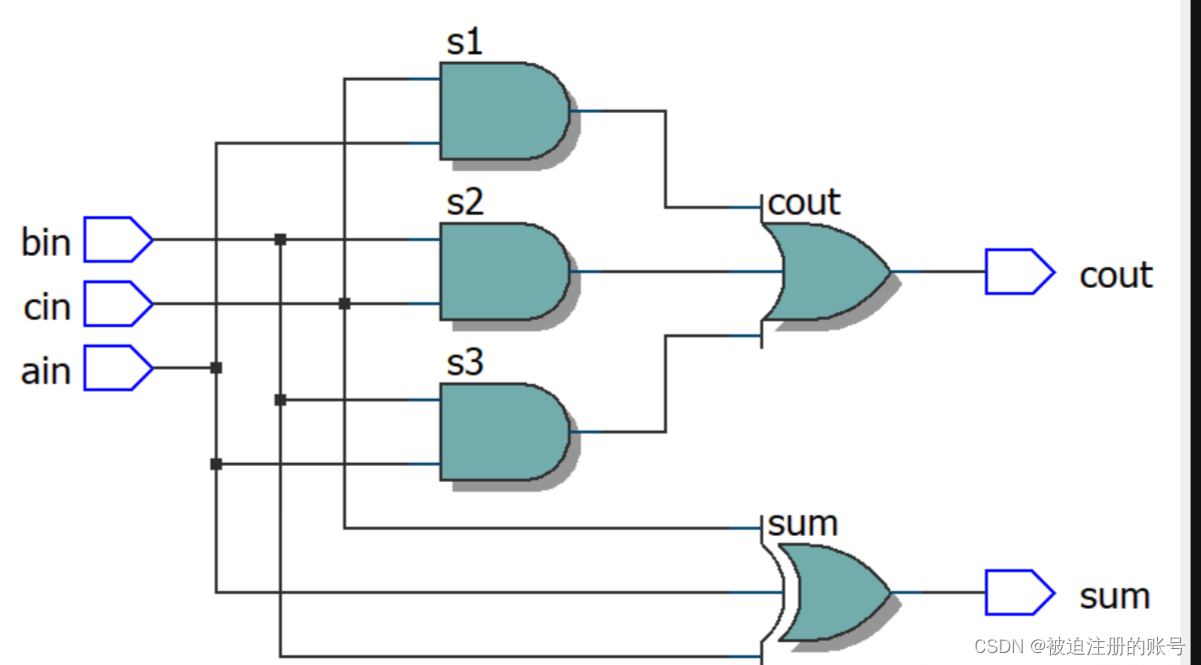

通过【Tools】→【Netlist Viewers】→【RTL Viewer】查看电路图

②仿真实现

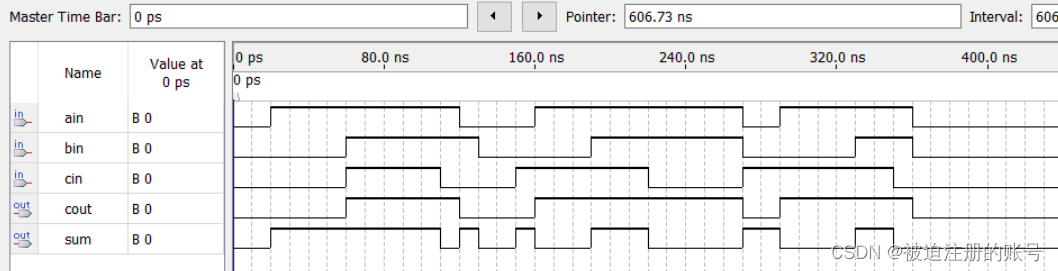

步骤和上面的仿真步骤一样,这里就不再重复了。 结果如下:

4位全加器

代码

module Verilog2 (

input A, B, Cin,

output Sum, Cout

);

// Full Adder logic

assign {Cout, Sum} = A + B + Cin;

endmodule

module FourBitAdder_functional_level (

input [3:0] A, B, Cin,

output [3:0] Sum,

output Cout

);

wire c1, c2, c3;

FullAdder_functional_level fa1(A[0], B[0], Cin, Sum[0], c1);

FullAdder_functional_level fa2(A[1], B[1], c1, Sum[1], c2);

FullAdder_functional_level fa3(A[2], B[2], c2, Sum[2], c3);

FullAdder_functional_level fa4(A[3], B[3], c3, Sum[3], Cout);

endmodule

电路图

三、下载文件到开发板上

3.1 引脚绑定

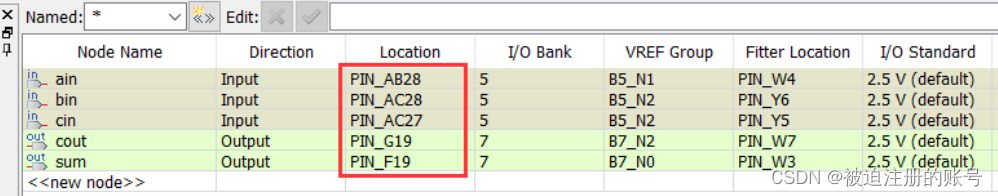

开发板上的18个拨码开关选其中三个:SW0、SW1、SW2 分别接 ain、bin、cin(开关向上拨和向下拨分别显示输入是高还是低电平) LED0、LED1 分别接 cout 和 sum,灯亮表示输出为 “1”,灯灭表示输出为 “0”。 硬件设计好后,还需要查引脚图进行引脚绑定,如图:

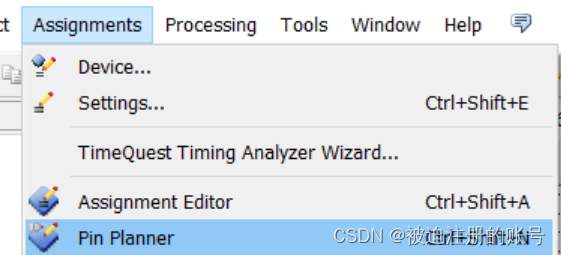

开始绑定引脚:点击【Assignments】→【Pin Planner】

选定了引脚之后原理图文件一定要再编译一次,才能真正把引脚绑定上

3.2 烧录文件

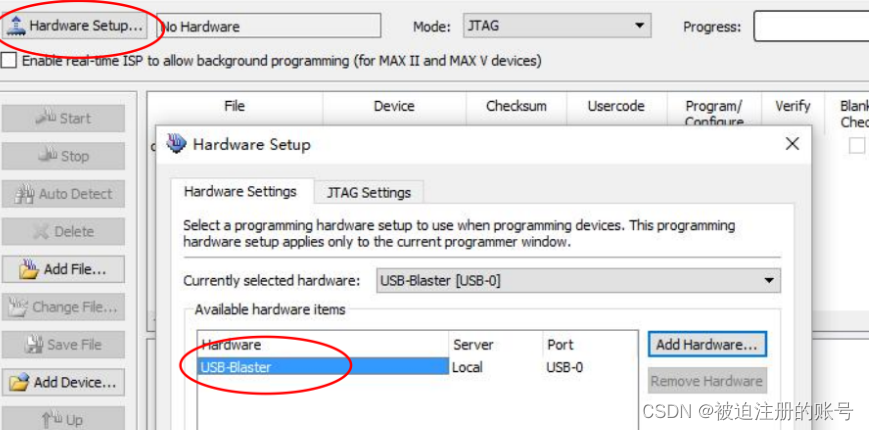

现在可以下载到硬件上进行测试了。 把开发板接上电源,USB 接口接电脑。打开电源开关(注意不用下载时请一定关闭开关,以免烧坏板子)。

点击tool,选择programmer

第一次下载需安装硬件:即在下载界面中点击按钮【hardware setup…】,然后在弹出的对话框中选择【USB blaster】,再点击【ok】,则硬件被安装上

现在可以下载到硬件上进行测试了。 把开发板接上电源,USB 接口接电脑。打开电源开关(注意不用下载时请一定关闭开关,以免烧坏板子)。

点击tool,选择programmer

第一次下载需安装硬件:即在下载界面中点击按钮【hardware setup…】,然后在弹出的对话框中选择【USB blaster】,再点击【ok】,则硬件被安装上

勾选上,点击【Start】,烧录成功

如果没有检测到硬件,说明没有安装相应驱动,下载安装即可

四、总结

使用 Quartus 来仿真十分的方便,整个过程也并不复杂,配置开发板使用更加的直观,有一定的数字电路基础后,再来使用这个软件来仿真,就会得心应手。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?