SystemVerilog Assertions 应用指南学习笔记(一)

断言

什么是断言?

为什么使用SystemVerilog Assertion(SVA)?

SVA术语

SVA中定义了两种断言:即时断言和并发断言

并发断言

即时断言

SVA块

举个例子:如下所示,就是一个property里如何嵌套sequence

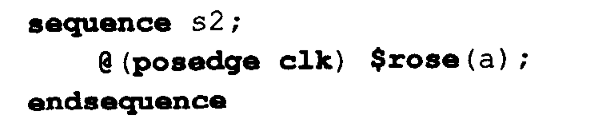

边沿定义的序列

举例:

逻辑关系的序列

序列复用

时序关系的序列

需要注意:序列s4的开始时间和结束时间不同。

如果信号“a”在任何时钟周期不为高电平,序列在同个时钟周期开始并失败。

如果信号“a”是高电平,序列开始。在两个时钟周期后,如果信号“b”是高电平,序列成功(第5和第14时钟周期)。另一方面,如果在两个时钟周期后,信号“b”不是高电平,序列失败。

应注意的是,在图中,成功的序列总是标注在序列开始的位置。

SVA中的时钟定义

通常情况下,在property中定义时钟,使sequence独立于时钟是一种好的编码风格

禁止属性

9139

9139

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?