1.概述

雷达硬件加速器(Radar Hardware Accelerator)是一种硬件IP,可以从主处理器的FMCW雷达信号处理中卸载某些常用计算的负担,也就是不需要主处理器参与计算,可直接通过控制启动HWA进行相关专用计算。

目前HWA可以处理的一些雷达信号的计算主要包括windowing, FFT, magnitude, log2, CFAR-CA等。

2.体系结构

2.1 总体结构

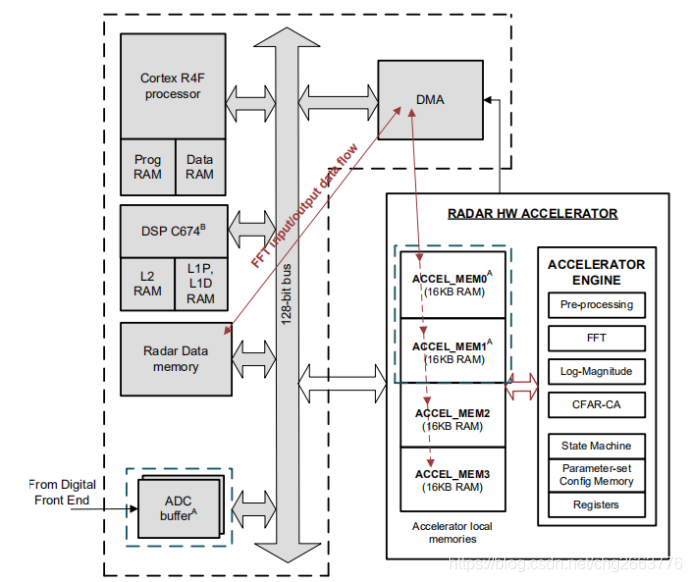

1)总体数据流:

典型的数据流是利用DMA模块将采样点数据(例如FFT输入采样)从雷达数据存储器(Radar Data memory)中传入雷达硬件加速器的本地存储器中(ACCEL_MEMx),使主加速器引擎能够访问和处理这些采样数据。主加速引擎会根据配置进行相对应的计算处理。一旦加速器处理完成,DMA模块从雷达硬件加速器的本地存储器读取输出数据,并将它们存储回雷达数据存储器中,供主处理器进一步处理。

2)数据Ping-pong机制:

对于输入和输出,DMA写(和读)操作可以与加速器的主要计算处理同时发生。四个本地存储器(ACCEL_MEMx)的存在实现了这种并行性。例如,DMA可以被配置为将FFT输入样本(ping)写入到ACCEL_MEM0中,并从ACCEL_MEM2中读取FFT输出样本(ping)。同时,加速器引擎可以从ACCEL_MEM1处理FFT输入样本(pong),并将FFT输出样本(pong)写入ACCEL_MEM3。但是,DMA和加速器都不能同时访问相同的16KB内存。这将会导致一个系统错误。

3)雷达硬件加速器在单个时钟域上工作,时钟频率为200MHZ。加速器的本地存储器为128位宽。

2.2 HWA内部结构

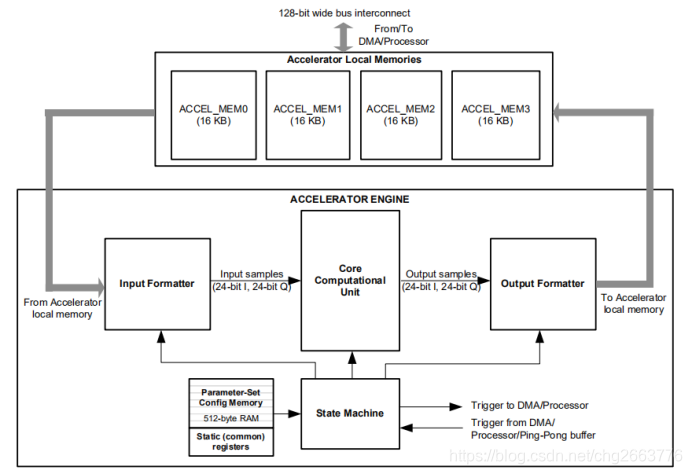

1)状态机(State Machine):状态机负责控制加速器的整体运行——特别是启动、循环、停止以及加速器与主处理器之间的触发和握手机制。状态机还与参数集配置存储器紧密相连,并负责对参数集配置存储器中编程的多个加速器操作序列进行排序和链接。

2)输入格式化器(Input Formatter):输入格式化器负责从任何一个本地存储器中读取输入样本,并将其输入到核心计算单元中。在此过程中,提供了访问输入样本的灵活方法,包括对16位、32位对齐的输入样本、转置读取、灵活的缩放和符号扩展以生成24位的内部位宽等等。最后,输入格式化器块提供24位复杂样本作为对核心计算单元的输入。输入格式化器从中读取输入样本的本地存储器(存储器)称为源存储器。

3)输出格式化器(Output Formatter):输出格式化器负责将核心计算单元的输出样本写入本地存储器。还提供了灵活的格式化输出样本的方法,包括16位与32位对齐的输出样本、转置写入、从24位的内部位宽灵活缩放、到16位或32位对齐的输出样本、符号扩展等。 输出格式化器将输出样本写入的本地存储器(存储器)称为目标存储器。

4)核心计算单元(Core Computational Unit):核心计算单元包含各种操作的主要计算逻辑,如窗口化、FFT、级数、log2和CFAR-CA计算。 该单元接受来自输入格式化器的流输入(以每个时钟周期一个输入样本的速率),执行计算,并向输出格式化器(通常以每个时钟周期一个输出样本的速率)产生流输出,根据所涉及的计算的性质,具有一些初始延迟。

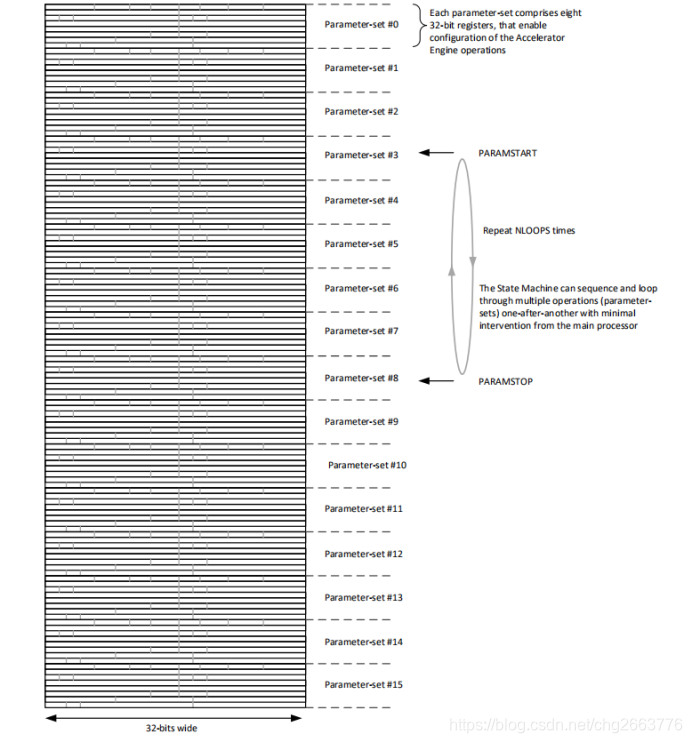

5)参数集配置内存(Parameter-Set Config Memory):这是一个512字节的RAM,用于预配置一个加速器操作的链式序列的参数集(寄存器设置),然后状态机可以在一个循环中执行。这允许加速器在一个循环中执行预先编程的操作序列,而不需要来自主处理器的频繁干预。可以预先配置和排序(链式)的参数集数为16。 这意味着多达16个加速器操作可以被链接在一起,然后这些操作也可以被循环,最小化来自主处理器的干预。

雷达硬件加速器(Radar Hardware Accelerator, HWA)是一种专为减轻主处理器在FMCW雷达信号处理中的计算负担而设计的硬件IP。它能处理windowing、FFT、magnitude、log2和CFAR-CA等计算任务。加速器通过DMA与雷达数据存储器交互,采用数据Ping-pong机制实现并行处理。内部结构包括状态机、输入格式化器、输出格式化器、核心计算单元和参数集配置内存,其中状态机控制整个流程,核心计算单元执行主要计算,参数集配置内存允许预编程操作序列,减少主处理器干预。

雷达硬件加速器(Radar Hardware Accelerator, HWA)是一种专为减轻主处理器在FMCW雷达信号处理中的计算负担而设计的硬件IP。它能处理windowing、FFT、magnitude、log2和CFAR-CA等计算任务。加速器通过DMA与雷达数据存储器交互,采用数据Ping-pong机制实现并行处理。内部结构包括状态机、输入格式化器、输出格式化器、核心计算单元和参数集配置内存,其中状态机控制整个流程,核心计算单元执行主要计算,参数集配置内存允许预编程操作序列,减少主处理器干预。

4122

4122

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?