1. 格雷码定义

在一组数的编码中,若任意两个相邻的代码只有一位二进制数不同,则称这种编码为格雷码(Gray Code),另外由于最大数与最小数之间也仅一位数不同,即“首尾相连”,因此又称循环码或反射码。

2. 转换方法

(1)递归查表法

1位格雷码有2个码字:0和1;

(n+1)位格雷码中的前2^n(2的N次方)个字码等于n位格雷码的码字,按顺序书写,加前缀0;

(n+1)位格雷码中的后2^n(2的N次方)个字码等于n位格雷码的码字,但按逆序书写,加前缀1;

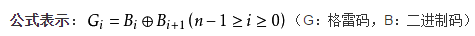

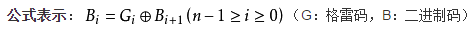

2)异或转换

二进制码→格雷码(编码,i为bit位数):

格雷码→二进制码(解码,i为bit位数):

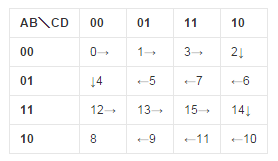

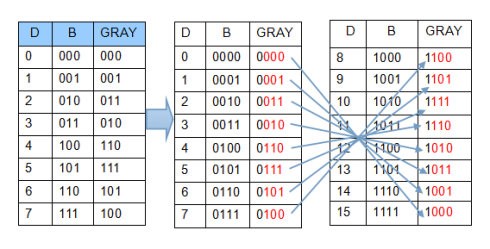

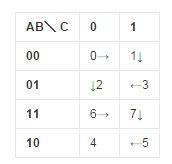

(3)卡诺图

三位格雷码与四位格雷码:

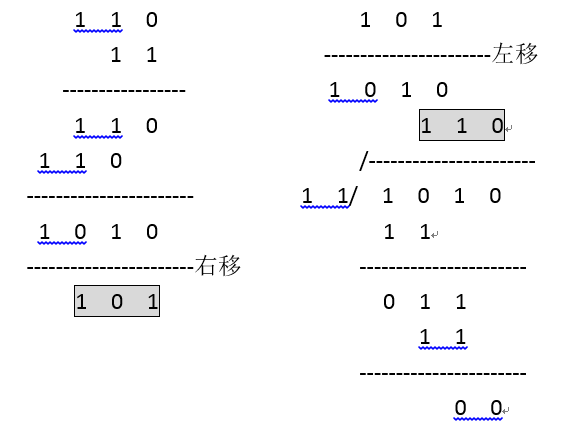

(4)异或乘除法

异或乘除法没有借位和进位

编码:异或乘3后右移1位。

解码:左移异或除3,忽略余数

3. 实现方法

程序采用递归循环查表法,FPGA多采用异或转换

(1)二进制转格雷码

FPGA代码:

//================================================================

// Filename : bin2gray.v

// Created On : 2017-05-14 16:54:30

// Last Modified : 2017-05-14 16:55:14

// Author : ChrisHuang

// Description : Converting Gray Code to Binary

//================================================================

`timescale 1ns/1ps

module bin2gray

#(parameter pDataWidth = 4

)

(

input [pDataWidth-1:0] iBinary,

output [pDataWidth-1:0] oGrayCode

);

assign oGrayCode = (iBinary >> 1) ^ iBinary;

endmodule

//================================================================

// Filename : bin2gray_tb.v

// Created On : 2017-05-14 16:54:30

// Last Modified : 2017-05-14 16:55:14

// Author : ChrisHuang

// Description : test Converting Gray Code to Binary

//================================================================

`timescale 1ns/1ps

module bin2gray_tb();

reg rClk;

reg [3:0] rBinary;

wire [3:0] wGray;

initial

begin

rClk = 0;

rBinary = 4'b0;

#500 $stop;

end

always #10 rClk = ~rClk;

always @ (posedge rClk)

begin

rBinary <= rBinary + 1'b1;

end

bin2gray #(4) i1

(

.iBinary (rBinary ),

.oGrayCode (wGray )

);

endmodule

(2)格雷码转二进制

FPGA代码:

//================================================================

// Filename : gray2bin.v

// Created On : 2017-05-14 21:22:30

// Last Modified : 2017-05-14 21:23:14

// Author : ChrisHuang

// Description : Converting Gray Code to Binary

//================================================================

`timescale 1ns/1ps

module gray2bin

#(parameter pDataWidth = 4

)

(

input [pDataWidth-1:0] iGrayCode,

output [pDataWidth-1:0] oBinary

);

reg [pDataWidth-1:0] rBinary;

always @ (iGrayCode)

begin

rBinary[3] = iGrayCode[3];

rBinary[2] = iGrayCode[2] ^ rBinary[3];

rBinary[1] = iGrayCode[1] ^ rBinary[2];

rBinary[0] = iGrayCode[0] ^ rBinary[1];

end

assign oBinary = rBinary;

endmodule

//================================================================

// Filename : gray2bin_tb.v

// Created On : 2017-05-14 21:22:30

// Last Modified : 2017-05-14 21:23:14

// Author : ChrisHuang

// Description : Converting Gray Code to Binary

//================================================================

`timescale 1ns/1ps

module gray2bin_tb();

`include "bin2gray.v"

reg rClk;

reg [3:0] rBinary;

wire [3:0] wGray;

wire [3:0] wBinary;

initial

begin

rClk = 0;

rBinary = 4'b0;

#500 $stop;

end

always #10 rClk = ~rClk;

always @ (posedge rClk)

begin

rBinary <= rBinary + 1'b1;

end

bin2gray #(4) i1

(

.iBinary (rBinary ),

.oGrayCode (wGray )

);

gray2bin #(4) i2

(

.iGrayCode (wGray ),

.oBinary (wBinary )

);

endmodule

参考:

http://www.cnblogs.com/logic3/p/5609919.html

http://blog.csdn.net/beiyeqingteng/article/details/7044471

http://baike.baidu.com/link?url=rNvrOCbvcfcU3T_zsJVAjTimZmICXlvFDZZIn-V8W5bBE4vTPlgYM50CyOIZfFZSGmwB1tskkgRAhUKvtAGR6UUp2TwrPVP9PgQ5tSiyPRvO-OjOhKVFviAGnv0azViO

1057

1057

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?