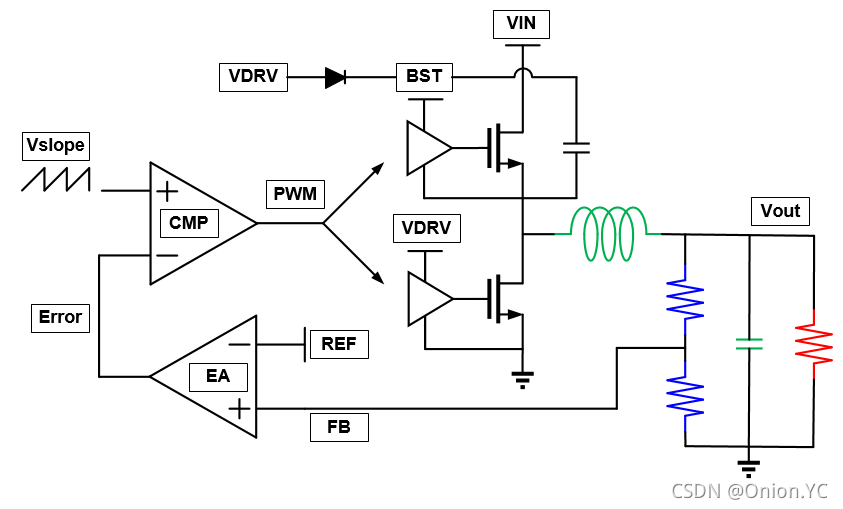

同步Buck系统可以有效地实现DC-DC降压功能,并且具有较高的效率。下图所示是一种PWM电压型同步Buck系统的原理图, 该电路的主要工作机制是利用FB对输出进行采样并与参考电压REF进行比较放大获得误差信号,误差信号再与锯齿波进行比较获得PWM信号进而控制高低侧功率管开关。

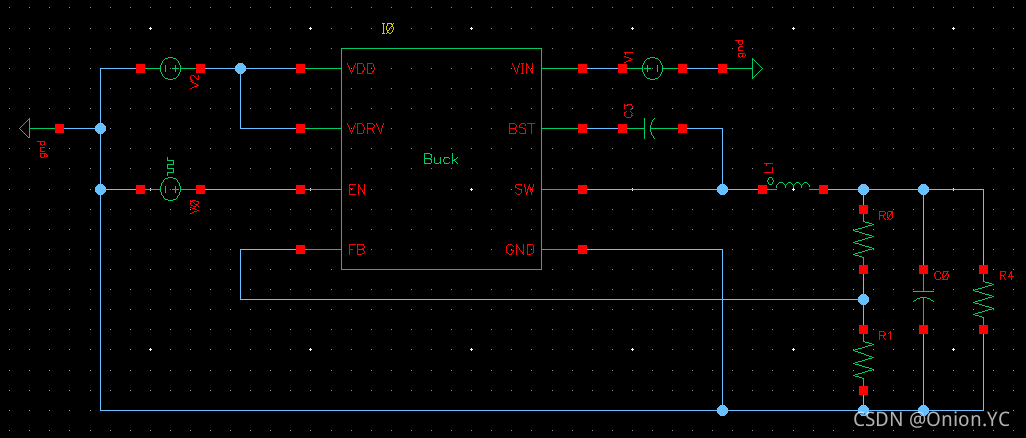

该Buck系统接口如下:VDD(逻辑部分电源);VDRV(高低侧驱动部分电源);EN(使能信号端);FB(反馈端);VIN(输入电压端);BST(自举升压端);SW(开关端);GND(接地端)。VDD和VDRV也可以设计在芯片内部由VIN经LDO获得。

下图是该Buck系统的模块组成:BGR(带隙基准);LDO(低压差线性稳压器);OSC(振荡器);EA(误差放大器);CMP(比较器);Driver_RS(RS

本文介绍了PWM电压型同步Buck系统的工作原理,该系统通过FB采样和误差放大获得PWM信号,控制功率管开关实现高效DC-DC降压。系统包括BGR、LDO、OSC等模块,仿真结果显示在6V输入、1.5V输出、50Ω负载条件下,系统能稳定工作。

本文介绍了PWM电压型同步Buck系统的工作原理,该系统通过FB采样和误差放大获得PWM信号,控制功率管开关实现高效DC-DC降压。系统包括BGR、LDO、OSC等模块,仿真结果显示在6V输入、1.5V输出、50Ω负载条件下,系统能稳定工作。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6109

6109

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?