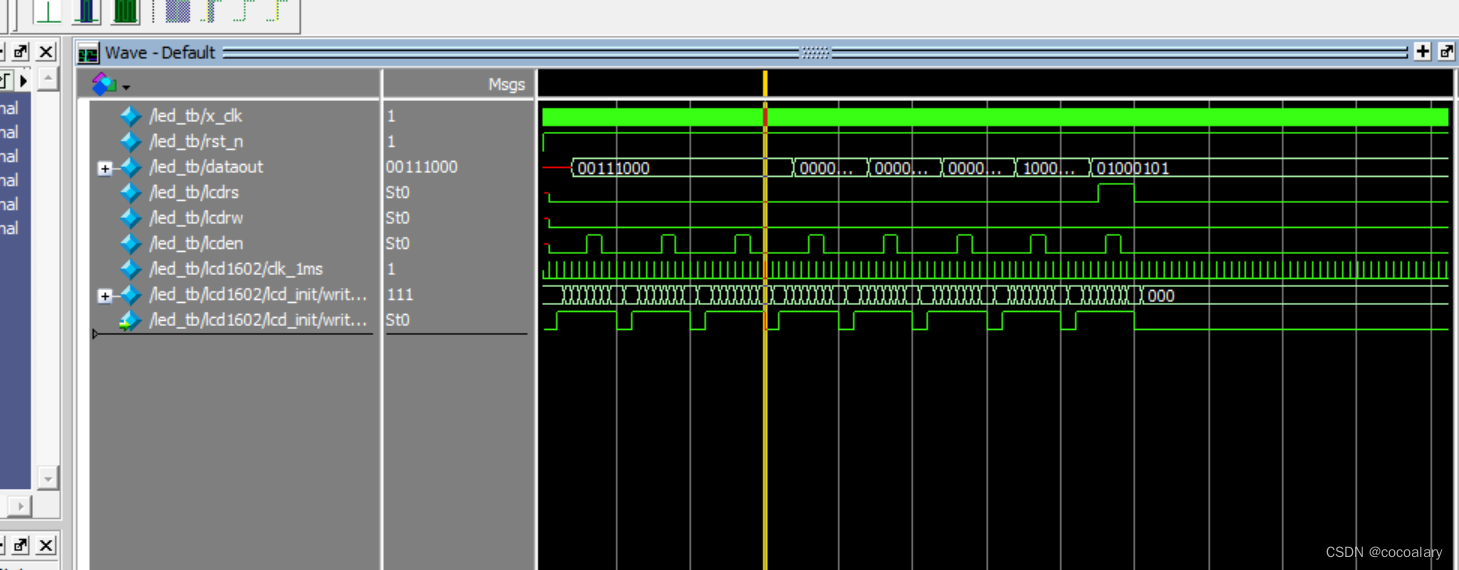

终于实现了FPGA点亮LCD了。

module lcd_init(

input start_init,

input clk_1ms,

input rst_n,

output reg lcd_rs,

output reg lcd_rw,

output reg lcd_en,

// input [7:0] datain,

output [7:0] dataout

//output reg init_flag

);

wire lcdrs;

wire lcdrw;

wire lcden;

reg [7:0] datain;

reg [7:0] dy_cnt;

reg cmd_start;

reg cmd_sel;

always @(posedge clk_1ms or negedge rst_n)

begin

lcd_rs=lcdrs;

lcd_rw=lcdrw;

lcd_en=lcden;

end

always @(posedge clk_1ms or negedge rst_n)

begin

if (!start_init)

dy_cnt =8'd0;

else

if(rst_n==1'b0)

begin

dy_cnt <=8'd0;

end

else

if(dy_cnt>=8'd170)

begin

dy_cnt <=dy_cnt;

end

else

dy_cnt <=dy_cnt+8'd1;

end

writecommand writecommand(

.cmd_start(cmd_start),

.cmd_sel(cmd_sel),

.clk_1ms(clk_1ms),

.rst_n(rst_n),

.lcdrs(lcdrs),

.lcdrw(lcdrw),

.lcden(lcden),

.datain(datain),

.dataout(dataout)

);

always @(posedge clk_1ms or negedge rst_n)

begin

if(rst_n==1'b0)

begin

cmd_start =0;

cmd_sel=0;

end

else

case(dy_cnt)

8'd00:

begin

cmd_start =0;

cmd_sel=0;

end

8'd01:

begin

datain<=8'h38;

cmd_start=1;

end

8'd02,8'd03,8'd04,8'd05,8'd06,8'd07,8'd08:;

8'd09,8'd10:

cmd_start=0;

8'd11:

begin

datain<=8'h38;

cmd_start=1;

end

8'd12,8'd13,8'd14,8'd15,8'd16,8'd17,8'd18:;

8'd19,8'd20:

cmd_start=0;

8'd21:

begin

datain<=8'h38;

cmd_start=1;

end

8'd22,8'd23,8'd24,8'd25,8'd26,8'd27,8'd28:;

8'd29,8'd30:

cmd_start=0;

8'd31:

begin

datain<=8'h0c;

cmd_start=1;

end

8'd32,8'd33,8'd34,8'd35,8'd36,8'd37,8'd38:;

8'd39,8'd40:

cmd_start=0;

8'd41:

begin

datain<=8'h06;

cmd_start=1;

end

8'd42,8'd43,8'd44,8'd45,8'd46,8'd47,8'd48:;

8'd49,8'd50:

cmd_start=0;

8'd51:

begin

datain<=8'h01;

cmd_start=1;

end

8'd52,8'd53,8'd54,8'd55,8'd56,8'd57,8'd58:;

8'd59,8'd60:

cmd_start=0;

8'd61:

begin

datain<=8'h84;

cmd_start=1;

end

8'd62,8'd63,8'd64,8'd65,8'd66,8'd67,8'd68:;

8'd69,8'd70:

cmd_start=0;

8'd71:

begin

datain<=8'h46;

cmd_sel=1;

cmd_start=1;

end

8'd72,8'd73,8'd74,8'd75,8'd76,8'd77,8'd78:;

8'd79,8'd80:

begin

cmd_start=0;

cmd_sel=0;

end

8'd81:

begin

datain<=8'h50;

cmd_sel=1;

cmd_start=1;

end

8'd82,8'd83,8'd84,8'd85,8'd86,8'd87,8'd88:;

8'd89,8'd90:

begin

cmd_start=0;

cmd_sel=0;

end

8'd91:

begin

datain<=8'h47;

cmd_sel=1;

cmd_start=1;

end

8'd92,8'd93,8'd94,8'd95,8'd96,8'd97,8'd98:;

8'd99,8'd100:

begin

cmd_start=0;

cmd_sel=0;

end

8'd101:

begin

datain<=8'h41;

cmd_sel=1;

cmd_start=1;

end

8'd102,8'd103,8'd104,8'd105,8'd106,8'd107,8'd108:;

8'd109,8'd110:

begin

cmd_start=0;

cmd_sel=0;

end

8'd111:

begin

datain<=8'h20;

cmd_sel=1;

cmd_start=1;

end

8'd112,8'd113,8'd114,8'd115,8'd116,8'd117,8'd118:;

8'd119,8'd120:

begin

cmd_start=0;

cmd_sel=0;

end

8'd121:

begin

datain<=8'hc5;

cmd_start=1;

end

8'd122,8'd123,8'd124,8'd125,8'd126,8'd127,8'd128:;

8'd129,8'd130:

cmd_start=0;

8'd131:

begin

datain<=8'h6f;

cmd_sel=1;

cmd_start=1;

end

8'd132,8'd133,8'd134,8'd135,8'd136,8'd137,8'd138:;

8'd139,8'd140:

begin

cmd_start=0;

cmd_sel=0;

end

8'd141:

begin

datain<=8'h6b;

cmd_sel=1;

cmd_start=1;

end

8'd142,8'd143,8'd144,8'd145,8'd146,8'd147,8'd148:;

8'd149,8'd150:

begin

cmd_start=0;

cmd_sel=0;

end

default:;

endcase

end

endmodule

module lcd1602(

input x_clk,

output lcdclk,

input rst_n,

output lcdrs,

output lcdrw,

output lcden,

output [7:0] dataout

);

wire sys_clk;

assign sys_clk =x_clk;

assign lcdclk =x_clk;

//defparam OSCH_inst.NOM_FREQ = "38.00";

//OSCH OSCH_inst(

//.STDBY(1'b0), // 0=Enabled, 1=Disabled // also Disabled with Bandgap=OFF

//.OSC(sys_clk),

//.SEDSTDBY()

//); // this signal is not required if not // using SED

reg power_on_rst ;

reg [16:0] clk_1ms_count;

reg clk_1ms;

reg cmdflagout=0;

reg dataflagout=0;

reg init_flag=0;

parameter CLK_1MS_PERIOD = 17'd49999;

reg [5:0] internal_por_cnt;

initial internal_por_cnt = 6'b0; //For Simulation

always @(posedge sys_clk)begin

if(internal_por_cnt<6'd60)

internal_por_cnt <= internal_por_cnt + 1'b1;

else

internal_por_cnt <= internal_por_cnt;

end

always @(posedge sys_clk )begin

if(internal_por_cnt>6'd50)

power_on_rst <= 1'b1;

else

power_on_rst <= 1'b0;

end

always @(posedge sys_clk or negedge power_on_rst) begin

if(power_on_rst == 1'b0)begin

clk_1ms_count <= 17'b0;

clk_1ms <= 1'b0;

end

else begin

if(clk_1ms_count == CLK_1MS_PERIOD)begin

clk_1ms_count <= 17'b0;

clk_1ms <= 1'b1;

end

else begin

clk_1ms_count <= clk_1ms_count + 17'b1;

clk_1ms <= 1'b0;

end

end

end

lcd_init lcd_init(

.start_init(1),

.clk_1ms(clk_1ms),

.rst_n(rst_n),

.lcd_rs(lcdrs),

.lcd_rw(lcdrw),

.lcd_en(lcden),

.dataout(dataout)

);

endmodule

本文详细描述了一个使用FPGA控制LCD显示屏的过程,包括初始化步骤、时钟管理、寄存器操作以及发送特定命令序列。

本文详细描述了一个使用FPGA控制LCD显示屏的过程,包括初始化步骤、时钟管理、寄存器操作以及发送特定命令序列。

2630

2630