1、总线

系统结构

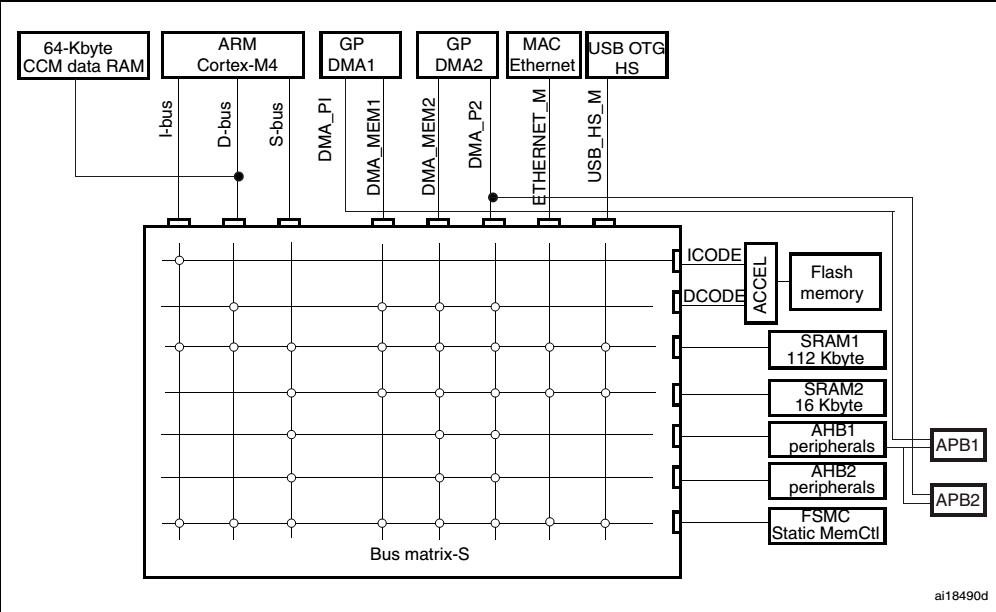

系统包括一个由多个互相连接的32位AHB总线组成的矩阵

- 8个主总线

1. – Cortex-M4 with FPU core I-bus, D-bus and S-bus

2. – DMA1 memory bus

3. – DMA2 memory bus

4. – DMA2 peripheral bus

5. – Ethernet DMA bus

6. – USB OTG HS DMA bus- 7个从总线:

1. – Internal Flash memory ICode bus

2. – Internal Flash memory DCode bus

3. – Main internal SRAM1 (112 KB)

4. – Auxiliary internal SRAM2 (16 KB)

5. – AHB1 peripherals including AHB to APB bridges and APB peripherals

6. – AHB2 peripherals

7. – FSMC总线矩阵也能够提供主到从的访问,从而使能并发访问,甚至在多个高速外设同时工作的时候也能够高效工作. 64Kbyte的CCM(core coupled memory)数据RAM不是总线矩阵的一部分,只能通过CPU来访问.

总线类型

-

I-bus

该总线连接带有FPU的Cortex-M4内核的指令总线到BusMatrix. 该总线被内核用于取指令操作. 该总线的控制目标是一块包括代码的内存 (internal Flash memory/SRAM or external memories through the FSMC/FMC).

-

D-bus

该总线连接带有FPU的Cortex-M4内核的数据总线到64Kbyte的CCM数据RAM再到BusMatrix. 该总线被内核用于下载代码与调试. 该总线的控制目标是一块包括代码或者数据的内存 (internal Flash memory or external memories through the FSMC/FMC).

-

S-bus

该总线连接带有FPU的Cortex-M4内核的系统总线到BusMatrix. 该总线被用来访问加载到SRAM或者外设的数据. 指令也可能通过该总线取得 (没有ICode来的高效). 该总线的控制目标有:内部的SRAM1, SRAM2 and SRAM3, AHB1的外设(包括APB外设), AHB2的外设和通过FSMC/FMC的外部内存

-

BusMatrix

BusMatrix 管理主总线之间的访问仲裁. 仲裁使用循环算法

总线结构图:

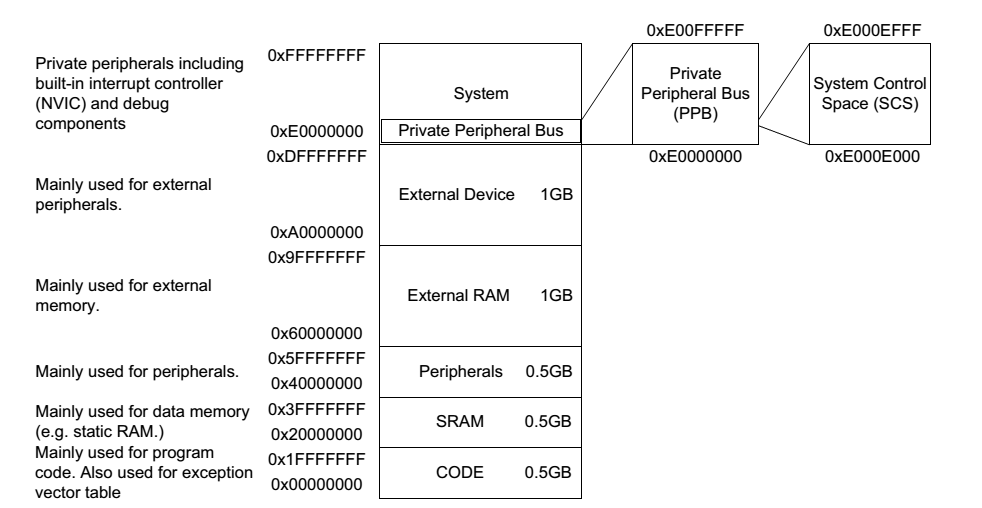

2、内存分布

- 编程空间(代码空间), 数据空间, 寄存器和I/O端口被组织在同一个线性的4Gb空间中。所有的数据都按照小端存储

- 可寻址内存空间被分为8个块, 每块包括512MB

- 所有没有被分配到片上内存或者片上外设的空间都被成为”reserved”

嵌入式SRAM

- STM32F407ZG配置了4 Kbytes的备份 SRAM,192 Kbytes的系统SRAM。

- 嵌入式SRAM可以以字节,半字,字的方式访问,可以以CPU的速度进行无需等待的访问,嵌入式SRAM被分为以下3个块:

- SRAM1 和 SRAM2 映射到 0x2000 0000 地址并且可以被所有的 AHB 总线访问.

- SRAM3 (只有 STM32F42xxx 与 STM32F43xxx 系列可用) 映射到 0x2002 0000 地址处并且可以被所有的 AHB 总线访问

- CCM (core coupled memory) 映射到 0x1000 0000 地址处只能够通过D-bus被CPU访问

位带操作

在STM32中提供了两个位带操作域以及对应的位带别名域

| 位带操作域 | 位带别名域 |

|---|---|

| SRAM的低1M字节 : 0x2000 0000~0x200F FFFF | 0x2200 0000~0x23FF FFFC |

| 外设的低1M字节 : 0x4000 0000~0x400F FFFF | 0x4200 0000~0x43FF FFFC |

位带操作公式:

bit_word_addr = bit_band_base + (byte_offset x 32) + (bit_number × 4)- 1

例子:

0x22006008 = 0x22000000 + (0x300*32) + (2*4)

/* 对0x22006008的读写就实现了对0x2000 0300处第2个bit的读写 */

/* 同理,若要对0x40000000地址块进行位操作,需要把上面式子右边的0x22000000换成0x42000000 */- 1

- 2

- 3

以后我们想直接操作某个寄存器的某一位的时候,只需要找到这一位对应的别名地址,然后对别名地址进行读写即可实现对这一位的读写。如果想实现这中操作的话,只需要定义宏即可,例如下面的:

#define REGISTER_BIT_BAND(ofs, bit_num) (0x22000000 + (ofs << 5) + (bit_num << 2))

#define WRITE_R_BIT_BAND(ofs, bit_num, stat) (*((volatile unsigned int *)REGISTER_BIT_BAND(ofs, bit_num)) = stat)

//上面两个宏可以实现对寄存器位带域的操作- 1

- 2

- 3

内核编程手册给出的M系列4GB内存分布

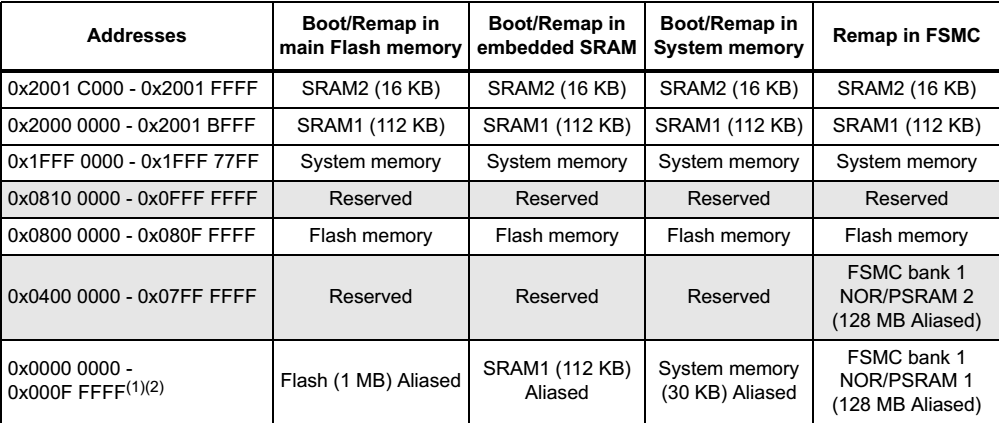

3、启动配置

启动方式

| Boot mode selection pins | Boot mode | Aliasing | |

|---|---|---|---|

| BOOT1 | BOOT0 | ||

| x | 0 | Main Flash memory | Main Flash memory is selected as the boot space |

| 0 | 1 | System memory | System memory is selected as the boot space |

| 1 | 1 | Embedded SRAM | Embedded SRAM is selected as the boot space |

我的板子启动是在main flash memory,由前面的ARM编译工具一节可以知道代码从0x08000000开始运行,这个也是由分散加载文件指定的,也是板子上面main flash实际地址

物理地址重映射

- 下面的内存空间可以被重映射:

- Main Flash memory

- System memory

- Embedded SRAM1 (112 KB)

- FSMC bank 1 (NOR/PSRAM 1 and 2)- 1

- 2

- 3

- 4

映射表为

映射到0x00000000地址处的内存块可以由SYSCFG控制器的(SYSCFG_MEMRMP)寄存器低二位决定,如下表所示

| bit1 | bit0 | memory selected |

|---|---|---|

| 0 | 0 | Main Flash memory mapped at 0x0000 0000 |

| 0 | 1 | System Flash memory mapped at 0x0000 0000 |

| 1 | 0 | FSMC Bank1 (NOR/PSRAM 1 and 2) mapped at 0x0000 0000 |

| 1 | 1 | Embedded SRAM (SRAM1) mapped at 0x0000 0000从表中 |

可以看出来从main flash启动的时候flash memory会被重新映射到0地址开始处,大小为1MB,但是我的板子依然是从0x08000000地址处运行代码的,现在由表中数据可以看出来从0地址开始运行也是可以的,可能是为了适应不同的启动方式,所以才从0x08000000地址处开始运行系统代码的。如果要从其他的地方运行flash memory中的代码,只需要在那种方式对应的被重映射到0地址空间代码段开头加上一个跳转语句,直接跳转到0x08000000地址处就可以运行代码了

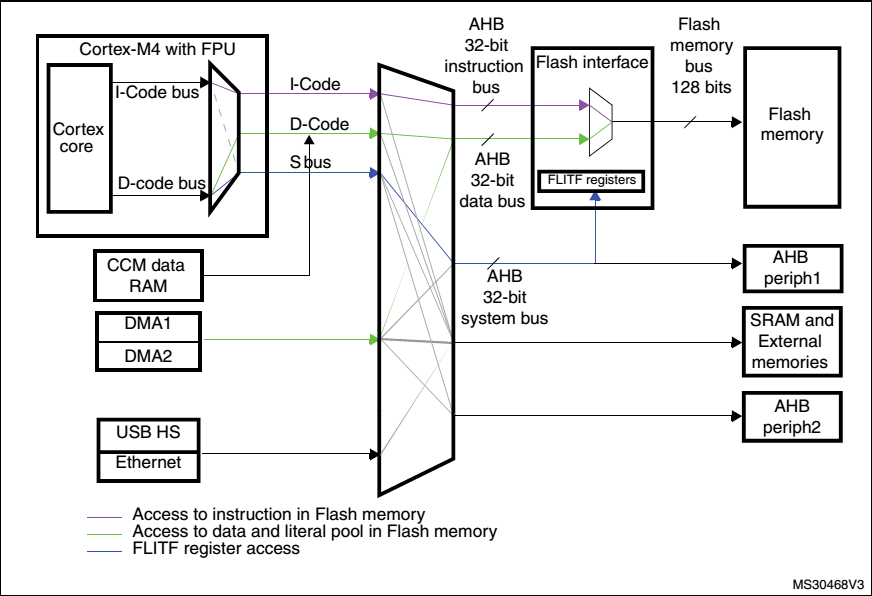

4、嵌入式flash memory

接口特性:

- Flash memory 读操作

- Flash memory 编程/擦除操作

- 读/写保护

- 指令预取

- I-Code上面有 64 个 128 位宽的快速存取线

- I-Code上面有 8 个 128 位宽的快速存取线

flash memory特性:

- 1M byte容量

- 128位的读数据位宽

- 支持 Byte, half-word, word and double word 写入

- 支持扇区与块擦除

- 支持内存组织

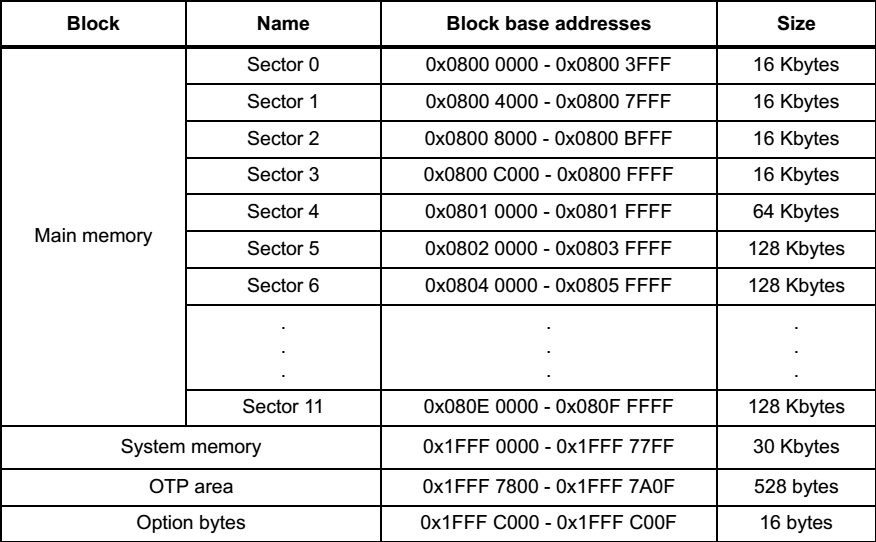

- flash memory可以被组织成下面的样子:

- – main memory 分为 4 个 16 Kbytes 大小扇区, 1 个 64 Kbytes 大小扇区,和 7 个 128 Kbytes 大小扇区

- – 不同启动设备对应相应的system memory

- – 512 OTP (一次性编程) bytes

- – 可选配置读写保护

- flash memory可以被组织成下面的样子:

- 低电量模式

内存分布图

额外补充时钟一节内容:

VOS 在 PWR_CR 寄存器的 bit15 位被设置

当 VOS = ‘0’, fHCLK 最大为 144 MHz.

当 VOS = ‘1’, fHCLK 最大为 168 MHz.

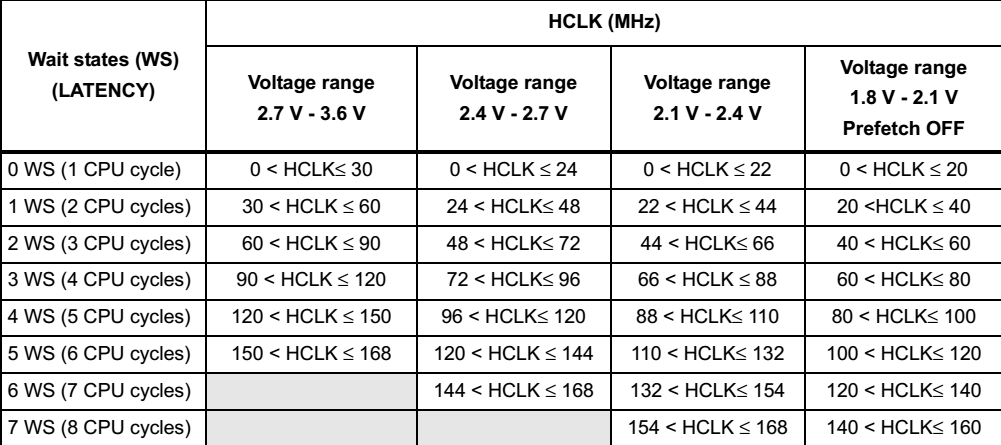

等待周期

等待周期指的是CPU访问Flash的等待时间,CPU访问Flash的周期就是等待周期加上1,这个与Flash的硬件性能有关

四个驱动单元:context-M3内核的D-bus总线和S-bus总线、通用DMA1和通用DMA2。

四个被驱动的单元:内部FLASH(内部山村存储器)、内部SRAM、FSMC、AHB到APB的桥AHP2APBx。

ICode总线是context-M3与内部闪存FLASH指令接口之间的连接的总线,实现指令的预取功能。

DCode总线是将context-M3与内部闪存存储器(FLASH)的数据接口连接起来的总线,实现数据读取。

系统总线(system bus)连接context-M3和总线矩阵,总线矩阵协调着context-M3和DMA间的访问。

DMA总线实现DMA的AHB主控接口道总线接口的连接。

总线矩阵

此总线矩阵协调内核系统总线和DMA主控总线之间的访问仲裁。此仲裁利用轮换算法。此总线矩阵由四个驱动部件(CPU的DCode、系统总线、DMA1总线和DMA2总线)和四个被动部件(闪存存储器接口(FLITF)、SRAM、FSMC和AHB2APB桥)构成。

AHB外设通过总线矩阵与系统总线相连,允许DMA访问。

APB1操作速度限于36MHz,APB2操作于全速(最高72MHz)。

存储器组织

程序存储器、数据存储器、寄存器和输入输出端口被组织在同一个4GB的线性地址空间内。

数据字节以小端格式存放在存储器中。一个字里的最低地址字节被认为是该字的最低有效字

FLASH/代码区512M、片上SRAM512M、片上外设/寄存器区512M。4G内其它的地址空间是保留的地址空间。

3868

3868

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?