在FPGA中,数据进行跨时钟域传输时,会出现亚稳态的问题。跨时钟域也就是跨越了两个频率和相位不同的异步时钟域。为了解决亚稳态和由时钟不同步引起的其他问题,选用了FIFO。

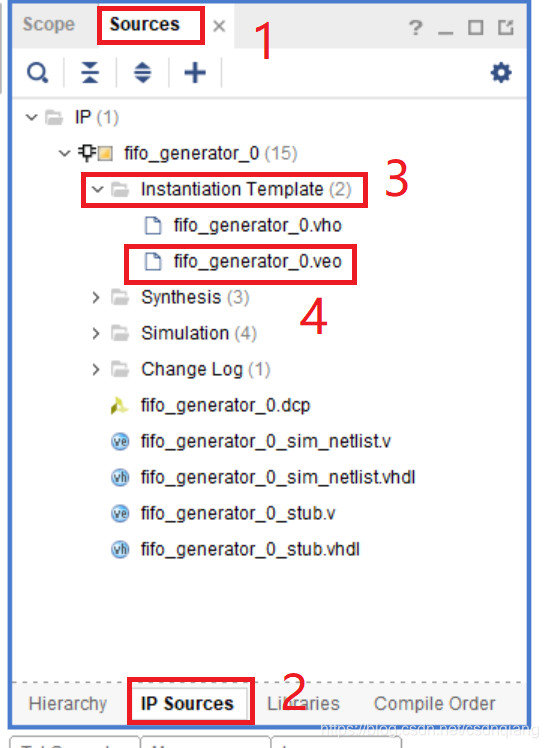

本例中,选用了输入和输出为同一时钟来生成FIFO。生成FIFO后可在.veo文件中找到例化模版,如下图所示:

操作流程为:

Sources(1)→IP Sources(2)→Instantiation template(3)→.veo文件(4)。

然后新建测试文件并命名为top.v,在文件中进行实例化,实例化代码如下:

fifo_generator_0 your_instance_name (

.clk(!clk), // input wire clk

.srst(!rst), // input wire srst

.din(din), // input wire [7 :0] din

.wr_en(wr_en), // input wire wr_en

.rd_en(rd_en), // input wire rd_en

.dout(dout), // output wire [7: 0] dout

.full(), // output wire full

.empty() //

在FPGA中,数据进行跨时钟域传输时,会出现亚稳态的问题。跨时钟域也就是跨越了两个频滤和相位不同的异步时钟域。为了解决亚稳态和由时钟不同步引起的其他问器,选用了FIFO。本例中,选用了输入和输出为同一时钟来生成FIFO。生成FIFO后可在.veo文件中找到例化模版,如下图所示:操作流程为:Sources(1)→IP Sources(2)→Instantiation template(3)→.veo文件(4)。然后新建测试文件并命名为top.v,在文件中进行实例化,实例化代码如下:fifo_gen

在FPGA中,数据进行跨时钟域传输时,会出现亚稳态的问题。跨时钟域也就是跨越了两个频滤和相位不同的异步时钟域。为了解决亚稳态和由时钟不同步引起的其他问器,选用了FIFO。本例中,选用了输入和输出为同一时钟来生成FIFO。生成FIFO后可在.veo文件中找到例化模版,如下图所示:操作流程为:Sources(1)→IP Sources(2)→Instantiation template(3)→.veo文件(4)。然后新建测试文件并命名为top.v,在文件中进行实例化,实例化代码如下:fifo_gen

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

411

411

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?