一、 7系FPGA基本结构

介绍Xilinx FPGA 7 系列的时钟结构、资源、用法

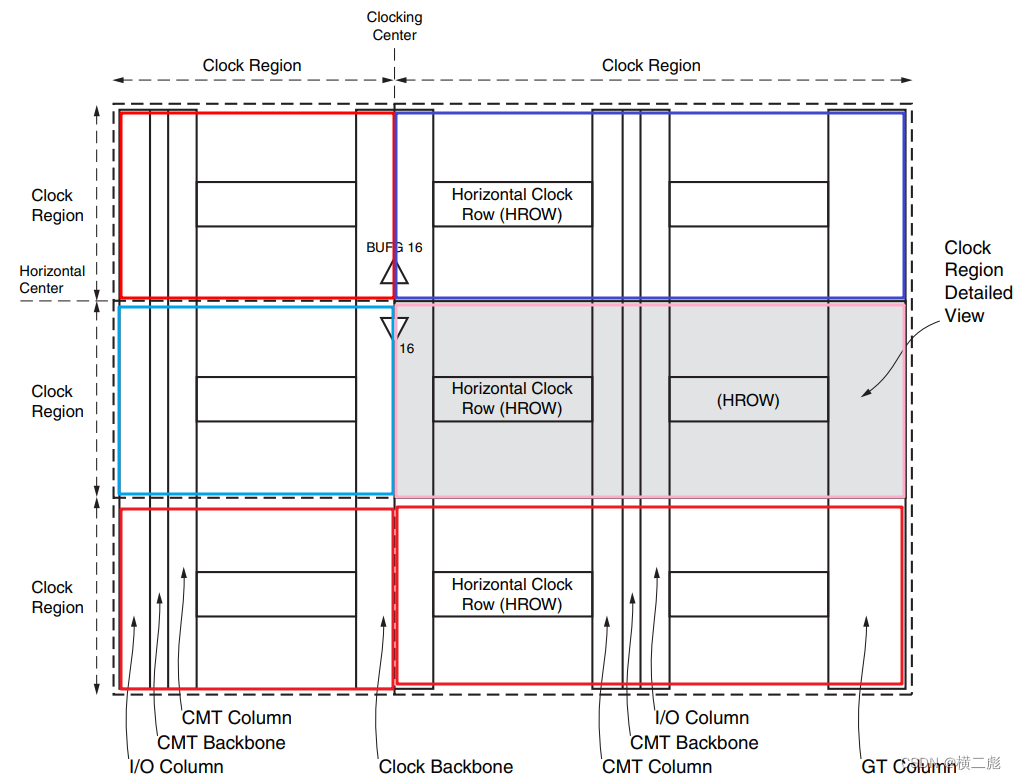

首先来看7系列FPGA的时钟结构图:

Clock Region:时钟区域,下图中有6个时钟区域,用不同的颜色加以区分出来

Clock Backbone:从名字也能看出来,这个一个纵向贯穿整个FPGA的时钟资源,把FPGA的clock region分成了两个部分,所有的全局时钟时钟都要从这经过。可以看到BUFG都在Clock Backbone上。Clocking Center就是Backbone中间的分割线。

Horizontal Center:水平分割线,将FPGA的BUFG分割成上下相等的两部分,像下图中,上下各有16个BUFG。需要注意的是,BUFG不属于任何的clock region,并且BUFG可以到底FPGA的任一个时钟角落。

HROW:Horizontal Clock Row, 将每一个clock region分成上下两部分,全局时钟进入每个clock region时,需要要经过HROW,有点类似于Clock Backbone在FPGA中的作用。

CMT Backbone:Clock Backbone是整个FPGA的Backbone,是很珍贵的资源,而如果是上下相邻的clock region,可以通过CMT Backbone互连。

CMT Column:每个Cloumn包含一个MMCM和一个PLL。

GT Column:高速收发器的column。

分多个clock region原因

为了适用更多的时钟,加入没有clock region,那就全部是global clock,如果有16个时钟网络,那最多就支持16个时钟。而分成了clock region后,如果该区域的时钟资源恰好可以布局到对应的region,则只使用该region的时钟网络资源。也就是说,如果有16个时钟网络资源,那么极限情况下,两个region就可以使用32个时钟。

二、7系列clock region详解

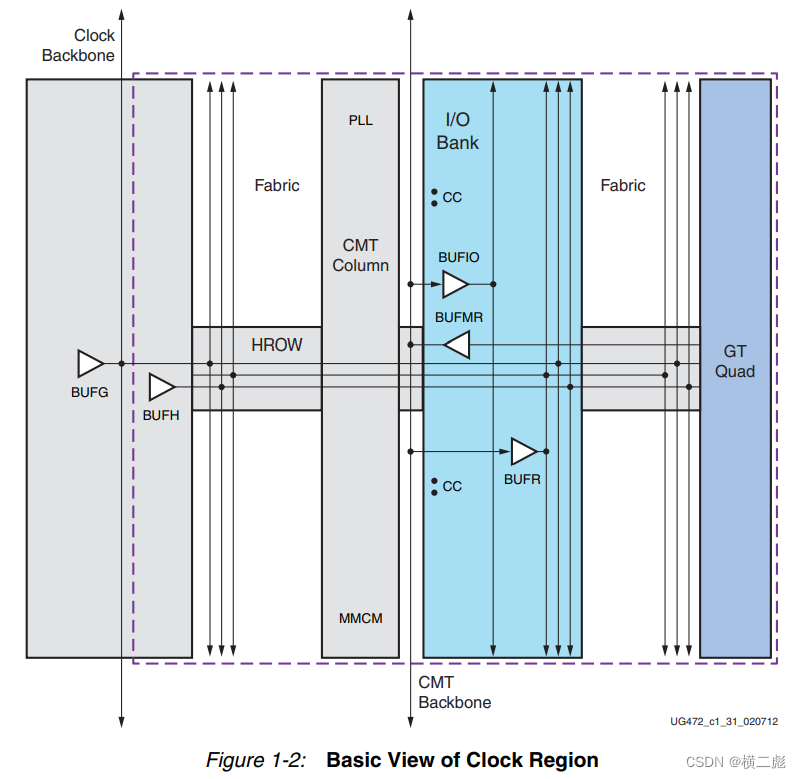

7系列FPGA的clock region的结构图

7系列FPGA的clock region的结构图

首先我们来明确几个Buffer的含义

BUFG:global clock buffer

BUFH:horizontal clock buffer,可驱动左右相邻的两个region

BUFR:regional clock buffer,从名字就可以看出来,只能驱动当前region

BUFIO:I/O buffer,位于IO Bank中,只能用于驱动IO

BUFMR:multi-clock region buffer,它可以驱动本BANK和上下相邻BANK的BUFIO和BUFR,起到了扩展连接的作用

CC:clock capable

下图是clock region更详细的内部结构图,

可以看到:

每个IO Bank的4个cc管脚可以驱动CMT中的PLL/MMCM,也可以驱动BUFH;

HROW中有12个routing track,BUFG和BUFH共享12个track;

GT Quad有10个专门的track用于驱动CMT和clock backbone中的BUFFER;

BUFR有4个track驱动逻辑资源、CMT和BUFG;

CMT在一定条件下可以通过CMT backbone驱动上下相邻的CMT;

一个region中的时钟资源可以驱动本region或者水平临近region的时钟BUFFER;

CMT、cc管脚和GT时钟可以通过BUFH来驱动左右相邻region

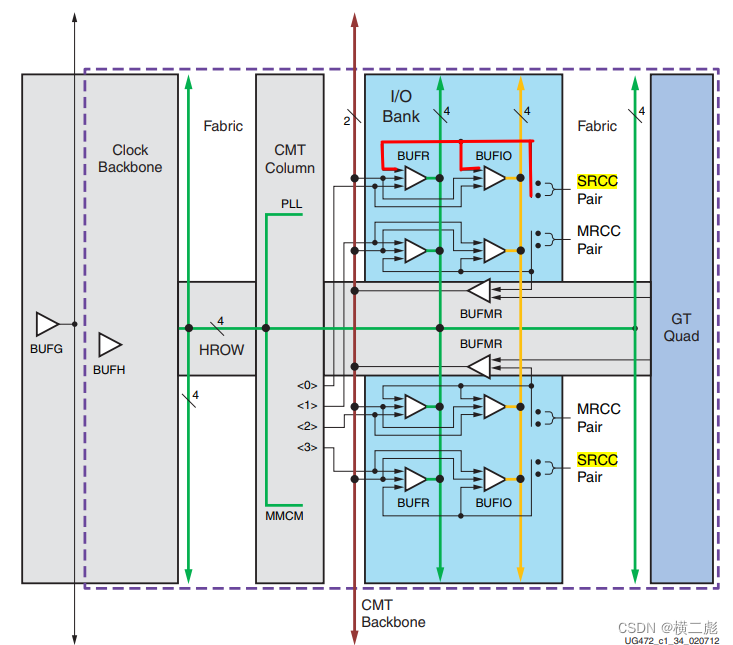

下图是BUFR/BUFMR/BUFIO的详细结构图,

可以看出:

每个IO Bank都含有4个BUFIO和BUFR;

clock buffer都可以被cc管脚或者MMCM来驱动;

图中可以看到CC又分了MRCC和SRCC,它们的区别我们放到下一篇文章中专门来讲;

从MMCM输出到BUFR和BUFIO之间有一条专门的高性能差分路径;

三 、MRCC和SRCC的区别

只有7系列的FPGA中才有MRCC和SRCC的说法,到了UltraScale系列,都是叫GC。

MRCC就是Multi Region的CC,从该管脚输入的时钟可以access到不同的clock region,而SRCC就是Single Region的CC,从该管脚输入的时钟只能access当前clock region。

MRCC通过BUFMR来access最多三个clock region,从下面的图也可以看出,已经用红色的线将MRCC的路径都标出来,可以看到,MRCC通过了BUFMR到达了CMT Backbone,然后就可以access其他的clock region了。

从上面这个图可以看出,MRCC可以直接驱动BUFR和BUFIO,也可以先经过BUFMR后再驱动BUFIO和BUFR。

SRCC的路径在下面的图中用红色的线标识出来,可看到,它的路径只在当前的clock region里面。

下面这个表格解释的就更加清晰了,MRCC和SRCC都是由外部的时钟驱动,而且MRCC和SRCC的区别就在于MRCC可以驱动BUFMR,SRCC不行。其他基本都一样,它们都可以驱动四个BUFIO、四个BUFR、一个CMT、上下相邻的CMT、16个BUFG和BUFH。

其中有一点很关键,就是它们都可以驱动BUFG和BUFH,这就意味着,从MRCC和SRCC进来的时钟都可以access全局时钟树,也就都可以当做全局时钟。

所以,SRCC进来的时钟,虽然不能直接驱动其他clock region,但接到BUFG上之后,仍然可以通过BUFG来驱动其他的clock region。

MRCCs that are located in the same clock region and on the same left/right side of the device drive:

the same left/right side:因为FPGA里面有个纵向的Clock Backbone,以这个为间隔分成了左右两部分,所有的全局时钟都在这个Clock Backbone里面。

MRCCs within the same half top/bottom drive:

• 16 BUFGs

the same half top/bottom drive:FPGA里面有个Horizontal Center,将FPGA的BUFG分割成上下相等的两部分,上下各有16个BUFG。

1973

1973

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?