September 13, 2016

作者:dengshuai_super

出处:http://blog.csdn.net/dengshuai_super/article/details/52535925

声明:转载请注明作者及出处。

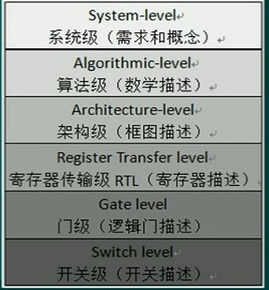

建模方式:抽象层次

HDL语言用于建模时,可以根据抽象的层次进行分类:

可以用高级别的的愈发描述需求和概念(系统级)

可以将需求概念用数学形式描述(算法级)

可以用通用寄存器的传输操作来描述(RTL)(我们用语言来描述的代码都可以归结为寄存器的传输操作)

可以将通用寄存器描述的模型转变为逻辑门描述的模型(Gate-level)

可以将逻辑门描述的模型转变为用电路开关描述的模型(Switch-level)

建模方式:三种建模方式

HDL建模时,除了可以用不同层次的抽象进行分类,还可以根据其对信号的描述方式的不同划分为以下三种:

1、数据流建模

2、行为建模

3、结构化建模

在模块中对信号资源分配(或组合逻辑的连接)的描述,成为数据流描述(Data-flow Description),或称为数据流建模(Data-flow Modeling)

在模块中对信号的行为进行的描述,称为行为描述(Behavioral Description),或称为行为建模(Behavioral Modeling)

将诸多模块组织成一个更大的模块,其描述称为结构化描述(Structural Description),或称为结构化建模(Structural Modeling)

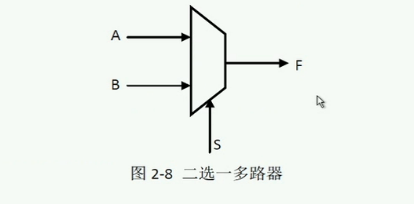

例:二选一多路器

1、数据流建模

//二选一多路器的Verilog数据流建模

module two_to_one_dataflow(a,b,s,f);

input a;

input b;

input s;

output f;

assign f = (a&~s)|(b&s);//等号在这里是一个阻塞赋值

endmodule`timescale 1ns / 1ns

module two_to_one_dataflow_tb;

reg a,b,s;

wi

本文介绍了Verilog HDL在FPGA设计中的建模方法,包括抽象层次和三种具体建模方式:数据流建模、行为建模和结构化建模。数据流建模关注信号资源分配,行为建模关注信号行为,结构化建模则涉及模块的组织结构。通过实例展示了这三种建模方式的应用。

本文介绍了Verilog HDL在FPGA设计中的建模方法,包括抽象层次和三种具体建模方式:数据流建模、行为建模和结构化建模。数据流建模关注信号资源分配,行为建模关注信号行为,结构化建模则涉及模块的组织结构。通过实例展示了这三种建模方式的应用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1596

1596

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?