名称:Quartus音乐播放器verilog代码青创QC-FPGA开发板(文末获取)

软件:Quartus

语言:Verilog

代码功能:

音乐播放器设计

1、可以通过蜂鸣器播放歌曲,循环播放

2、可以通过按键控制开始、暂停、复位

3、led灯显示节奏

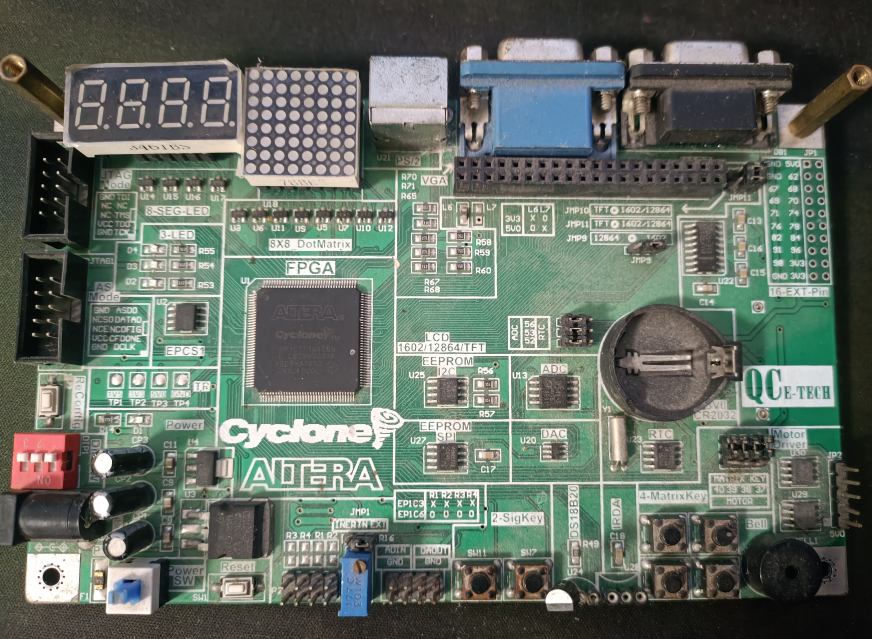

本代码已在青创QC-FPGA开发板验证,青创QC-FPGA开发板如下,其他开发板可以修改管脚适配:

1. 工程文件

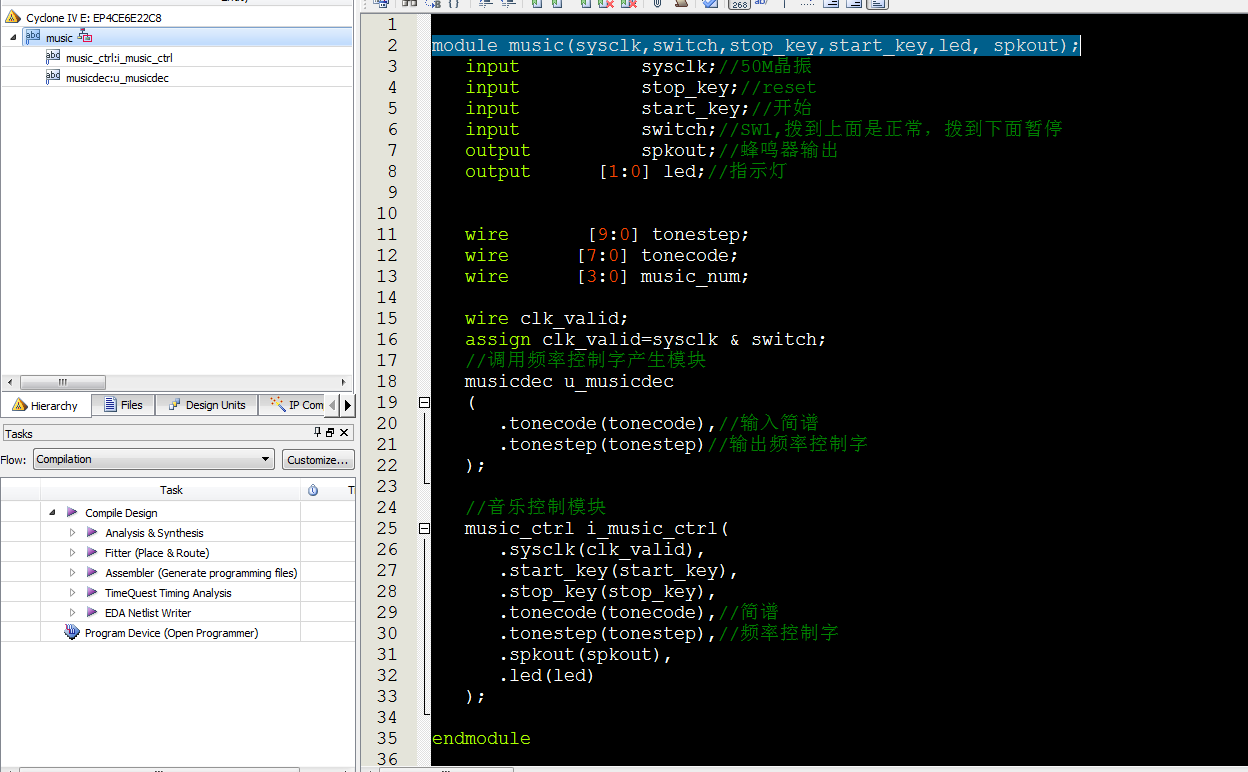

2. 程序文件

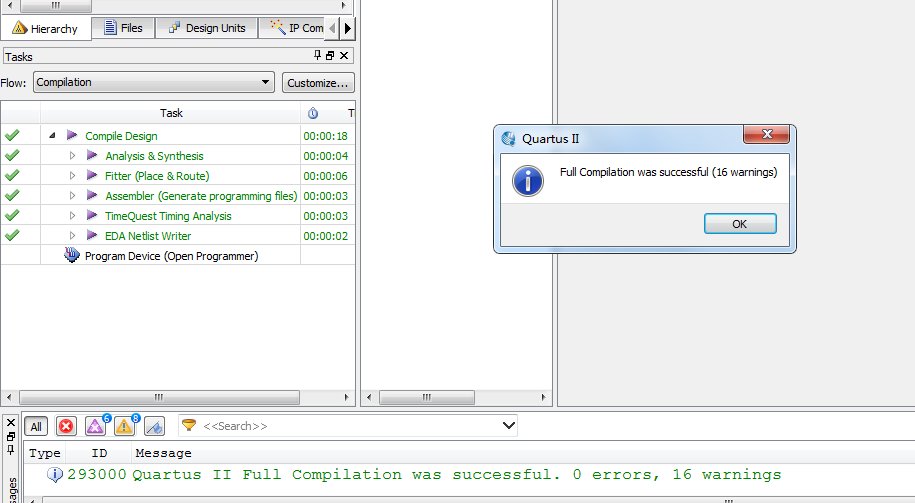

3. 程序编译

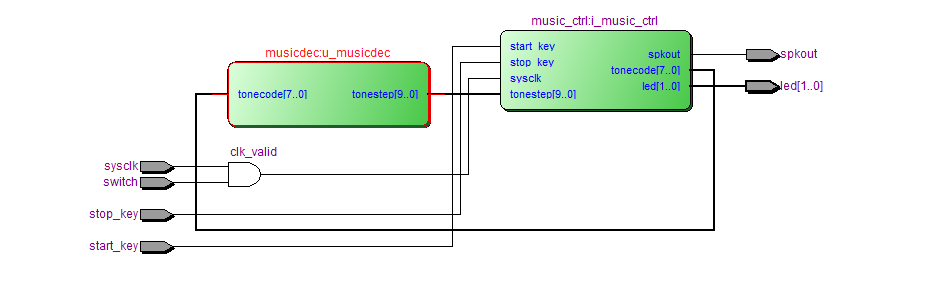

4. RTL图

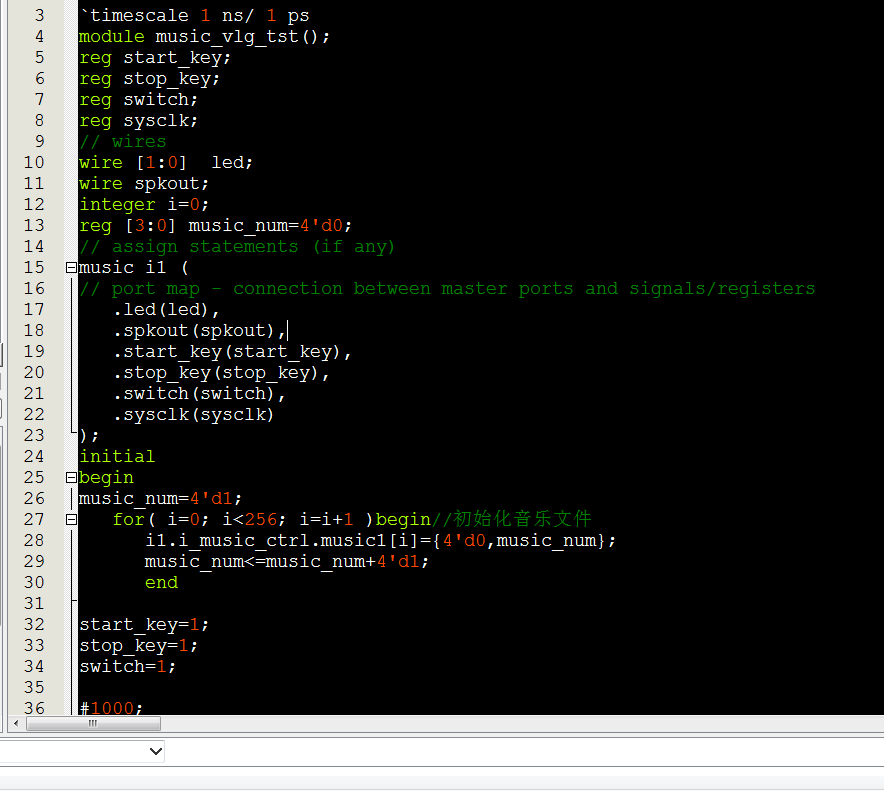

5. Testbench

6. Modelsim仿真

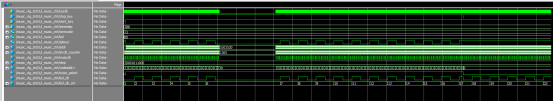

仿真了启动、暂停、停止等情况下的波形

6.1 整体仿真

6.2 音乐控制模块

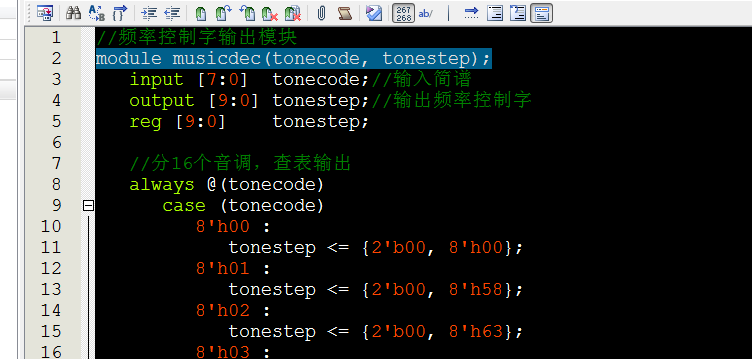

6.3 频率控制字模块

部分代码展示:

module music(sysclk,switch,stop_key,start_key,led, spkout); input sysclk;//50M晶振 input stop_key;//reset input start_key;//开始 input switch;//SW1,拨到上面是正常,拨到下面暂停 output spkout;//蜂鸣器输出 output [1:0] led;//指示灯 wire [9:0] tonestep; wire [7:0] tonecode; wire [3:0] music_num; wire clk_valid; assign clk_valid=sysclk & switch; //调用频率控制字产生模块 musicdec u_musicdec ( .tonecode(tonecode),//输入简谱 .tonestep(tonestep)//输出频率控制字 ); //音乐控制模块 music_ctrl i_music_ctrl( .sysclk(clk_valid), .start_key(start_key), .stop_key(stop_key), .tonecode(tonecode),//简谱 .tonestep(tonestep),//频率控制字 .spkout(spkout), .led(led) ); endmodule

完整代码

扫描文章末尾的公众号二维码

1192

1192

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?