名称:序列检测器及正弦波发生器设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

序列检测器及正弦波发生器

1、检测序列11010011,高位在前

2、设计正弦波发生器

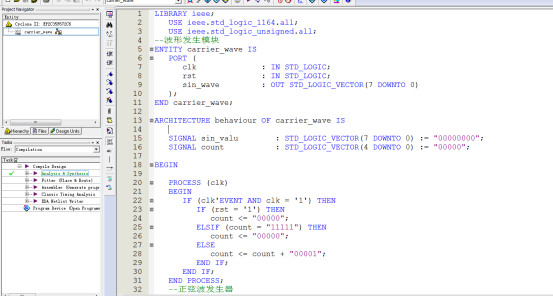

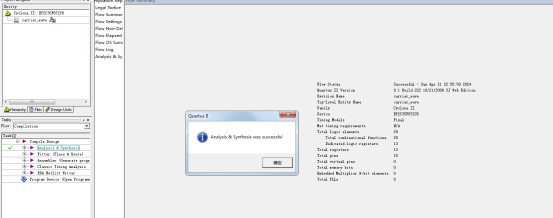

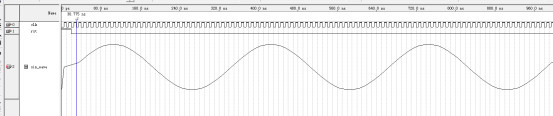

正弦波发生器

1、工程文件

2、程序文件

3、程序编译

4、仿真图

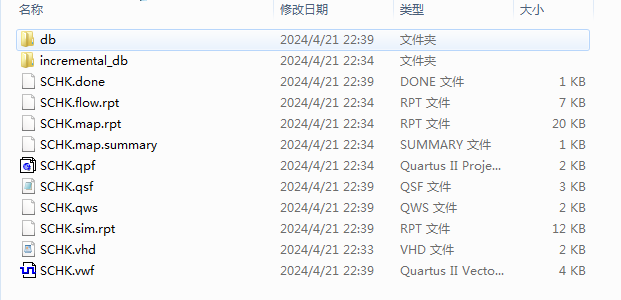

序列检测

1、工程文件

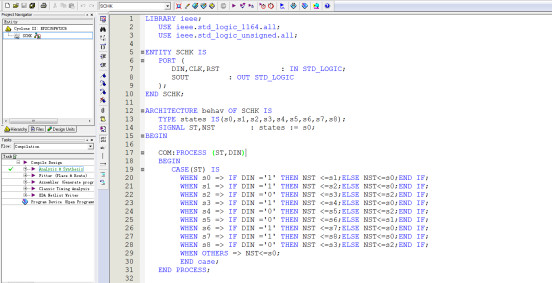

2、程序文件

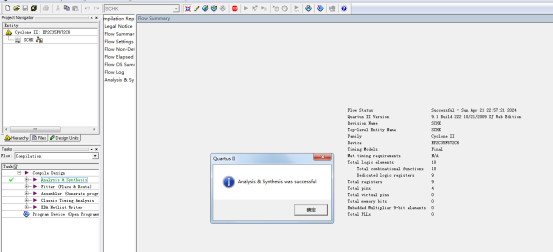

3、程序编译

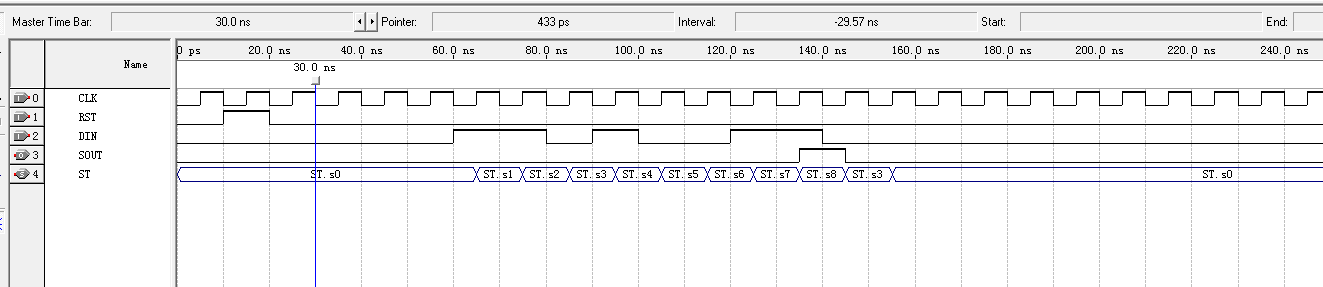

4、仿真图

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; ENTITY SCHK IS PORT ( DIN,CLK,RST : IN STD_LOGIC; SOUT : OUT STD_LOGIC ); END SCHK; ARCHITECTURE behav OF SCHK IS TYPE states IS(s0,s1,s2,s3,s4,s5,s6,s7,s8); SIGNAL ST,NST : states := s0; BEGIN COM:PROCESS (ST,DIN) BEGIN CASE(ST) IS WHEN s0 => IF DIN ='1' THEN NST <=s1;ELSE NST<=s0;END IF; WHEN s1 => IF DIN ='1' THEN NST <=s2;ELSE NST<=s0;END IF; WHEN s2 => IF DIN ='0' THEN NST <=s3;ELSE NST<=s2;END IF; WHEN s3 => IF DIN ='1' THEN NST <=s4;ELSE NST<=s0;END IF; WHEN s4 => IF DIN ='0' THEN NST <=s5;ELSE NST<=s2;END IF; WHEN s5 => IF DIN ='0' THEN NST <=s6;ELSE NST<=s1;END IF; WHEN s6 => IF DIN ='1' THEN NST <=s7;ELSE NST<=s0;END IF; WHEN s7 => IF DIN ='1' THEN NST <=s8;ELSE NST<=s0;END IF; WHEN s8 => IF DIN ='0' THEN NST <=s3;ELSE NST<=s2;END IF; WHEN OTHERS => NST<=s0; END case; END PROCESS;

源代码

点击下方的公众号卡片获取

749

749

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?