名称:4位加法器设计VHD代码ISE仿真(文末获取)

软件:ISE

语言:VHDL

代码功能:

4位加法器设计

1、熟悉ISE软件的使用

2,掌握FPGA设计的全过程。

3、熟练掌握元件例化语句、生成语句的描述方法

4、掌握组合逻辑电路的设计方法。

5、设计并实现一个4位加法器

6、掌握ISE软件中仿真测试文件编写及功能时序仿真操作流程。

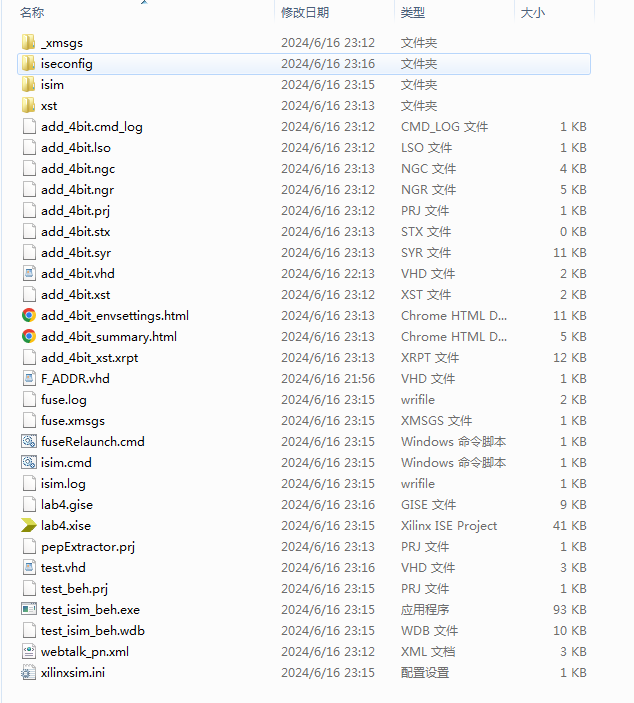

1. 工程文件

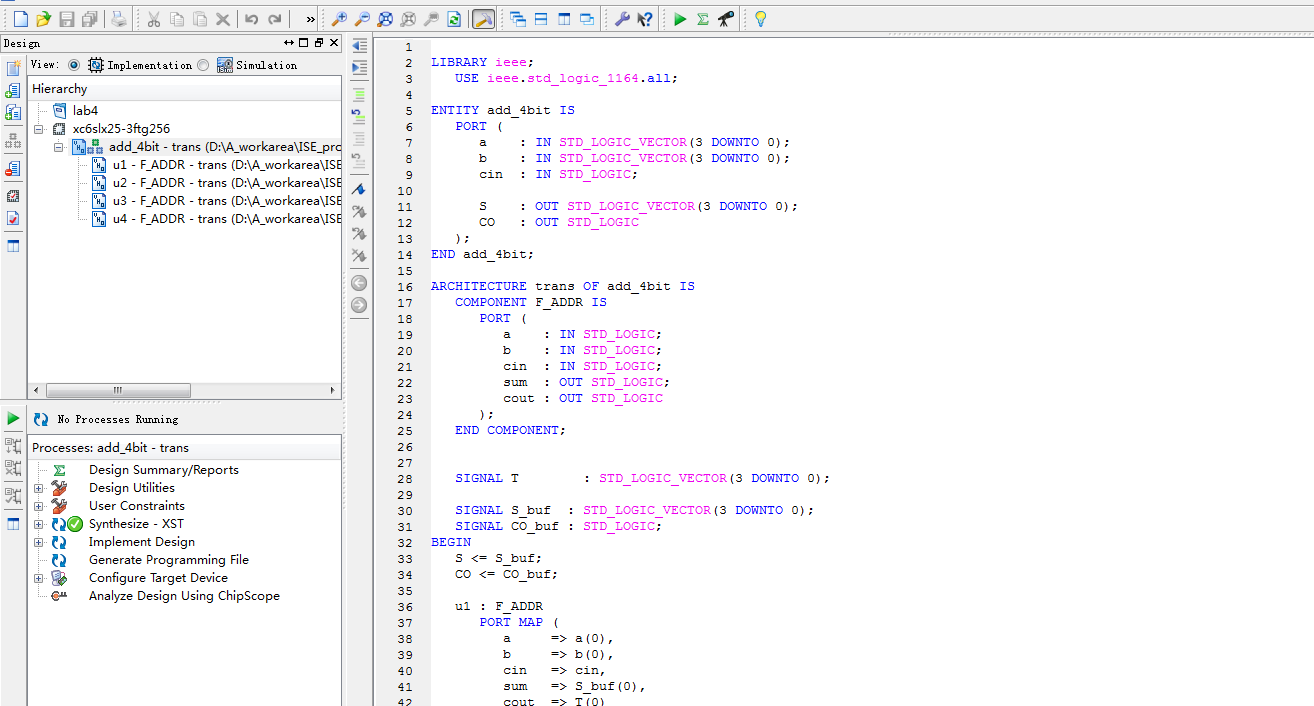

2. 程序文件

3. 程序编译

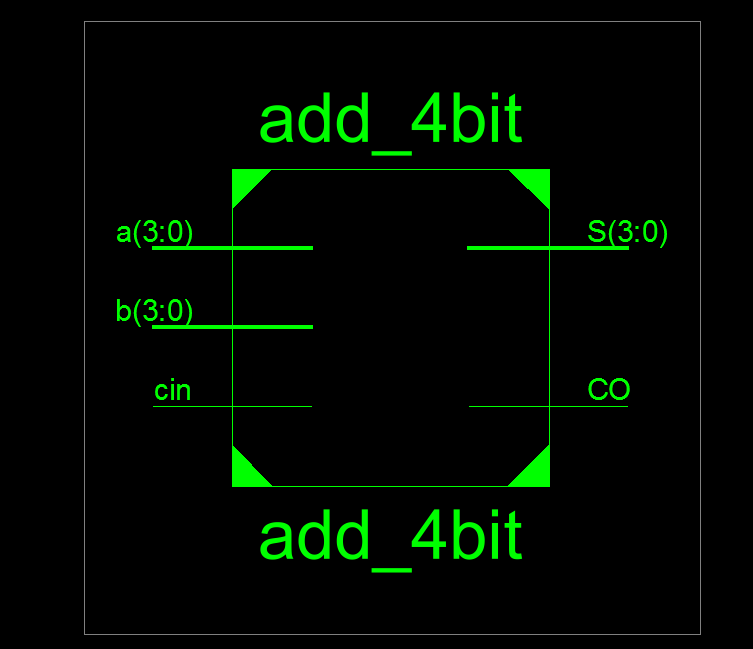

4. RTL图

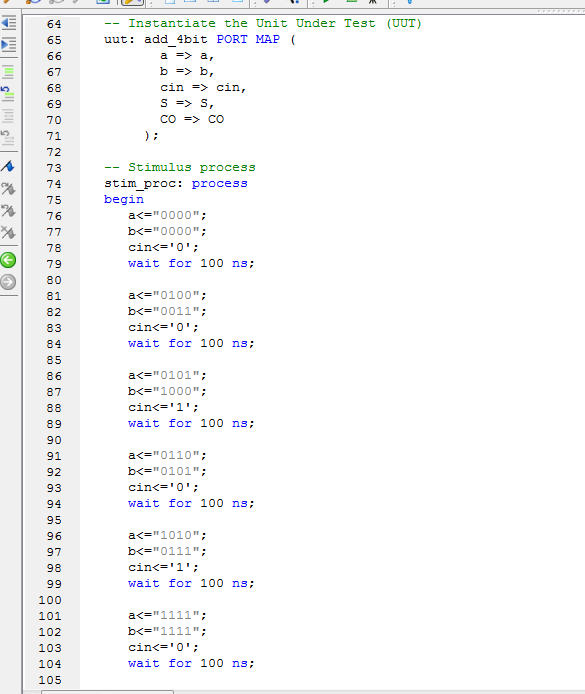

5. Testbench

6. 仿真图

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY add_4bit IS PORT ( a : IN STD_LOGIC_VECTOR(3 DOWNTO 0); b : IN STD_LOGIC_VECTOR(3 DOWNTO 0); cin : IN STD_LOGIC; S : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); CO : OUT STD_LOGIC ); END add_4bit; ARCHITECTURE trans OF add_4bit IS COMPONENT F_ADDR IS PORT ( a : IN STD_LOGIC; b : IN STD_LOGIC; cin : IN STD_LOGIC; sum : OUT STD_LOGIC; cout : OUT STD_LOGIC ); END COMPONENT; SIGNAL T : STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL S_buf : STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL CO_buf : STD_LOGIC; BEGIN S <= S_buf; CO <= CO_buf; u1 : F_ADDR PORT MAP ( a => a(0), b => b(0), cin => cin, sum => S_buf(0), cout => T(0) ); u2 : F_ADDR PORT MAP ( a => a(1), b => b(1), cin => T(0), sum => S_buf(1), cout => T(1) ); u3 : F_ADDR PORT MAP ( a => a(2), b => b(2), cin => T(1), sum => S_buf(2), cout => T(2) );

源代码

点击下方的公众号卡片获取

1900

1900

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?