一、创建一个包集合,里面包含自定义的record数据类型,然后用这个数据类型创建一个二维的存储器数组。

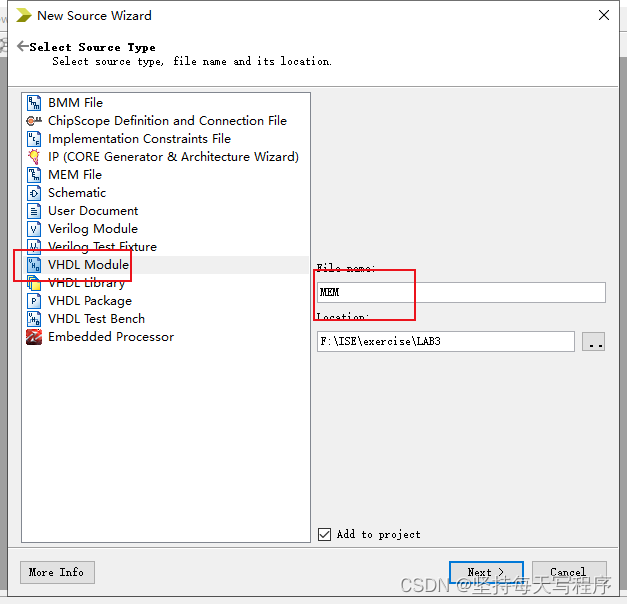

1.新建一个工程

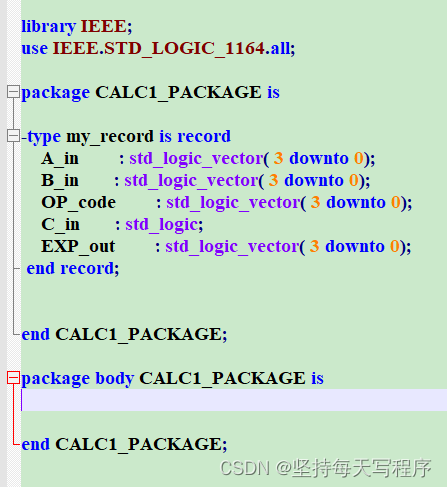

2.创建一个包含记录(record)数据类型的包集合

library IEEE;

use IEEE.STD_LOGIC_1164.all;

package CALC1_PACKAGE is

type my_record is record

A_in : std_logic_vector( 3 downto 0);

B_in : std_logic_vector( 3 downto 0);

OP_code : std_logic_vector( 3 downto 0);

C_in : std_logic;

EXP_out : std_logic_vector( 3 downto 0);

end record my_record;

end package CALC1_PACKAGE;

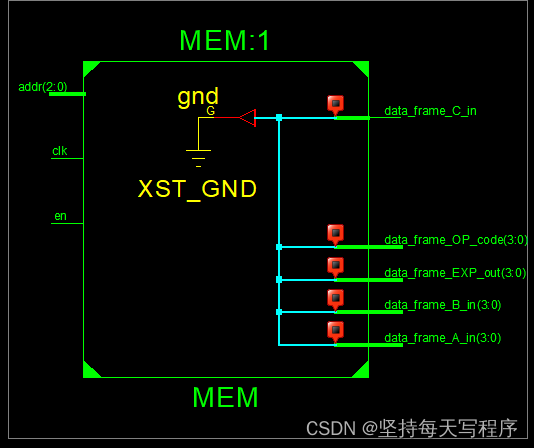

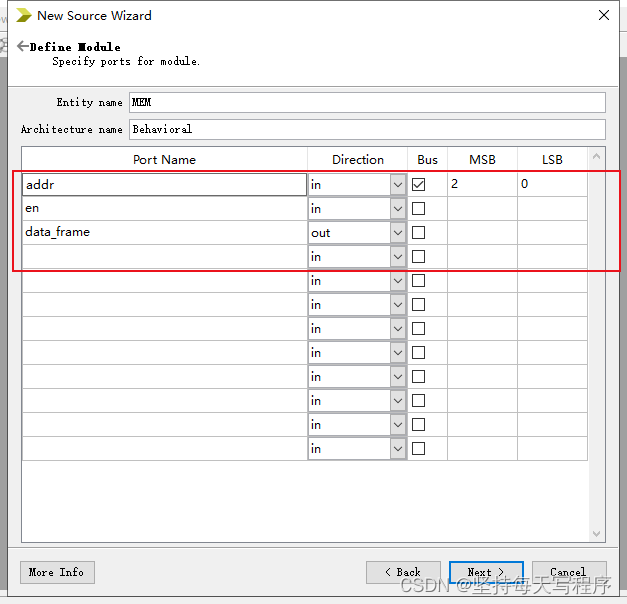

3.创建一个二维存储器数组

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

use WORK.CALC1_PACKAGE.all;

entity MEM is

Port ( addr : in STD_LOGIC_VECTOR (2 downto 0):="000";

en : in STD_LOGIC;

clk : in STD_LOGIC;

data_frame : out my_record);

end MEM;

architecture Behavioral of MEM is

type ROM_ARRAY is array (0 to 5) of my_record;

constant my_rom : ROM_ARRAY :=

(

0 => (A_in => "0000",B_in => "0000",OP_code => "0000",C_in => '0',EXP_out => "0000"),

1 => (A_in => "0000",B_in => "0000",OP_code => "0000",C_in => '0',EXP_out => "0000"),

2 => (A_in => "0000",B_in => "0000",OP_code => "0000",C_in => '0',EXP_out => "0000"),

3 => (A_in => "0000",B_in => "0000",OP_code => "0000",C_in => '0',EXP_out => "0000"),

4 => (A_in => "0000",B_in => "0000",OP_code => "0000",C_in => '0',EXP_out => "0000"),

5 => (A_in => "0000",B_in => "0000",OP_code => "0000",C_in => '0',EXP_out => "0000")

);

begin

process (clk)

begin

if(rising_edge(clk)) then

if(en = '1') then

data_frame <= my_rom(conv_integer(addr));

end if;

end if;

end process;

end Behavioral;

二、状态机计数模块:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

use WORK.calc1_package.all;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity fsm is

Port ( data_frame : in my_record;

clk : in STD_LOGIC;

rst : in STD_LOGIC;

a_in : out STD_LOGIC_VECTOR (3 downto 0);

b_in : out STD_LOGIC_VECTOR (3 downto 0);

c_in : out STD_LOGIC;

op_code : out STD_LOGIC_VECTOR (3 downto 0);

exp_out : out STD_LOGIC_VECTOR (3 downto 0);

addr : out STD_LOGIC_VECTOR (2 downto 0);

comp_en : out STD_LOGIC;

mem_en : out STD_LOGIC;

alu_en : out STD_LOGIC);

end fsm;

architecture Behavioral of fsm is

type state is (s0_prep,s1_fetch,s2_alu,s3_comp,s4_done); --5 states

signal curr_state,next_state : state;

signal addr_i,addr_q:STD_LOGIC_VECTOR (2 downto 0) ;

begin

addr <= addr_q;

P1:process(clk,rst) --state change

begin

if rst = '1' then

curr_state <= s0_prep;

addr_q <= (others => '0');

elsif rising_edge(clk) then

curr_state <= next_state;

addr_q <= addr_i;

end if;

end process;

P2:process(curr_state,data_frame,addr_q)

begin

a_in <= data_frame.a_in;

b_in <= data_frame.b_in;

c_in <= data_frame.c_in;

op_code <= data_frame.op_code;

exp_out <= data_frame.exp_out;

addr_i <= addr_q;

case curr_state is --state continue

when s0_prep =>

mem_en <= '0';

alu_en <= '0';

comp_en <= '0';

next_state <= s1_fetch;

when s1_fetch =>

mem_en <= '1';

alu_en <= '0';

comp_en <= '0';

next_state <= s2_alu;

when s2_alu =>

mem_en <= '0';

alu_en <= '1';

comp_en <= '0';

next_state <= s3_comp;

when s3_comp =>

mem_en <= '0';

alu_en <= '0';

comp_en <= '1';

next_state <= s4_done;

when s4_done => --addr_q++

if addr_q >= "101" then

next_state <= s4_done;

else

next_state <= s1_fetch;

addr_i <= addr_q+1;

end if;

mem_en <= '0';

alu_en <= '0';

comp_en <= '0';

when others =>

mem_en <= '0';

alu_en <= '0';

comp_en <= '0';

next_state <= s0_prep;

end case;

end process;

end Behavioral;

三、算术逻辑单元

----------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 14:32:39 08/14/2022

-- Design Name:

-- Module Name: alu - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity alu is

Port ( clk : in STD_LOGIC;

a_in : in STD_LOGIC_VECTOR (3 downto 0);

b_in : in STD_LOGIC_VECTOR (3 downto 0);

c_in : in STD_LOGIC;

op_code : in STD_LOGIC_VECTOR (3 downto 0);

alu_en : in STD_LOGIC;

alu_out : out STD_LOGIC_VECTOR (3 downto 0));

end alu;

architecture Behavioral of alu is

signal op_code_reg : STD_LOGIC_VECTOR (4 downto 0);

begin

op_code_reg <= op_code & c_in;

process(clk)

begin

if rising_edge(clk) then

if(alu_en = '1') then

case op_code_reg is

when "00000" => alu_out <= a_in;

when "00001" => alu_out <= a_in + 1;

when "00010" => alu_out <= a_in + b_in;

when "00011" => alu_out <= a_in + b_in + 1;

when "00100" => alu_out <= a_in + not b_in;

when "00101" => alu_out <= a_in + not b_in + 1;

when "00110" => alu_out <= a_in - 1;

when "00111" => alu_out <= a_in ;

when "01000" => alu_out <= a_in and b_in;

when "01010" => alu_out <= a_in or b_in;

when "01100" => alu_out <= a_in xor b_in;

when "01110" => alu_out <= not a_in;

when "10000" => alu_out <= (others => '0');

when others => alu_out <= (others => 'X');

end case;

end if;

end if;

end process;

end Behavioral;

四、比较器模块

----------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 15:04:20 08/14/2022

-- Design Name:

-- Module Name: comp - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity comp is

Port ( clk : in STD_LOGIC;

exp_out : in STD_LOGIC_VECTOR (3 downto 0);

alu_out : in STD_LOGIC_VECTOR (3 downto 0);

comp_en : in STD_LOGIC;

result : out STD_LOGIC);

end comp;

architecture Behavioral of comp is

begin

process(clk)

begin

if rising_edge(clk) then

if(comp_en = '1') then

if(exp_out = alu_out) then

result <= '1';

else

result <= '0';

end if;

end if;

end if;

end process;

end Behavioral;

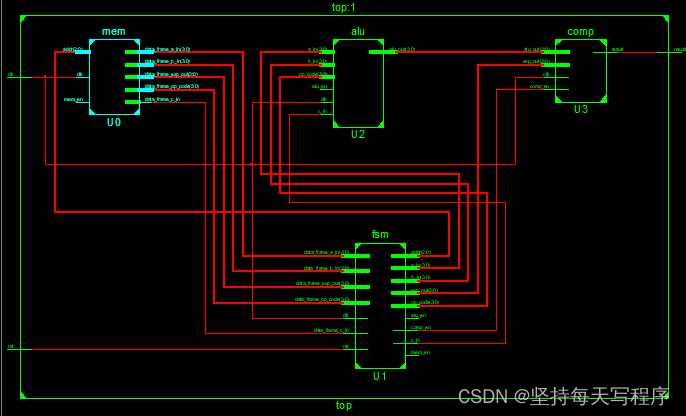

五、顶层模块:

----------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 15:04:20 08/14/2022

-- Design Name:

-- Module Name: comp - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity comp is

Port ( clk : in STD_LOGIC;

exp_out : in STD_LOGIC_VECTOR (3 downto 0);

alu_out : in STD_LOGIC_VECTOR (3 downto 0);

comp_en : in STD_LOGIC;

result : out STD_LOGIC);

end comp;

architecture Behavioral of comp is

begin

process(clk)

begin

if rising_edge(clk) then

if(comp_en = '1') then

if(exp_out = alu_out) then

result <= '1';

else

result <= '0';

end if;

end if;

end if;

end process;

end Behavioral;

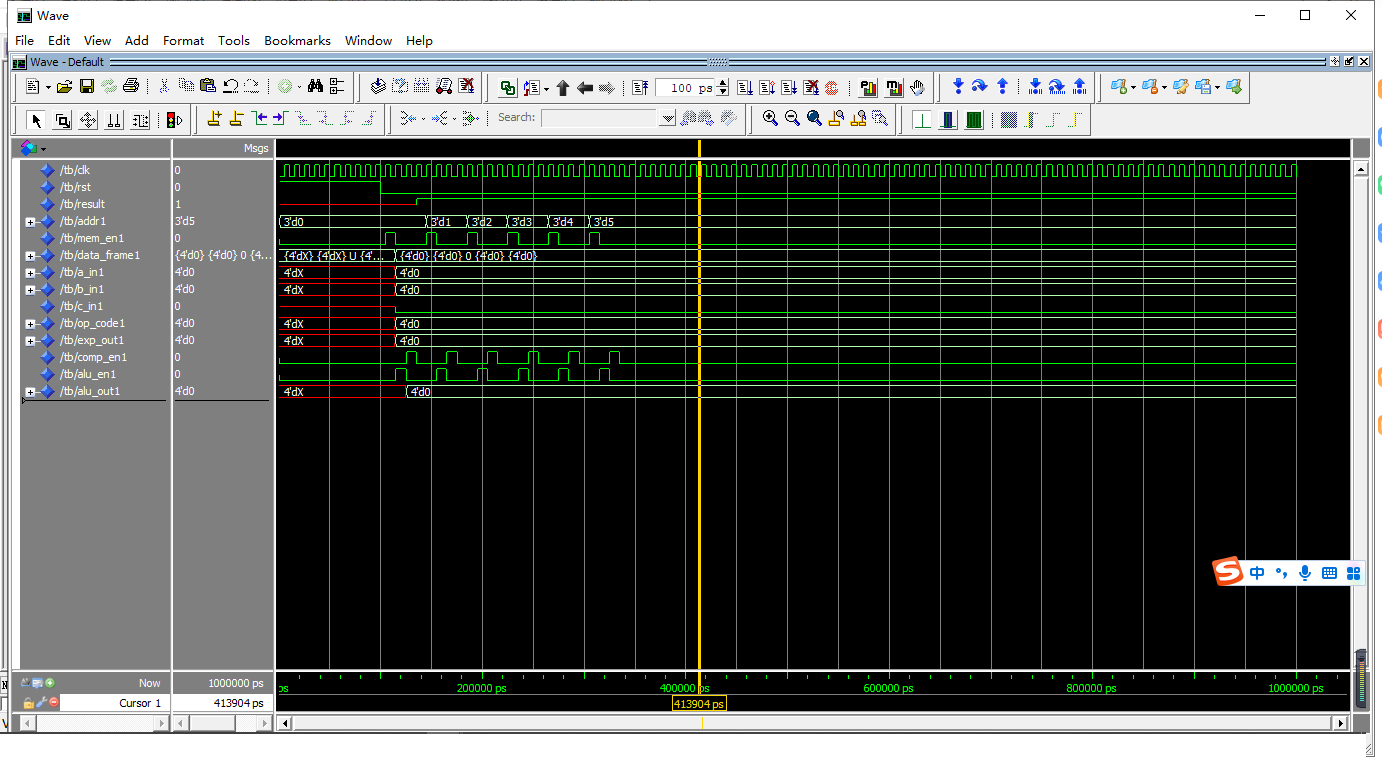

六、仿真模块:

--------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 16:49:21 08/14/2022

-- Design Name:

-- Module Name: F:/ISE/exercise/LAB3/tb.vhd

-- Project Name: LAB3

-- Target Device:

-- Tool versions:

-- Description:

--

-- VHDL Test Bench Created by ISE for module: top

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

-- Notes:

-- This testbench has been automatically generated using types std_logic and

-- std_logic_vector for the ports of the unit under test. Xilinx recommends

-- that these types always be used for the top-level I/O of a design in order

-- to guarantee that the testbench will bind correctly to the post-implementation

-- simulation model.

--------------------------------------------------------------------------------

LIBRARY ieee;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

use WORK.calc1_package.all;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--USE ieee.numeric_std.ALL;

ENTITY tb IS

END tb;

ARCHITECTURE behavior OF tb IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT top

PORT(

clk : IN std_logic;

rst : IN std_logic;

result : OUT std_logic

);

END COMPONENT;

component mem is

Port ( addr : in STD_LOGIC_VECTOR (2 downto 0);

mem_en : in STD_LOGIC;

clk : in STD_LOGIC;

data_frame : out my_record);

end component;

component fsm is

Port ( data_frame : in my_record;

clk : in STD_LOGIC;

rst : in STD_LOGIC;

a_in : out STD_LOGIC_VECTOR (3 downto 0);

b_in : out STD_LOGIC_VECTOR (3 downto 0);

c_in : out STD_LOGIC;

op_code : out STD_LOGIC_VECTOR (3 downto 0);

exp_out : out STD_LOGIC_VECTOR (3 downto 0);

addr : out STD_LOGIC_VECTOR (2 downto 0);

comp_en : out STD_LOGIC;

mem_en : out STD_LOGIC;

alu_en : out STD_LOGIC);

end component;

component alu is

Port ( clk : in STD_LOGIC;

a_in : in STD_LOGIC_VECTOR (3 downto 0);

b_in : in STD_LOGIC_VECTOR (3 downto 0);

c_in : in STD_LOGIC;

op_code : in STD_LOGIC_VECTOR (3 downto 0);

alu_en : in STD_LOGIC;

alu_out : out STD_LOGIC_VECTOR (3 downto 0));

end component;

component comp is

Port ( clk : in STD_LOGIC;

exp_out : in STD_LOGIC_VECTOR (3 downto 0);

alu_out : in STD_LOGIC_VECTOR (3 downto 0);

comp_en : in STD_LOGIC;

result : out STD_LOGIC);

end component;

--Inputs

signal clk : std_logic := '0';

signal rst : std_logic := '1';

--Outputs

signal result : std_logic;

signal addr1 : STD_LOGIC_VECTOR (2 downto 0);

signal mem_en1 : STD_LOGIC;

-- signal clk1 : STD_LOGIC;

signal data_frame1 : my_record;

-- signal rst1 : STD_LOGIC;

signal a_in1 : STD_LOGIC_VECTOR (3 downto 0);

signal b_in1 : STD_LOGIC_VECTOR (3 downto 0);

signal c_in1 : STD_LOGIC;

signal op_code1 : STD_LOGIC_VECTOR (3 downto 0);

signal exp_out1 : STD_LOGIC_VECTOR (3 downto 0);

signal comp_en1 : STD_LOGIC;

signal alu_en1 : STD_LOGIC;

signal alu_out1 : STD_LOGIC_VECTOR (3 downto 0);

-- Clock period definitions

constant clk_period : time := 10 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: top PORT MAP (

clk => clk,

rst => rst,

result => result

);

U0: mem port map (addr =>addr1,mem_en=>mem_en1,clk=>clk,data_frame=>data_frame1);

U1: fsm port map (data_frame=>data_frame1,clk=>clk,rst=>rst,a_in=>a_in1,

b_in=>b_in1,c_in=>c_in1,op_code=>op_code1,exp_out=>exp_out1,

addr=>addr1,comp_en=>comp_en1,mem_en=>mem_en1,alu_en=>alu_en1);

U2: alu port map (clk=>clk,a_in=>a_in1,b_in=>b_in1,c_in=>c_in1,op_code=>op_code1,alu_en=>alu_en1,alu_out=>alu_out1);

U3: comp port map (clk=>clk,exp_out=>exp_out1,alu_out=>alu_out1,comp_en=>comp_en1,result=>result);

-- Clock process definitions

clk_process :process

begin

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

end process;

-- Stimulus process

stim_proc: process

begin

-- hold reset state for 100 ns.

rst <= '1';

wait for 100 ns;

rst <= '0';

-- wait for clk_period*10;

-- insert stimulus here

wait;

end process;

END;

2183

2183

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?