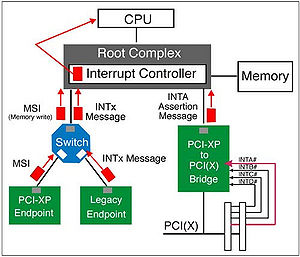

之所以可以实现如此的msi中的message,是因为pcie不仅仅是一条总线,而是一套协议,它是串行的,而非传统总线的并行形式,串行总线最适合定义协议了,然而不管怎样,cpu引脚以及其局部总线(前端总线)是并行的,因此针对于pcie,有一个称为root complex的家伙负责并串转换。由于pcie实现复杂的协议,因此它的一个端点可以往root complex发送一个消息,root complex接收到一个msi时,它会将这个message转换,依然向cpu的intr引脚发送一个高电平,然后cpu的inta引脚拉低的时候root complex将msi中取出的中断号取出来发送到数据总线上,也就是说,root complex代替pcie总线上连接的设备发送了intr高电平给cpu,然后代替各个设备发送了中断号给cpu处理,因此就解除了cpu和各个设备之间的耦合,只要root complex这个二传手负责二者的交互即可。

在传统的pci中断体系中,每一个pci总线上的设备被分配一个特定的中断号,然后当设备需要中断cpu时,设备直接发出int信号,然后在cpu的inta引脚拉低的时候将自己的中断号放在数据总线上,一切都要设备自己负责,这一切的缘由一部分就是因为pci的并行性,实现事务很复杂,而pcie是串行的,很容易定义协议包,因此很容易就实现了由root complex代理中断的功能,因此设备也就可以动态的分配独占的中断号了,因为中断号的分配完全是软件解决的,而不再像传统pci那样是硬件解决的了,软件的最大特点就是其灵活性,因此pcie更适合大量设备的环境,中断处理程序再也不需要大量遍历共享中断号的设备来确定中断源了。

联想一下以太网,或者ip网,它们的成功不是硬件的复杂性和高效性,而是不失高效性下的灵活性,这些体系或者机制的共同点就是它们的总线都是串行的,串行的总线可以方便的实现协议,而不用考虑并行同步的问题,这些协议是基于握手的,因此这些协议比硬件硬连线实现的机制更加灵活,如果采用硬连线并行机制,我们除了得到了短距离的快速传输外,几乎无法传输任何控制信息,还需要另外的控制总线和相关的时序,这就增加了芯片引脚的数量和集成电路设备的复杂性,因此串行线路在更高层次上是比并行线路更具有优势的,并行线路需要额外的控制电路时序来提供约束,而串行线路只需要协议包本身就可以提供约束。

附:一张可以体现pcie的图

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?