前言:

很多人都听说过CDC,也对CDC都有了很多的了解,但是对于RDC可能许多新人都没有接触过,作者也是工作两年后才接触到这个领域,这个领域其实在工业界是近十年才被重视起来的,而不像CDC大家已经有了充足的经验了。

分析:

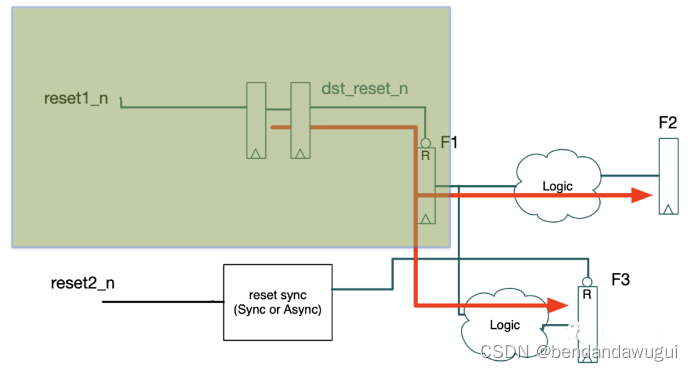

我们知道很多数字模块中都用到了Asynchronous Reset,那么用Asynchronous Reset有什么问题呢?别的缺点作者在Reset同步里面讲了,但是没有讲RDC的问题,下面我们先看一个例子。

在上面这幅图中,我们有2个reset,分别是reset1_n和reset2_n,其中flop F1是被reset1_n给异步reset的,而F3是被reset2_n给异步reset的,F2可能是被同步reset给复位,也可能没有reset,而这其中,F1和F2和F3的控制逻辑的fan-in,也就是说F1的变化会影响到F2和F3的值。

那么考虑这种情况,reset1_n assert了,但是reset2_n并没有assert,F3和F2依然工作在正常模式,并没有被复位,那么会发生什么情况呢?结果可能很糟糕,即F2和F3会产生metastability,导致芯片发生逻辑错误,你可能会说,不对啊,这里又没有跨时钟域,哪里来的metastability?注意看,因为reset1_n对F1是异步reset,也就是说,当reset1_n assert,F1立马会被reset,F1的Q立刻会发生变化,而我们说,asynchronous reset的assertion是可以在任何时间的,不然就不叫asynchronous了,它和时钟沿没有关系,甚至与有没有时钟都没有关系,换句话说,【F1的Q变成reset值可以发生在任何时候! 那么F2和F3的D输入经过那一堆组合逻辑,就可能在任何时候产生变化,如果这个变化恰好落在F2和F3的setup/hold window里,那不就导致了setup/hold time violation,从而导致亚稳态了吗?】

你可能还是有些将信将疑,难道F1的Q和F3的D,F1的Q和F2的Q之间不是有STA来做timing check吗?在timing 都满足的情况下怎么还会有setup/hold timing violation呢?你没有说错,如果F1,F2,F3确实都处在同一个时钟域,STA确实会做register to register的timing closure,但是注意,STA能够做的,是分析F1的Tclk2q再加上Tcombo是不是满足register to register的setup/hold,STA是无法做reset to q再加上Tcombo的check的,还是哪个原因,asynchronous reset的assertion是可以任何时间来的,所以没有办法做STA。(注意,reset de-assertion的和时钟沿对齐的,所以reset de-assertion是会做STA的),也就是说,图上红色的timing path其实是unconstrained。

好,我们再来总结一下这里例子,这里我们至少有了两个reset demain,其中reset domain 1就是包含所有被reset1_n所复位的flop,而reset domain2是包含被reset2_n复位的flop,如果这两个reset domain的flop在function mode的时候存在逻辑关系,而reset1_n可以单独assert,那就可能在reset domain2产生metasable。

注意,这里产生reset domain crossing issue的条件有:

1:必须是asynchronous reset assertion。因为synchronous reset的话,无论assertion还是de-assertion其实都是被STA check的。

2:存在不被这个asynchronous reset给控制的flop,如果你告诉我其实reset2_n在reset1_n assert的时候也assert了,那么其实也不会有问题。

这一类问题随着SoC越来越复杂,集成度越来越高,IP reuse也越来越多而越发变得常见,并且变得越来越重要,你可能会问,什么情况下reset1_n assert,但是reset2_n不assert呢?举个例子,如果reset1_n的部分要被power gating了,或者被soft reset了,而reset2_n的domain依然工作,那么就会出现这种情况,产生RDC最根本的原因,其实就是因为asynchronous reset assertion的路径无法被STA给约束到。

下面还有两个常见的例子:

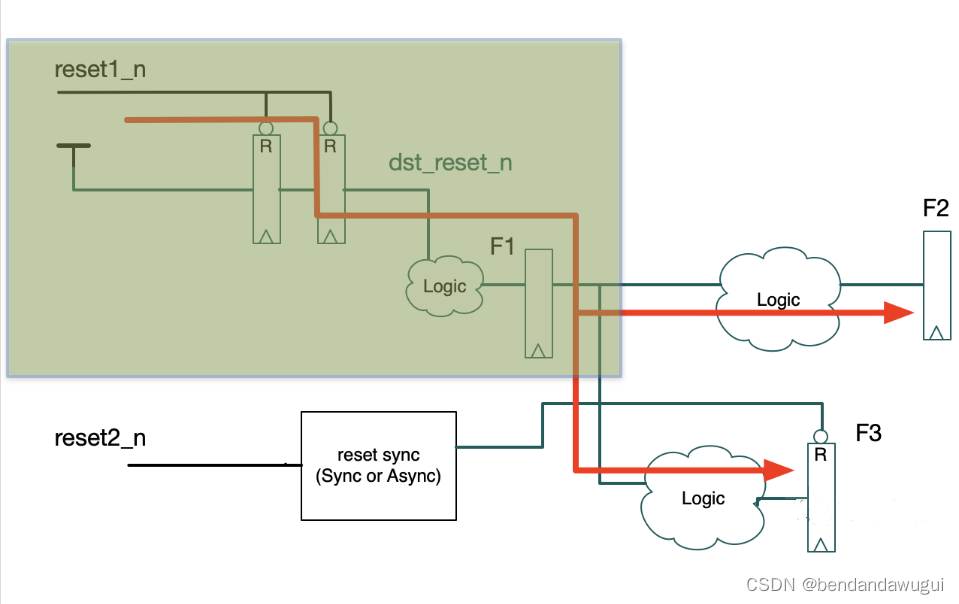

例1:

在这个例子中,reset1_n虽然经过了一个double flop的reset synchronizer,但是对于F1来说还是asynchronous reset,红色的path依然不会被STA给约束。

例2:

在这个例子中,F1没有asynchronous reset pin,并不是被直接asynchronous reset,但是dst_reset_n在assert的时候是作为D的逻辑,导致了F1本身可能就产生了metastable,进而继续影响下游的F2和F3,同样的,红线的path没有被STA给约束。

解决办法:

那么我们已经知道了RDC产生的原因,我们要怎么解决呢?

首先,最简单粗暴的思路就是,能不用asynchronous reset就不用。

因为synchronous reset无论是assertion还是de-assertion都会被STA约束,所以你可以放心,不会产生setup/hold的问题。

但是你可能会说,没法不用asynchronous reset啊,比如说我想在没有时钟的时候reset电路,我非得用asynchronous reset不可,或者说你拿到的是一个别人或者买来的IP,IP本身就用asynchronous reset了,你也没办法不用,那怎么办呢?

首先,如果这个是你自己的设计,那你就得多加小心。

1:在同一个时钟域内,不要混用asynchronous reset 和 synchronous reset。

2:用asynchronous reset 的时候,问自己一个问题:后级的logic也会被这个asynchronous reset给reset掉吗?

如果确认RDC path不可避免,那么我们来看可以怎么来修复。

思路1:

最常见的办法就是加clamp,看看下面的例子:

在F1的Q端加一个AND门,被一个rst_clamp给控制住,这个信号必须要在reset1_n assert之前先active,这样可以先一步将与门的输出控制在0(你也可以clamp在1,取决于后面的要求),这样做的好处就是,当F1被asynchronous reset的时候,F1的Q变化不会产生metastable,这是最常见的解决思路,难点就是要找出所有的F1,加上适当的clamp,而且还要设计恰当的rst_clamp信号,而且要加的clamp cell可能很多,漏了一个可能都会有问题,当然现在已经有了RDC检查的EDA工具,如果你漏了应该能够帮你找出来。

思路2:

另外一个思路是不加clamp cell,而是在asynchronous reset assertion之前将F2和F3的clock给停住,这样 既然F2和F3都没有clock,那自然不会有setup/hold的问题,当然,这种办法的缺点就是可能F2和F3的clock不能停,还是要工作在function mode,如果有这样的要求的话就不能这样修复了。

思路3:

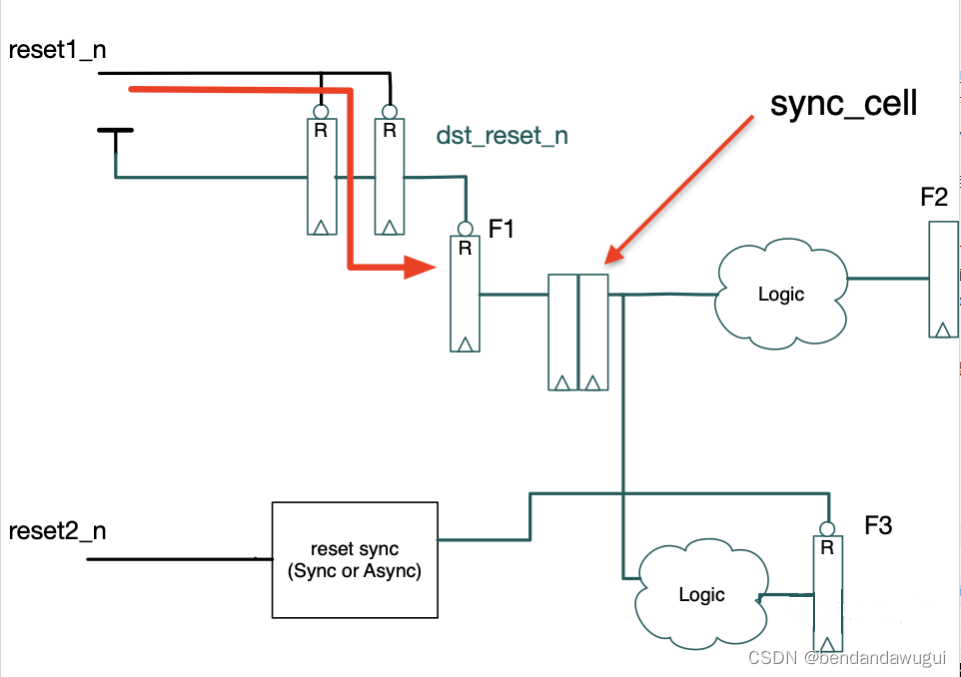

还有一个思路,借鉴CDC中的办法,即给F1的输出加synchronizer,如下图所示:

这样F3和F2的输入也都不会产生setup/hold violation,但是这样做的缺点也很明显:

第一,和clamp cell一样,要找到美也给crossing 的flop,然后加synchronizer,面积消耗比一个AND门要大得多;

第二:加了synchronizer会导致F1的值会被延迟两派之后才给到F2和F3,这种修复办法只有在确保加入synchronizer不会使得逻辑关系错误的情况下才能使用。

思路4:

保证复位顺序,如果能保证后级先复位,然后再复位前级,那也没有问题。

好了,这就是RDC的一个初步介绍,更多详细介绍大家在工作种可以参考EDA工具的手册,并且在工作中的实际问题种学习,增加经验。

306

306

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?