前段时间刚刚结束了芯片的RDC工作,打算做个即时总结,文中的复位信号都是低电平有效,文中假设所有的复位信号都是从异步复位同步释放电路处理过的,所以传统的复位信号释放导致的亚稳态并不存在,这里讨论的都是reset assertion时刻带来的亚稳态风险及解决方案。

1.什么是RDC?

在芯片设计中,RDC是reset domain crossing 的缩写,类似于CDC(clock domain crossing), 由于现在SOC芯片是有很多ECUs组成,为了使整个系统能够快速从复位中恢复, 用户希望SOC里面每个ECU模块都可以有自己独立的异步复位信号,这样可以出问题的时候只复位有错误逻辑的模块,而其它模块保持正常工作。

由于各个ECU的异步复位信号不一样,信号在他们之间传输就会出现RDC的问题,即信号从一个复位域被打拍或传输到另一个复位域,可能会带来亚稳态风险。

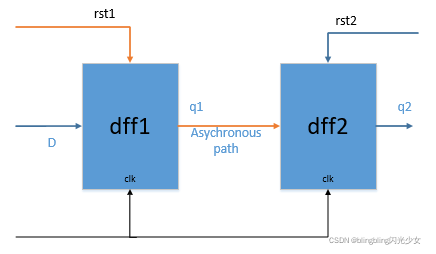

图1:RDC 图示

2.RDC中存在的亚稳态风险

如图1,当信号从rst1复位域跨到rst2复位域时,如果rst1置低位复位的时刻恰好在时钟上升沿附近,那q2输出信号可能会出现亚稳态风险,因为异步复位信号rst1置低位的那个时刻,q1被立刻拉低,因为rst1在时钟上升沿附近被拉低,也就是说q1在时钟上升沿附近发生信号变化,对于dff2来说,可能会出现建立时间或者保持时间不满足导致q1信号不能被准确sample, 从而导致q2信号

本文介绍了RDC(reset domain crossing)在芯片设计中的亚稳态风险,并提出了两种解决方案:reset assertion order和隔离法,包括数据隔离和时钟隔离,以确保信号在不同复位域间的稳定传输。

本文介绍了RDC(reset domain crossing)在芯片设计中的亚稳态风险,并提出了两种解决方案:reset assertion order和隔离法,包括数据隔离和时钟隔离,以确保信号在不同复位域间的稳定传输。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1078

1078

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?